该LMK05028是一款高性能网络同步器时钟器件,可提供抖动清除、时钟生成、高级时钟监控和良好的无中断开关性能,以满足通信基础设施和工业应用的严格时序要求。该器件的低抖动和高PSNR降低了高速串行链路中的误码率(BER)。

该器件具有两个PLL通道,可产生多达8个输出时钟,抖动为150 fs RMS。每个PLL域可以从任意四个基准输入中进行选择,以同步输出。

*附件:lmk05028.pdf

特性

- 两个独立的 PLL 通道具有以下特点:

- 抖动:100MHz 输出时 150fs RMS ≥

- 相位噪声:122.88MHz时100Hz偏移时为–112dBc/Hz

- 无中断开关:50ps 相位瞬态,带相位消除

- 带 Fastlock 的可编程环路带宽

- 使用低成本 TCXO/OCXO 实现符合标准的同步和保持

- 任何输入到任何输出频率转换

- 四个基准时钟输入

- 基于优先级的输入选择

- 失去参考的数字滞留

- 8个时钟输出,带可编程驱动器

- 多达六种不同的输出频率

- AC-LVDS、AC-CML、AC-LVPECL、HCSL 和 1.8V 或 2.5V LVCMOS 输出格式

- EEPROM/ROM用于上电时自定义时钟

- 灵活的配置选项

- 出色的电源噪声抑制 (PSNR)

- 3.3V电源,1.8V、2.5V或3.3V输出

- 工业温度范围:–40°C 至 +85°C

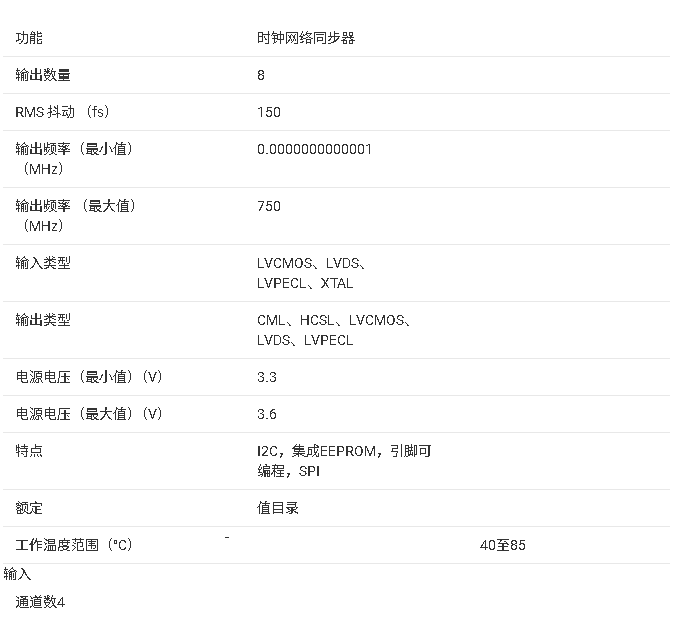

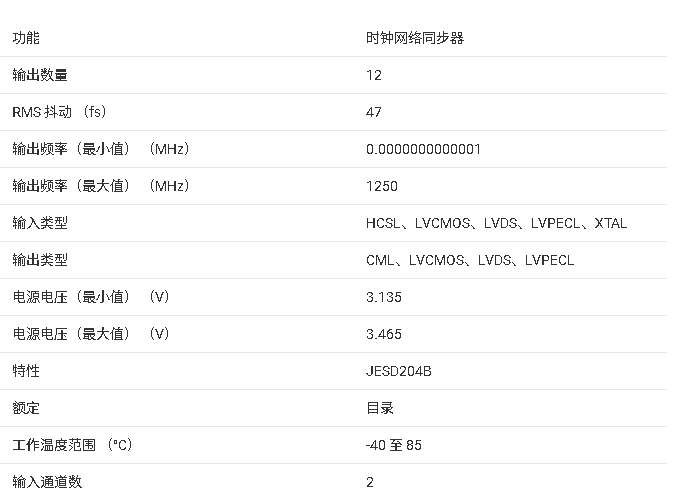

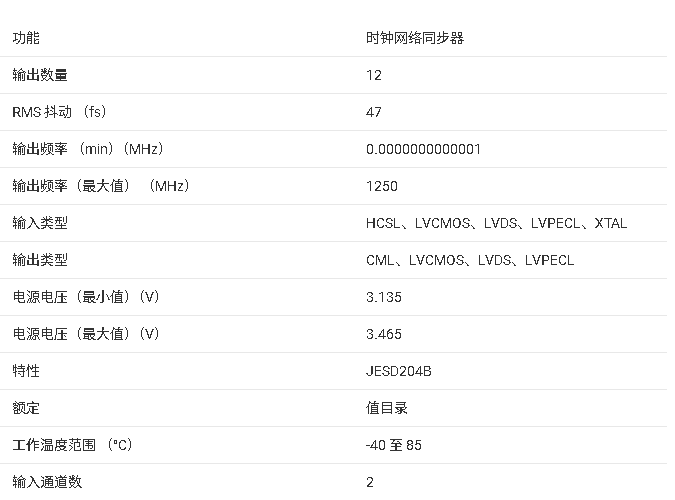

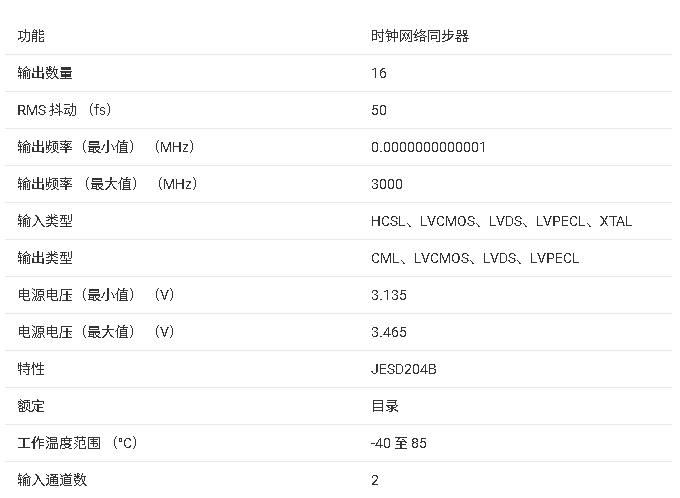

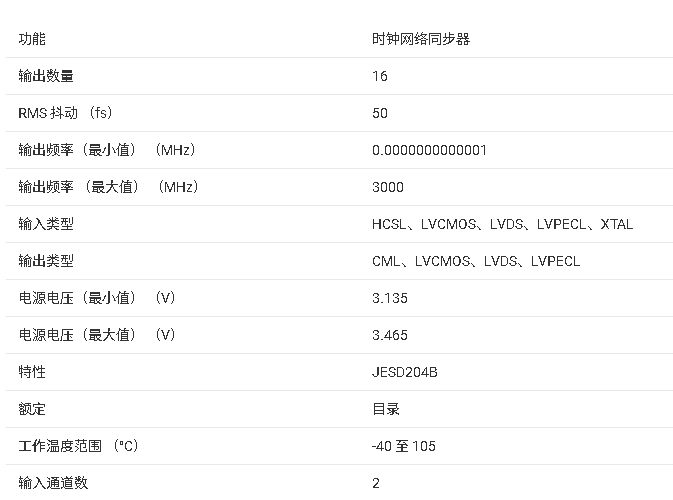

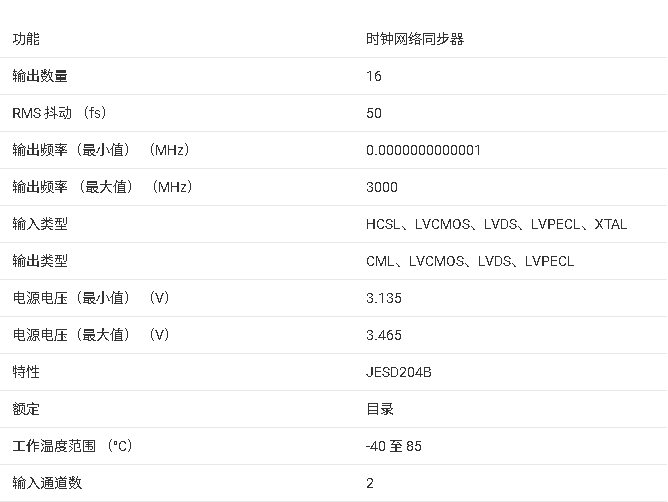

参数

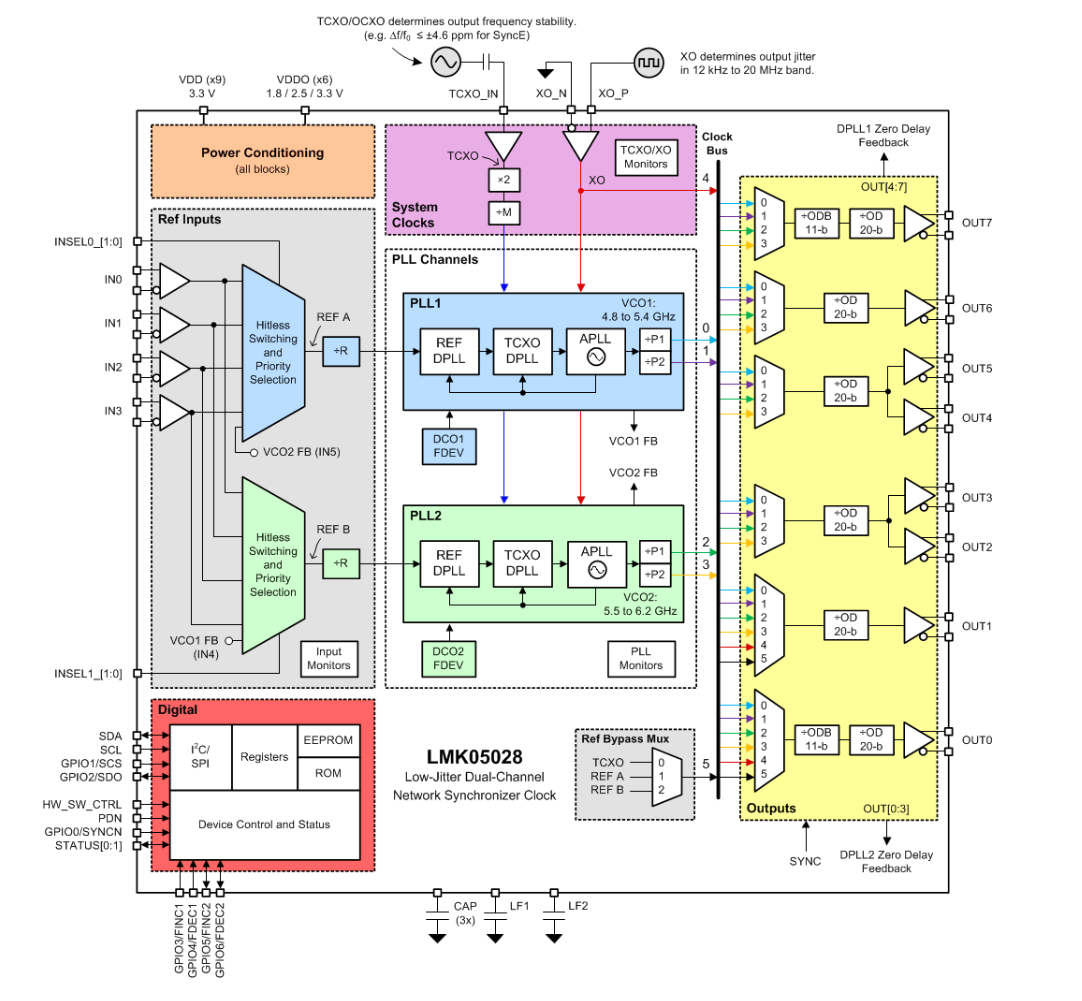

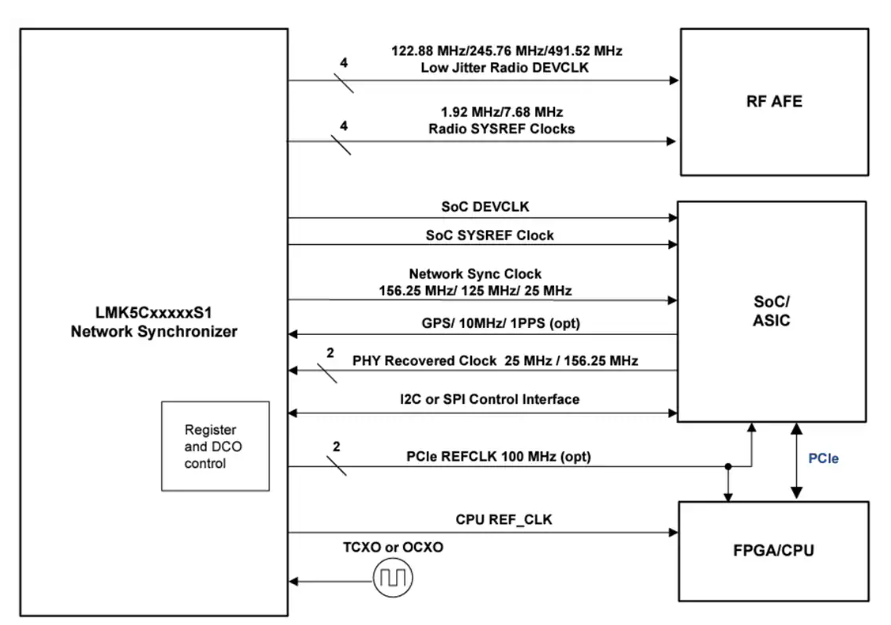

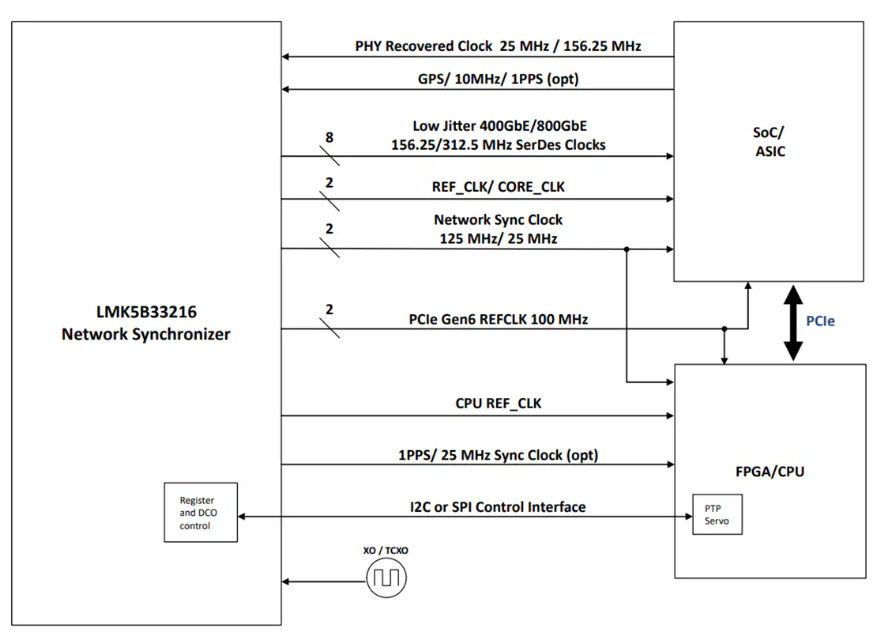

方框图

?1. 产品概述?

LMK05028是德州仪器(TI)推出的高性能网络同步器时钟芯片,具备双独立PLL通道、8路可编程时钟输出,支持150fs RMS超低抖动,适用于通信基础设施和工业应用。关键特性包括:

- ?双PLL架构?:支持3-loop/2-loop模式,集成数字PLL(DPLL)和模拟PLL(APLL),带宽可编程(0.01Hz–4kHz)。

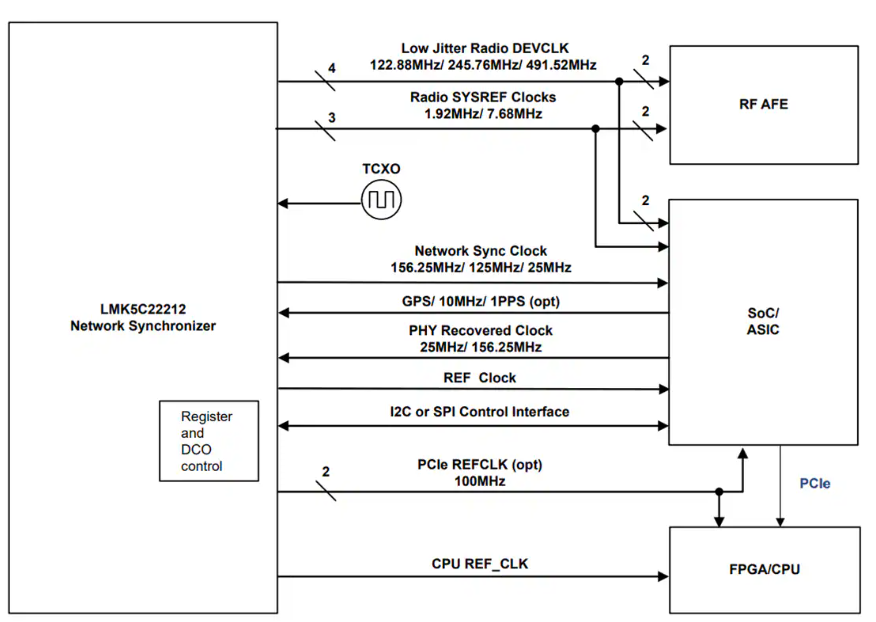

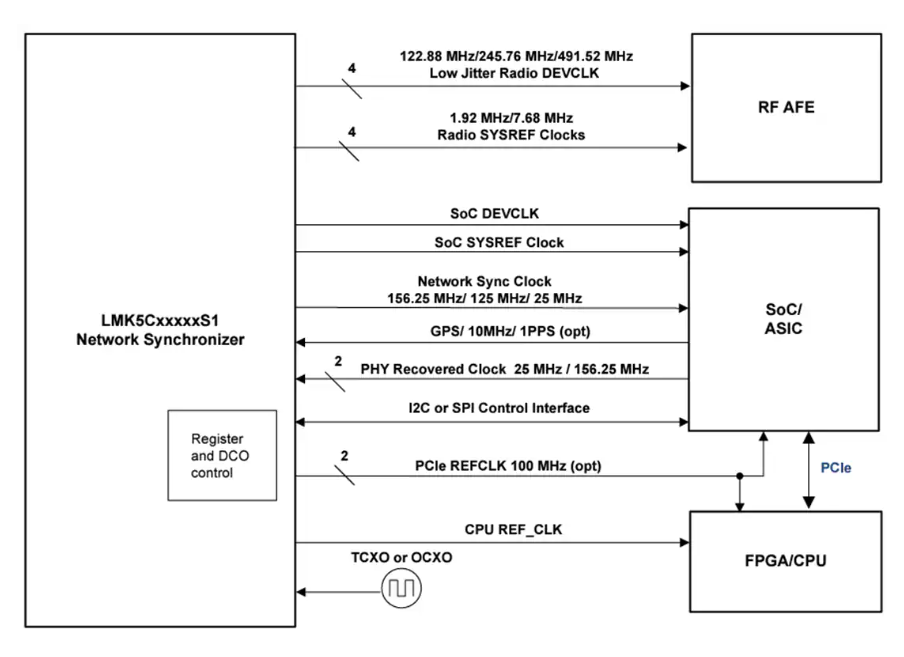

- ?输入灵活性?:4路参考时钟输入(支持差分/LVCMOS)、XO(10–100MHz)和TCXO(10–54MHz)输入。

- ?输出配置?:8路输出,支持AC-LVDS/CML/LVPECL、HCSL及1.8V/2.5V LVCMOS驱动,频率最高750MHz。

- ?高级功能?:Hitless切换(50ps相位瞬变)、数字保持模式(Holdover)、DCO模式(<1ppt/步进精度)、零延迟模式(ZDM)。

?2. 核心功能?

- ?时钟同步与清洁?:通过DPLL实现参考时钟的抖动衰减和频率合成,APLL提供低噪声VCO(4.8–6.2GHz)。

- ?输入监控?:集成幅度、频率、缺失脉冲检测,支持自动/手动输入切换。

- ?输出管理?:支持输出同步(SYNC)、多路分频(20位分频器),可配置静音和驱动类型。

?3. 应用场景?

- ?通信网络?:SyncE(G.8262)、SONET/SDH(Stratum 3/3E)、IEEE 1588 PTP从时钟。

- ?数据中心?:线卡、定时卡、FPGA/ASIC时钟生成。

- ?工业与医疗?:测试仪器、医学成像设备。

?4. 配置与编程?

- ?接口支持?:I2C/SPI接口,内置EEPROM/ROM存储配置,支持上电自定义初始化。

- ?设计工具?:TICS Pro软件辅助频率规划和寄存器配置生成。

?5. 电气与封装?

- ?电源?:3.3V核心供电,1.8V/2.5V/3.3V输出供电,工业温度范围(-40°C至+85°C)。

- ?封装?:64引脚VQFN(9mm×9mm),带裸露焊盘增强散热。

?6. 关键性能指标?

- 相位噪声:-112dBc/Hz @100Hz偏移(122.88MHz输出)。

- 电源噪声抑制(PSNR):<-70dBc(50mVpp噪声)。

- 启动时间:<20ms(含VCO校准)。

该芯片通过高集成度和灵活配置,满足严苛的时序要求,降低系统复杂性和BOM成本。

-

pll

+关注

关注

6文章

904浏览量

136883 -

时钟芯片

+关注

关注

2文章

277浏览量

41220 -

时钟器件

+关注

关注

0文章

13浏览量

8145 -

网络同步器

+关注

关注

0文章

24浏览量

1702

发布评论请先 登录

采用JESD204B的LMK5C33216超低抖动时钟同步器数据表

LMK5B12204具有两个频域的超低抖动网络同步器时钟数据表

LMK05318具有两个频域的超低抖动网络同步器时钟数据表

?LMK05028 低抖动双通道网络同步器时钟芯片总结

?LMK05028 低抖动双通道网络同步器时钟芯片总结

评论