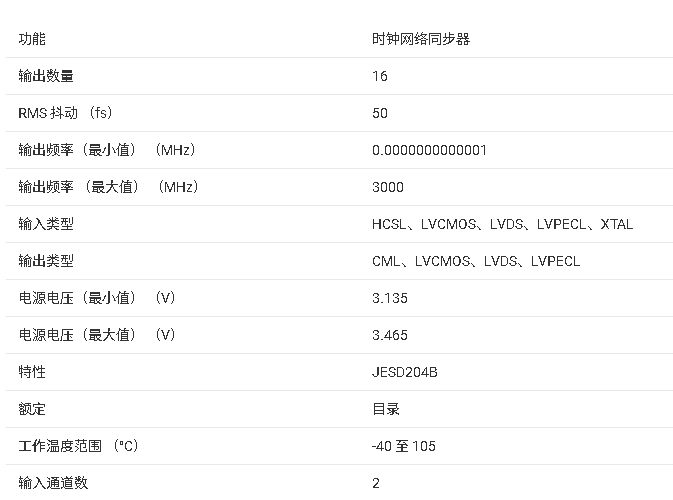

Texas Instruments LMK5B33216网络同步器和抖动清除器设计用于满足基于以太网的网络应用的严格要求,计时精度 < 5ns(D类)。该网络同步器集成了三个DPLL,可提供无中断切换。它还具有抖动衰减、可编程环路带宽和无外部环路滤波器。该特性可最大限度地提高灵活性和易用性。每个DPLL相位将配对的APLL锁定到参考输入。APLL3采用TI专有的体声波 (BAW) 技术,具有超高性能PLL。无论DPLL基准输入频率和抖动特性如何,均可生成312.5MHz输出时钟,RMS抖动为42fs(典型值)/60fs(最大值)。APLL2和APLL1提供了用于第二或第三频率和/或同步域的选项。

数据手册:*附件:Texas Instruments LMK5B33216网络同步器和抖动清除器数据手册.pdf

参考验证电路监视DPLL参考时钟,并在检测到切换事件时在它们之间执行无中断切换。可以启用零延迟和相位构建,以控制从输入到输出的相位关系。该器件可通过I^2^C或SPI接口完全编程。板载EEPROM可用于定制系统启动时钟。Texas Instruments LMK5B33216还具有出厂默认ROM配置文件作为回退选项。

特性

- 超低抖动BAW基于VCO的以太网时钟

- RMS抖动:42fs典型值/60fs最大值(312.5MHz时)

- RMS抖动:47fs典型值/65fs最大值(156.25MHz时)

- 三个高性能数字锁相环 (DPLL),带配对模拟锁相环 (APLL)

- 可编程DPLL环路带宽:1mHz到4kHz

- DCO频率调整步长:<1ppt

- 2个差分或单端DPLL输入

- 输入频率范围:1Hz (1PPS) 至800MHz

- 数字保持和无中断切换

- 16个差分输出,具有可编程HDS/LVPECL、LVDS和HSCL输出格式

- 配置6个LVCMOS频率输出时,多达20个总频率输出

- 输出频率:1Hz (1PPS) 至1250MHz,带可编程摆幅和共模

- 符合PCIe Gen 1至6标准

- I^2^C或3线/4线SPI接口

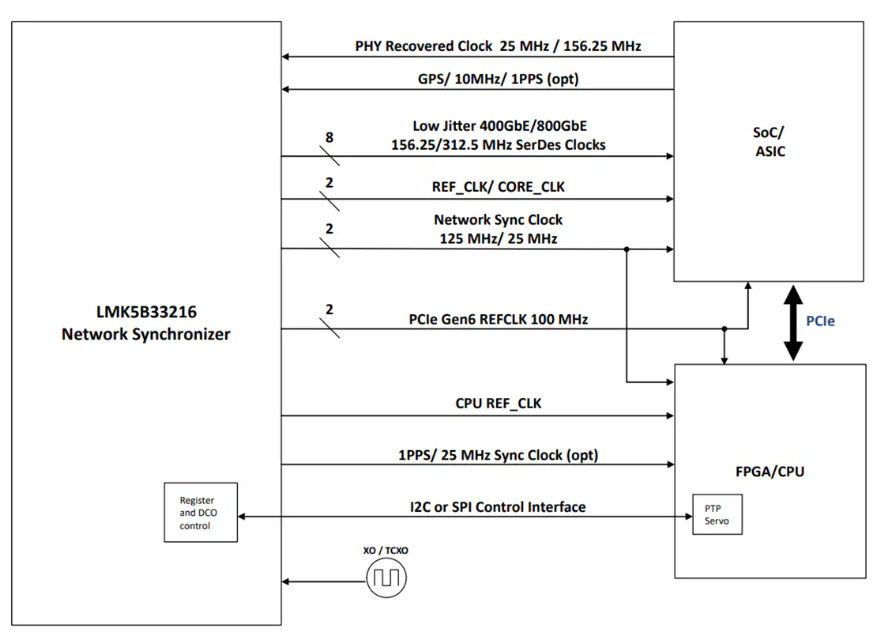

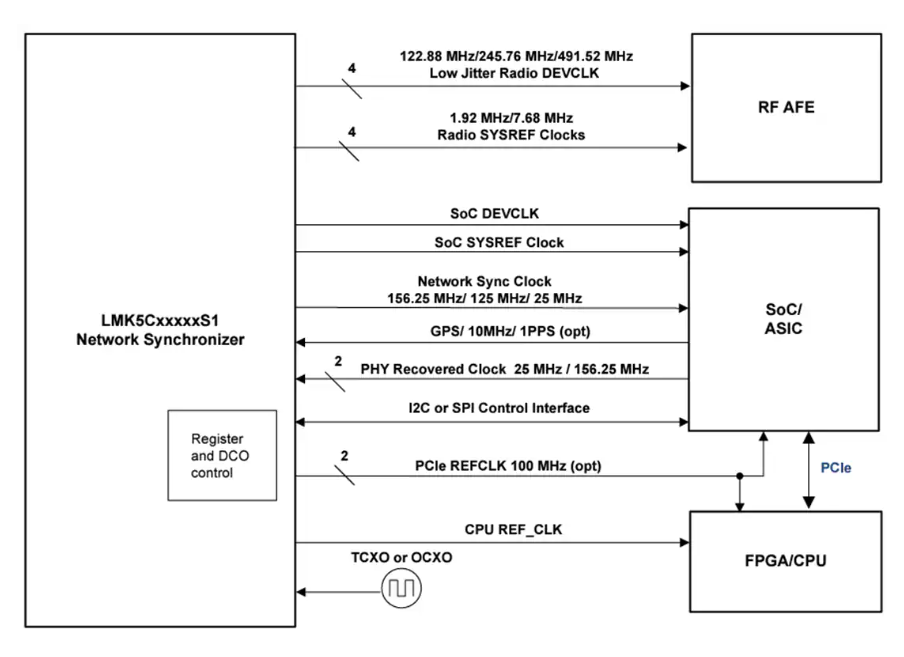

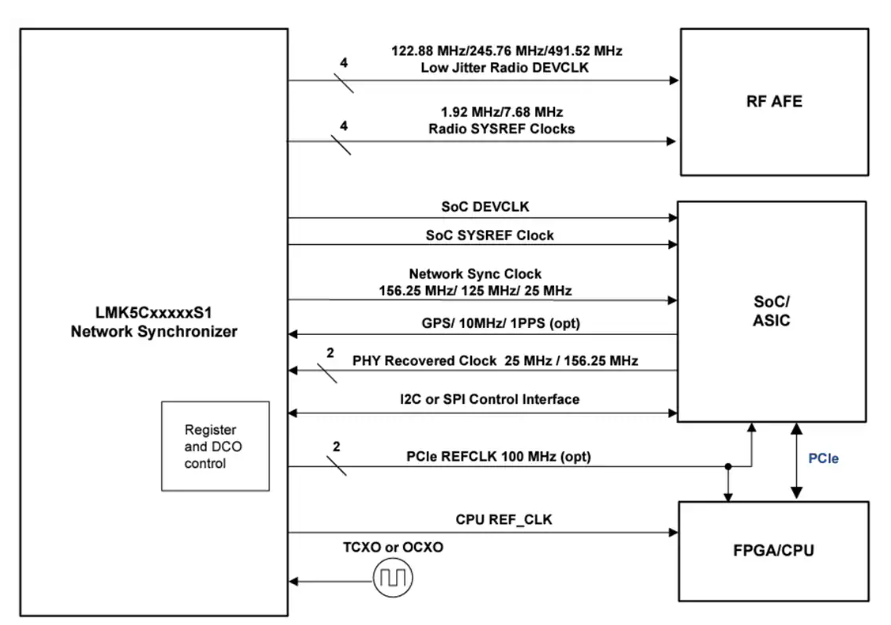

系统方框图

?基于LMK5B33216网络同步器的时钟系统设计与应用?

一、引言

在现代通信和网络设备中,高精度时钟同步是确保数据传输可靠性和系统性能的关键。Texas Instruments推出的LMK5B33216是一款高性能网络同步器和抖动清除器,专为以太网应用设计,具备超低抖动、多PLL架构和灵活的输出配置。本文将从核心特性、应用场景及设计要点三个方面展开分析。

二、核心特性

- ?超低抖动性能?

- 采用BAW(体声波)VCO技术,典型RMS抖动低至13fs(625MHz,4MHz高通滤波)和24fs(312.5MHz),满足高速SerDes和PCIe Gen 6的严苛要求。

- 支持三路数字锁相环(DPLL)和模拟锁相环(APLL),可编程带宽范围1mHz至4kHz,适应不同同步场景。

- ?灵活的输入输出配置?

- ?高集成度与低功耗?

- 集成EEPROM存储自定义启动配置,支持I2C/SPI控制接口,工作温度范围-40°C至85°C。

- 典型功耗850mA(全输出启用),支持按需关闭未使用模块以节能。

三、典型应用场景

- ?数据中心与交换机?

- 为100G-800G交换机提供低抖动时钟,支持SyncE(G.8262)和IEEE-1588协议,满足时间敏感网络(TSN)需求。

- 通过Zero-Delay Mode(ZDM)实现输入输出相位对齐,适用于1PPS同步。

- ? 光传输网络(OTN) ?

- 符合G.709标准,通过APLL级联实现多域时钟同步,降低参考时钟抖动对系统的影响。

- ?工业与医疗设备?

- 在测试仪器和医疗成像中,利用其高稳定性(±100ppm VCO调谐范围)和快速锁相能力(APLL锁定时长35ms)。

四、设计要点与建议

-

以太网

+关注

关注

41文章

5804浏览量

177424 -

清除器

+关注

关注

0文章

34浏览量

6030 -

同步器

+关注

关注

1文章

113浏览量

15335

发布评论请先 登录

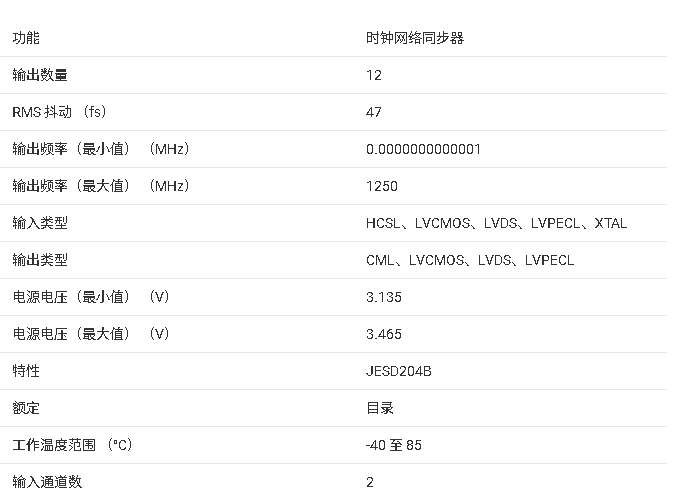

LMK5B33216 3 DPLL、3 APLL、2路输入、16路输出网络同步器数据表

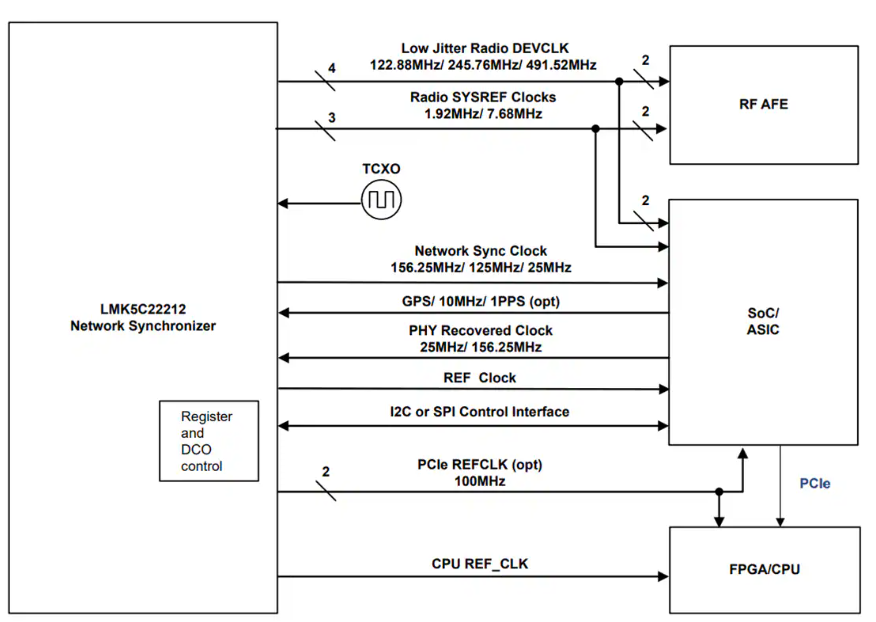

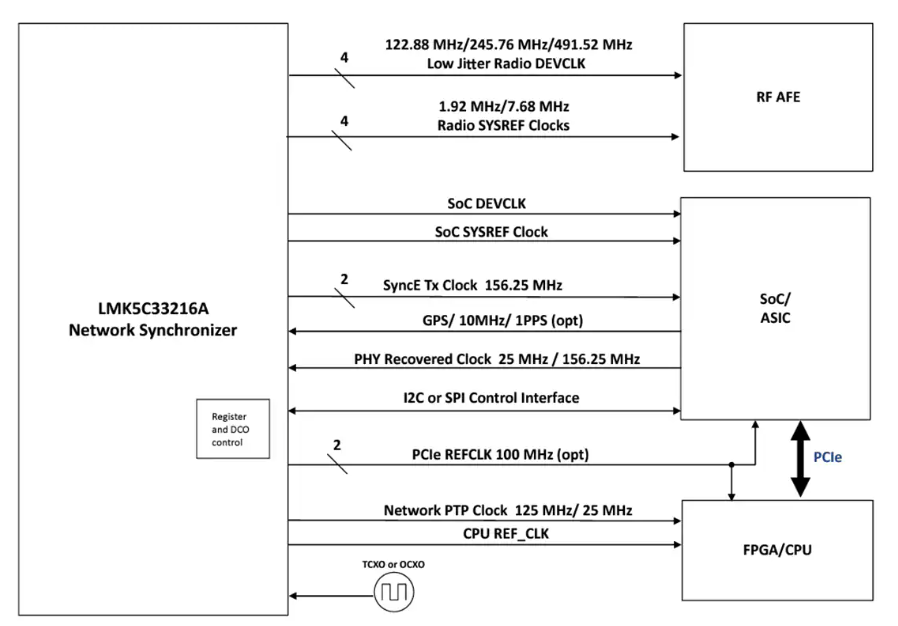

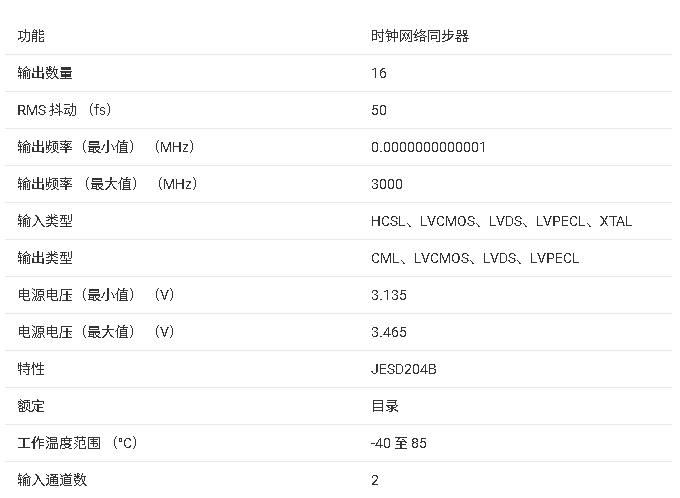

采用JESD204B的LMK5C33216超低抖动时钟同步器数据表

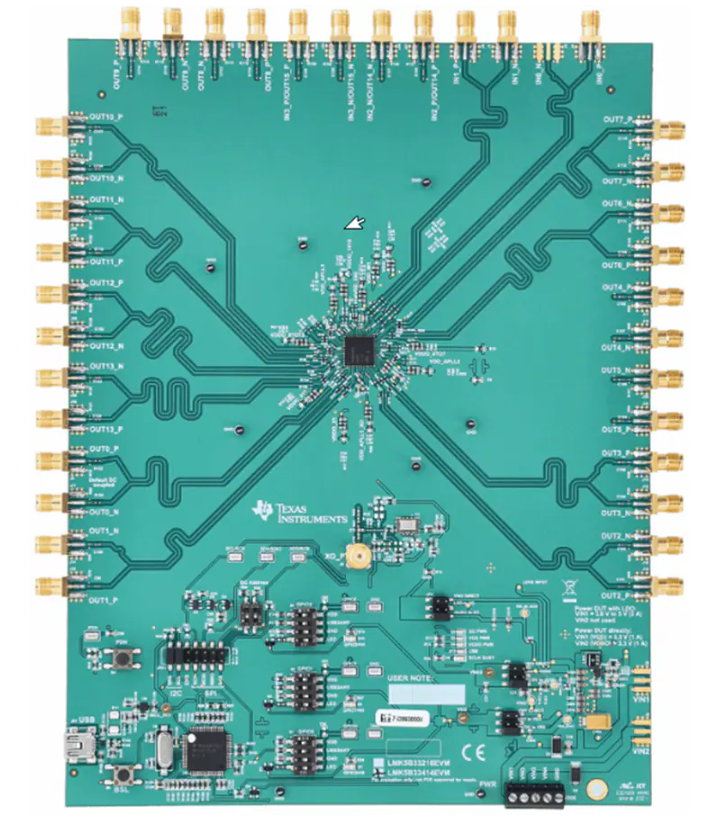

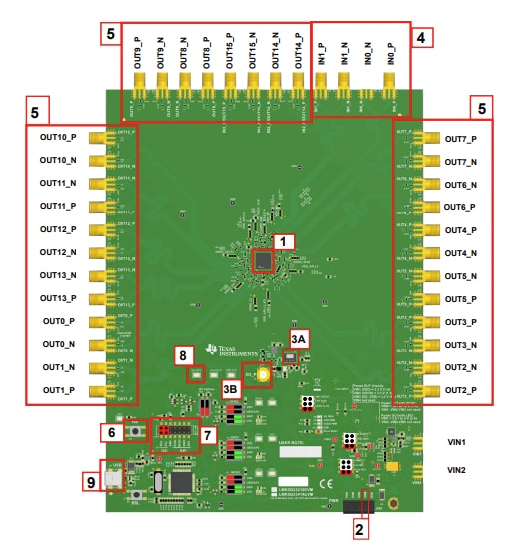

LMK5B33414EVM网络时钟发生器评估模块技术解析

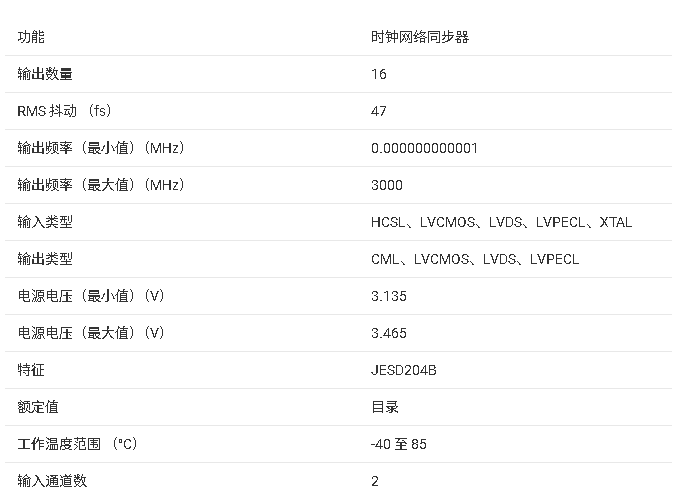

?LMK5C33216A 网络同步器与抖动清除器总结

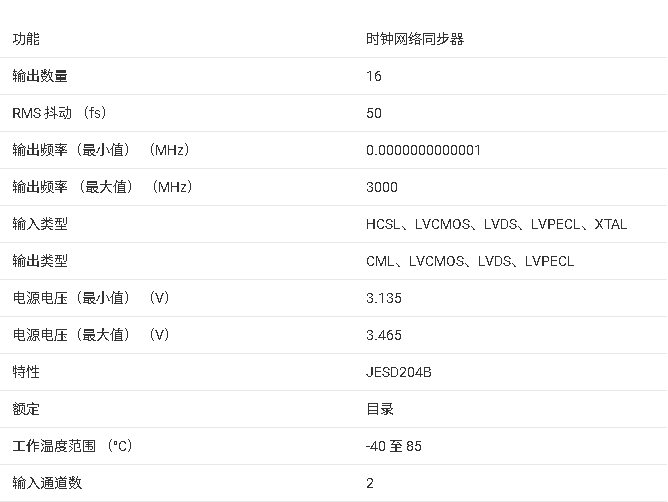

?基于LMK5B33216网络同步器的时钟系统设计与应用

?基于LMK5B33216网络同步器的时钟系统设计与应用

评论