该LMK05318是一款高性能网络同步器时钟器件,可提供抖动清除、时钟生成、高级时钟监控和卓越的无中断开关性能,以满足通信基础设施和工业应用的严格时序要求。该器件的超低抖动和高电源噪声抑制 (PSNR) 可降低高速串行链路中的误码率 (BER)。

该器件可以使用 TI 专有的体声波 (BAW) VCO 技术生成具有 50 fs RMS 抖动的输出时钟,与 XO 和基准输入的抖动和频率无关。

*附件:lmk05318.pdf

DPLL支持用于抖动和漂移衰减的可编程环路带宽,而两个APLL支持小数频率转换,以实现灵活的时钟生成。DPLL支持的同步选项包括带相位消除的无中断开关、数字保持和频率步长小于0.001 ppb(十亿分之一)的DCO模式,用于精确时钟控制(IEEE 1588 PTP从机)。DPLL可以锁相到1-PPS(每秒脉冲)基准输入,并在一个输出上支持可选的零延迟模式,以实现具有可编程失调的确定性输入到输出相位对齐。先进的基准输入监控模块可确保稳健的时钟故障检测,并有助于在发生基准电压源丢失 (LOR) 时最大限度地减少输出时钟干扰。

该器件可以使用常用的低频 TCXO 或 OCXO 来设置符合同步标准的自由运行或保持输出频率稳定性。否则,当自由运行或保持频率稳定性和漂移不重要时,器件可以使用标准 XO。该器件可通过 I 进行完全编程^2^C 或 SPI 接口,并支持通过内部 EEPROM 或 ROM 上电时自定义频率配置。EEPROM 在工厂预编程,如果需要,可以在系统内编程。

特性

- 一个数字锁相环 (DPLL),具有:

- 无中断开关:±50ps 相位瞬变

- 带 Fastlock 的可编程环路带宽

- 使用低成本 TCXO/OCXO 实现符合标准的同步和保持

- 两个模拟锁相环 (APLL),具有行业领先的抖动性能:

- 312.5 MHz时的50 fs RMS抖动(APLL1)

- 155.52 MHz时的125fs RMS抖动(APLL2)

- 两个参考时钟输入

- 基于优先级的输入选择

- 失去参考的数字滞留

- 8个时钟输出,带可编程驱动器

- 多达六种不同的输出频率

- AC-LVDS、AC-CML、AC-LVPECL、HCSL和1.8V LVCMOS输出格式

- EEPROM / ROM,用于上电时自定义时钟

- 灵活的配置选项

- 输入和输出 1 Hz (1 PPS) 至 800 MHz

- XO/TCXO/OCXO 输入:10 至 100 MHz

- DCO 模式:< 0.001 ppb/步,用于精确时钟控制(IEEE 1588 PTP 从机)

- 高级时钟监控和状态

- 我^2^C 或 SPI 接口

- PSNR:–83 dBc(3.3V电源时噪声为50 mVpp)

- 3.3V电源,1.8V、2.5V或3.3V输出

- 工业温度范围:–40°C 至 +85°C

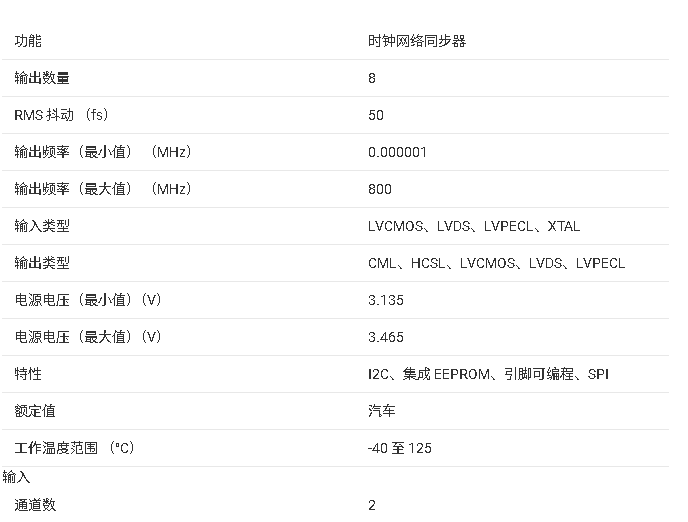

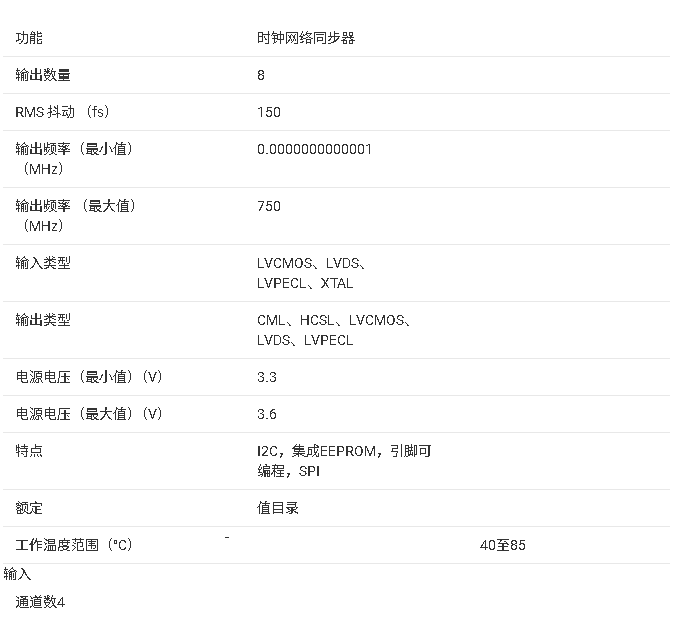

参数

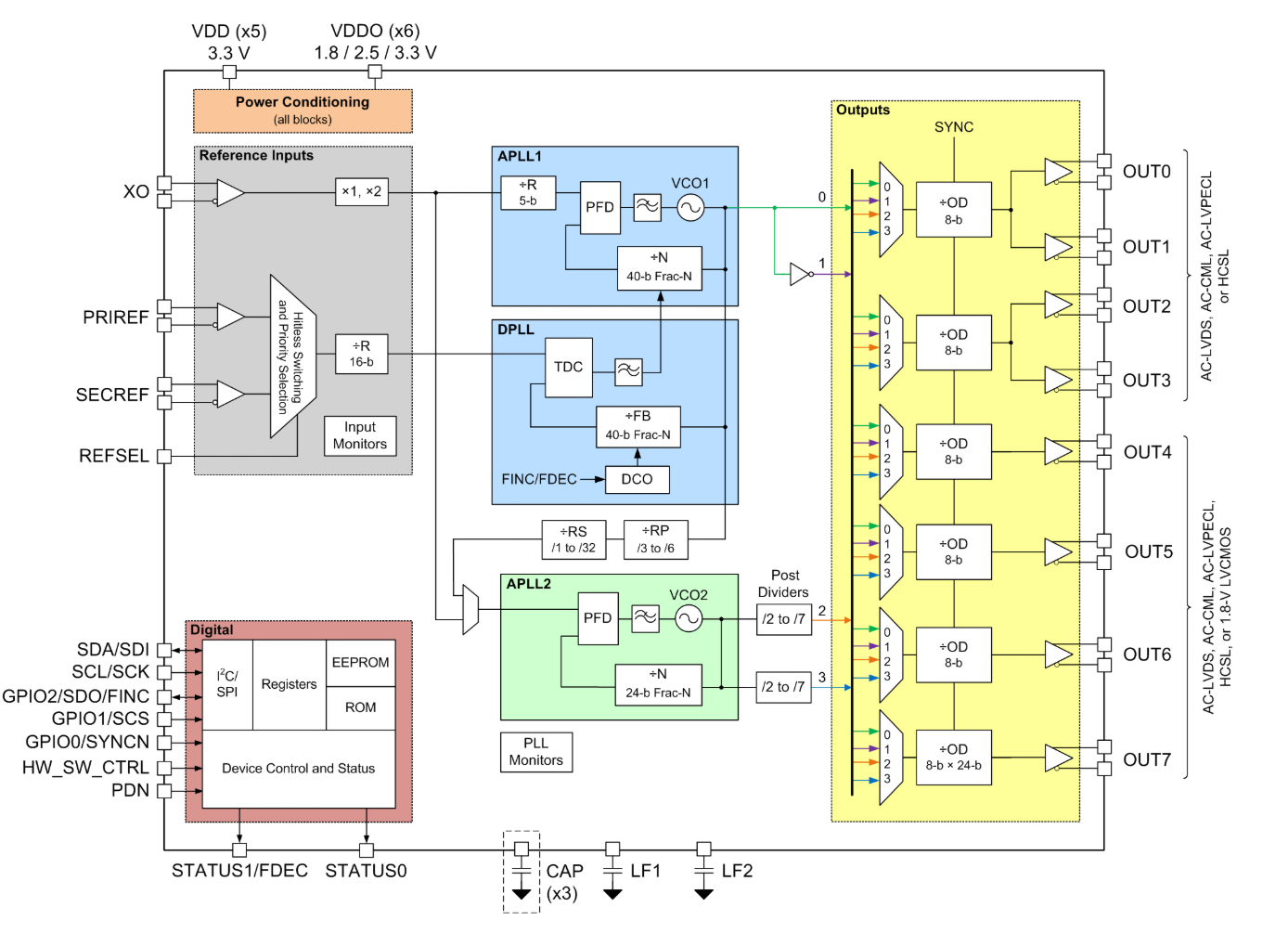

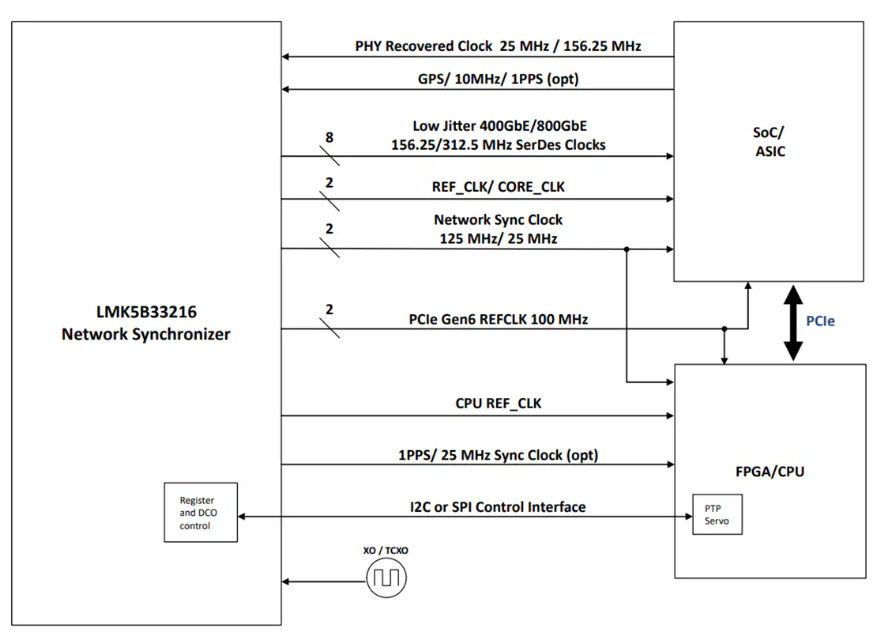

方框图

?1. 概述?

LMK05318是德州仪器(TI)推出的高性能网络同步时钟器件,专为通信基础设施和工业应用设计,提供超低抖动时钟生成、高级时钟监控和无缝切换性能。其核心特性包括:

- ?双域频率架构?:支持两个独立的频率域(APLL1和APLL2),分别基于BAW VCO和LC VCO技术。

- ?超低抖动?:APLL1典型抖动为50 fs RMS(312.5 MHz),APLL2为125 fs RMS(155.52 MHz)。

- ?多参考输入?:支持两个优先级可编程的参考时钟输入(PRIREF/SECREF),具备数字保持(holdover)和DCO模式(IEEE 1588 PTP从时钟支持)。

?2. 关键特性?

- ? 数字锁相环(DPLL) ?:支持±50 ps相位瞬态的无缝切换、可编程环路带宽和快速锁定。

- ? 模拟锁相环(APLL) ?:

- APLL1:基于BAW VCO,独立于外部XO抖动的50 fs RMS性能。

- APLL2:支持级联或独立模式,生成无关时钟频率。

- ?输出灵活性?:8个可编程时钟输出,支持AC-LVDS/CML/LVPECL、HCSL和1.8V LVCMOS格式,最高800 MHz频率。

- ?监控与诊断?:集成输入时钟监控(幅度、频率、丢失脉冲等)、PLL锁定检测和状态中断功能。

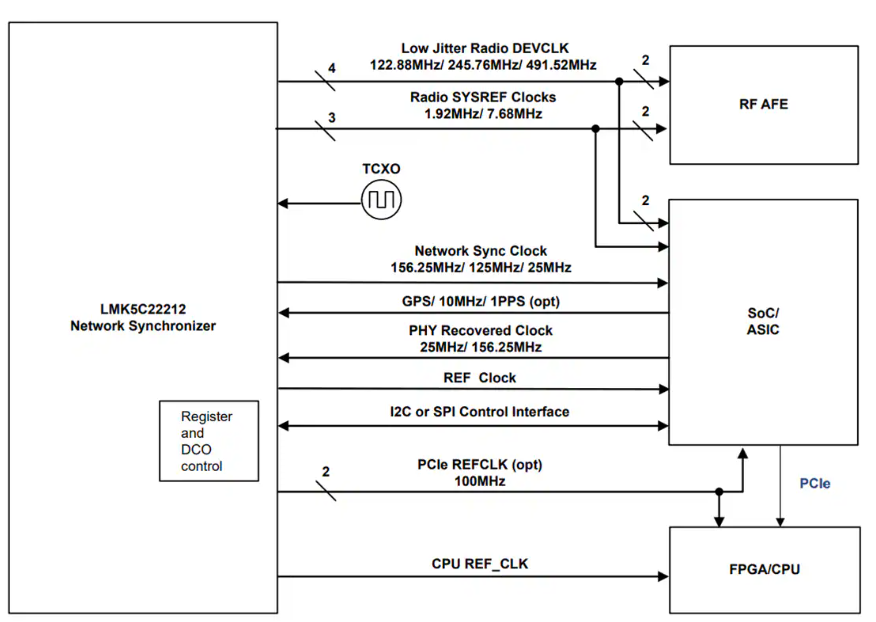

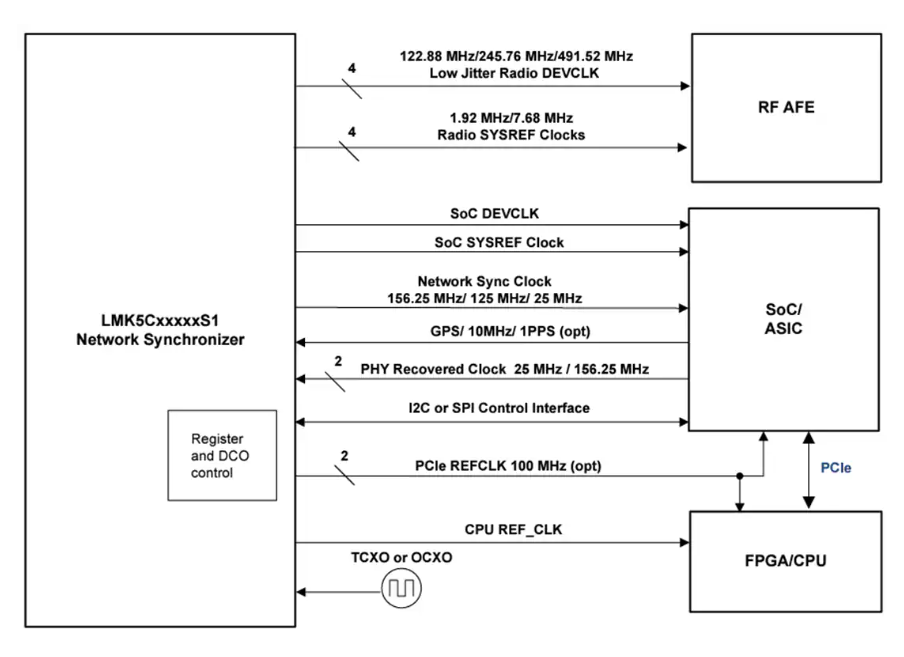

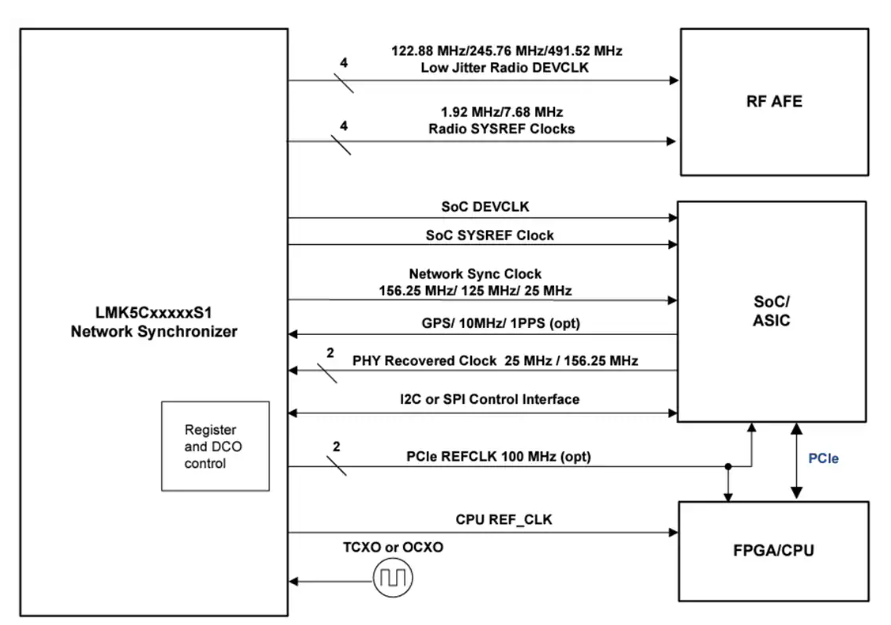

?3. 应用场景?

- ?通信设备?:SyncE(G.8262)、SONET/SDH(Stratum 3/3E)、IEEE 1588 PTP从时钟、光传输网络(G.709)。

- ?高速数据链路?:56G/112G PAM-4 PHY、ASIC/FPGA/SoC参考时钟。

- ?无线基础设施?:基站(BTS)、无线回传。

?4. 技术细节?

- ?电源管理?:3.3V核心供电,1.8V/2.5V/3.3V输出供电选项,集成LDO提升PSNR(-83 dBc)。

- ?接口与控制?:支持I2C/SPI编程,内置EEPROM/ROM存储配置,支持自定义启动频率。

- ?热性能?:工业温度范围(-40°C至+85°C),10层PCB设计下θJA为9.1°C/W。

?5. 设计支持?

- ?配置工具?:TICS Pro软件生成寄存器设置和频率规划。

- ?参考设计?:提供布局指南、电源去耦建议和热优化方案。

?6. 文档结构?

数据手册包含以下章节:

?总结?:LMK05318通过集成DPLL和双APLL架构,为高速网络和时序关键应用提供高精度、低抖动的时钟解决方案,同时支持灵活的配置和监控功能。

-

时钟器件

+关注

关注

0文章

13浏览量

8145 -

电源噪声

+关注

关注

3文章

166浏览量

17913 -

串行链路

+关注

关注

0文章

12浏览量

8336 -

BAW

+关注

关注

3文章

143浏览量

19233 -

网络同步器

+关注

关注

0文章

24浏览量

1702

发布评论请先 登录

LMK05318是否可以对Switch输出的1588 clock进行同步锁频、锁相?

LMK05318在TICS Pro中怎样设置,可以加快同步的速度,实现几分钟之内相位同步?

贸泽推出配备BAW谐振器的Texas Instruments 超低抖动LMK05318时钟

采用JESD204B的LMK5C33216超低抖动时钟同步器数据表

LMK5B12204具有两个频域的超低抖动网络同步器时钟数据表

LMK05318具有两个频域的超低抖动网络同步器时钟数据表

具有EEPROM的LMK05028低抖动双通道网络同步器时钟数据表

LMK05318 带BAW的超低抖动单通道网络同步器时钟技术手册

LMK05318 带BAW的超低抖动单通道网络同步器时钟技术手册

评论