本文要点

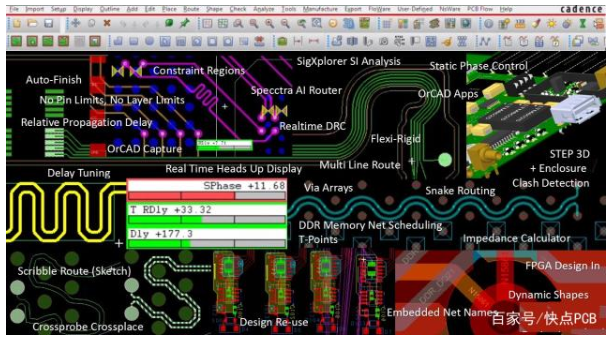

作为一名资深的电子设计工程师,在 Allegro中将走线优化好、散热调整好、阻抗控制精准,能够为后期调试和改板省下不少心力,好处就不用多说了!

上期我们介绍了如何利用约束管理器去约束我们的走线;本期我们将教会大家如何更快更精准的优化我们的布线。

应用场景

1.两条甚至多条高速线(例如:时钟、差分对、高速数据线)长距离紧挨着走线时,它们之间会通过电场和磁场产生能量,就需要在布平行线的时候做约束,优化布线即在一定程度上减少了串扰,又能够保证时序。

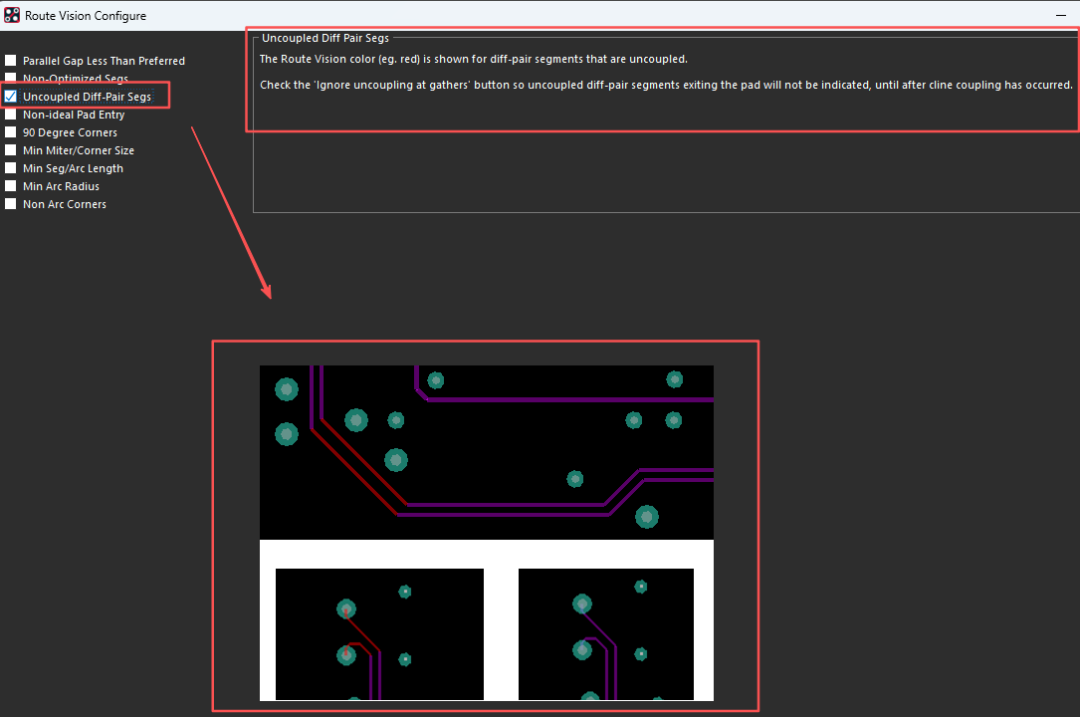

2.在高速电路设计中,当差分对的布线不对称、两根线之间的距离过大时,会造成共模噪声抑制能力大幅减弱、阻抗失控、导致信号反射、时序偏差等问题。处理未耦合的差分对,优化布线能够调整间距,实现均匀耦合。

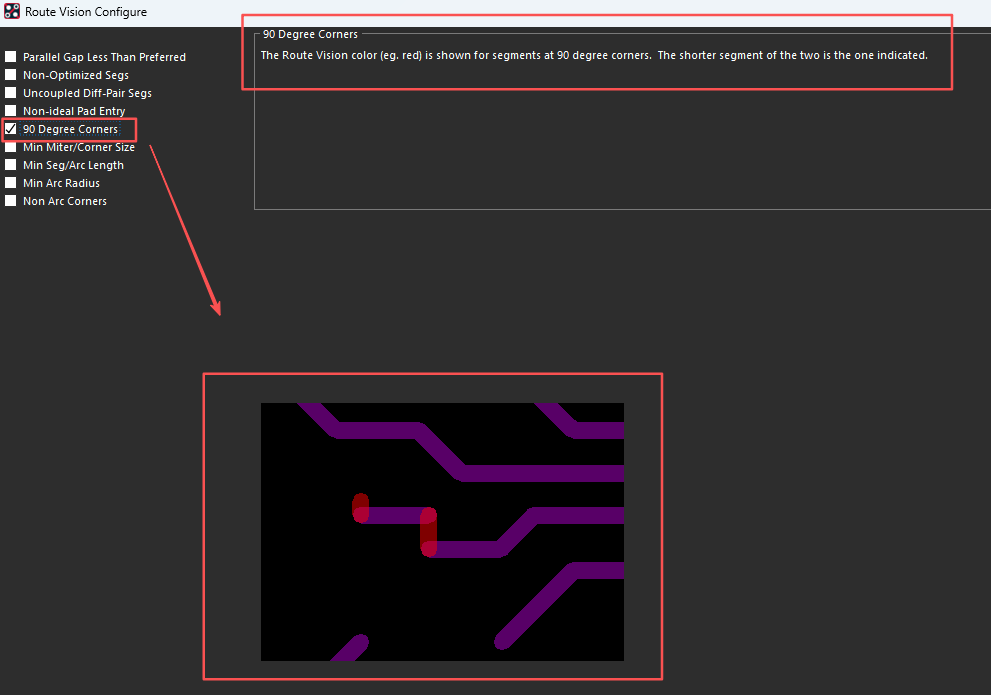

3.在高频/射频电路中,走线90°的尖角会像一个微型天线,产生不必要的寄生电容和电感,增加辐射损耗和反射,恶化插入损耗和回波损耗,直接影响射频性能和功率传输效率,因此需要在布线完成后对于整个电路板进行布线优化。养成好习惯,能够让你的设计水平立竿见影,专业程度立马提升。

运行环境

1、操作系统:Win 11

2、Cadence软件配置:Allegro X Designer Plus 24.1-2024 P001 [9/4/2024] Windows SPB 64-bit EditionEdition

布线优化

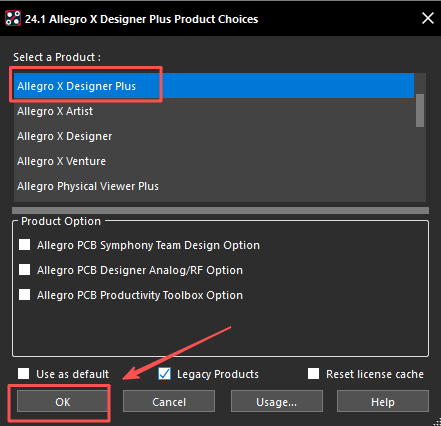

1.打开Cadence软件,选择产品Allegro X Designer Plus,点击OK进入软件。

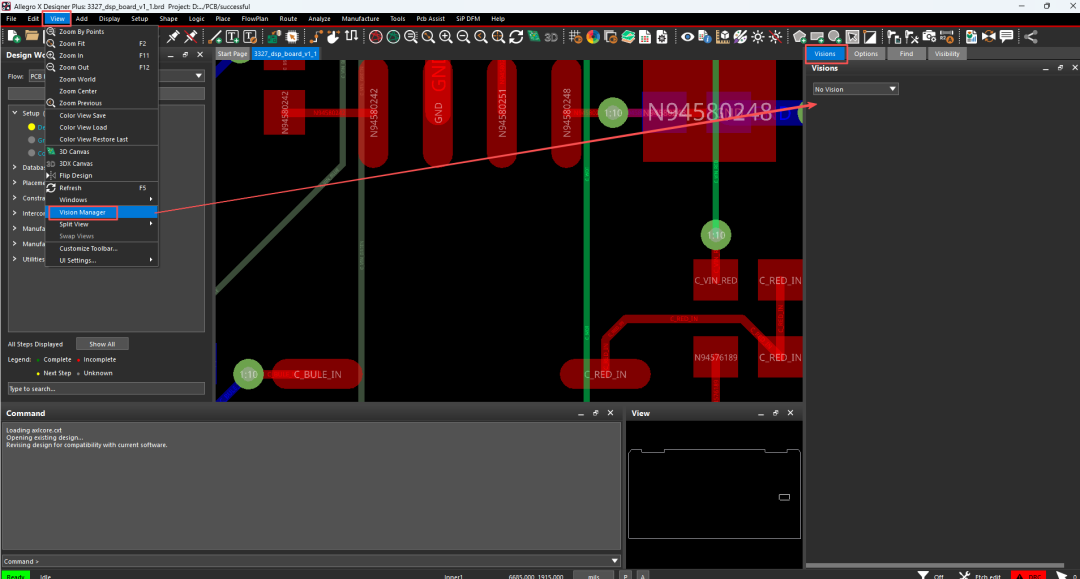

2.点击View-Vision Manager,打开Visions窗口界面。

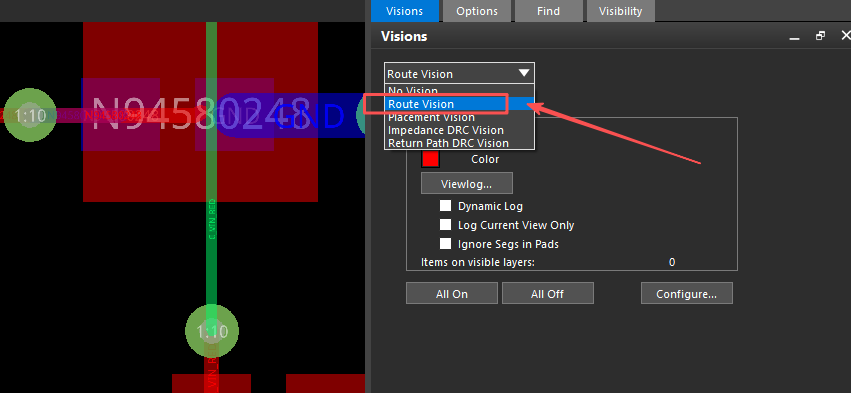

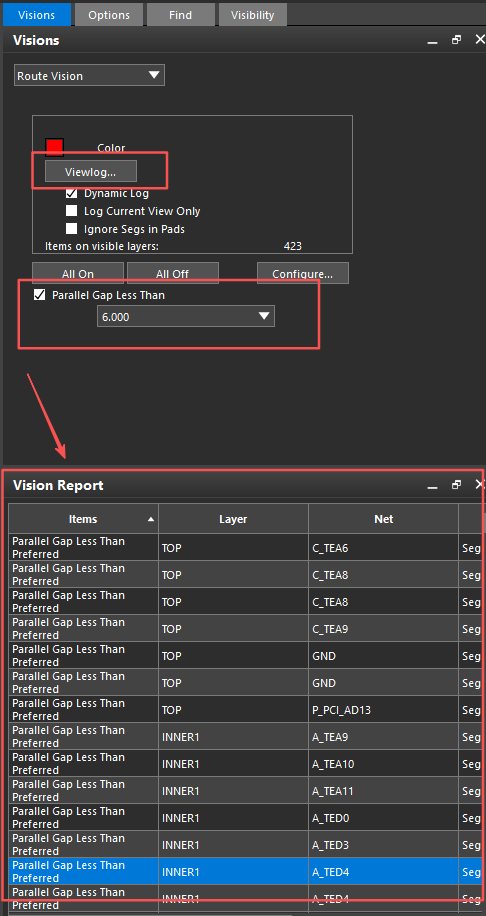

3.在Vision窗口界面下拉选择Route Vision,启用布线配置。

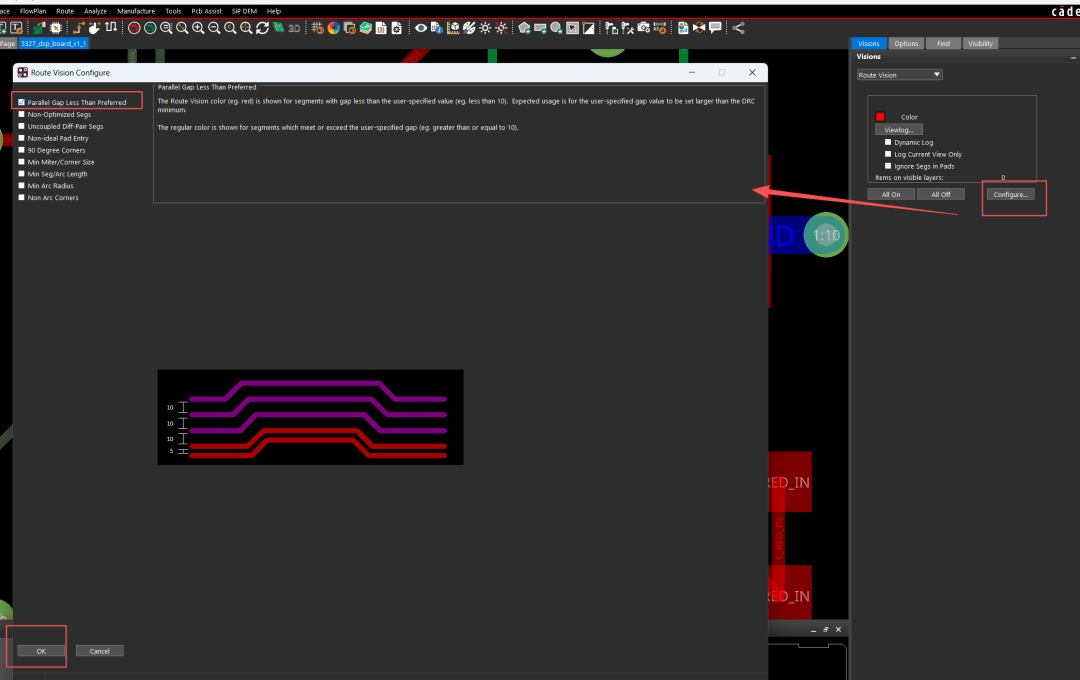

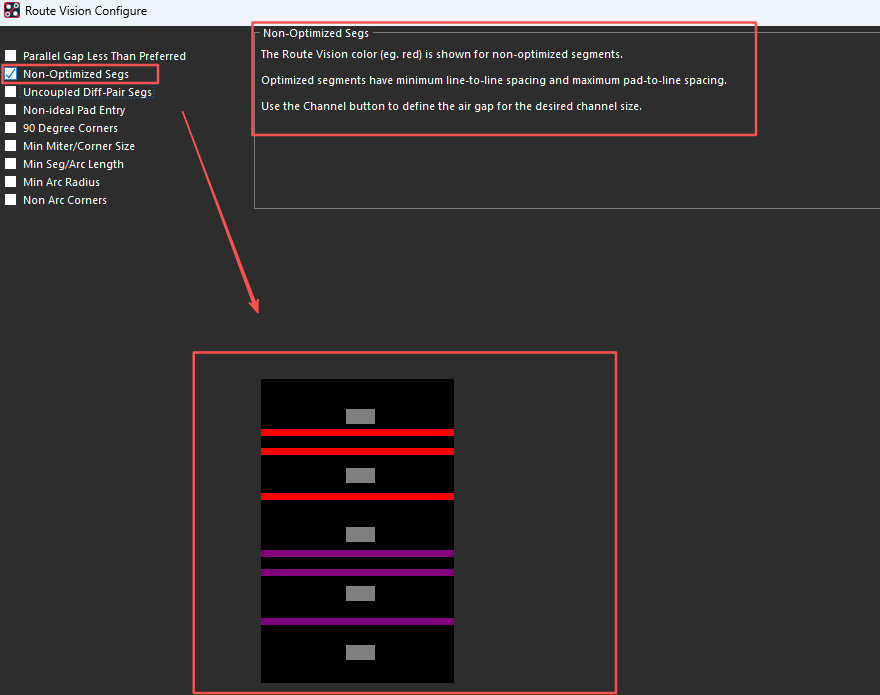

4.点击Configure进行配置,仅勾选(平行间隙小于标准值),当鼠标悬停在勾选对话框时,在界面下方会展示该选项的说明以及相关的图表。

5.选择ok进行配置。

6.回到Visions界面,勾选Dynamic Log,可查看不满足布线要求的值

7.勾选Parallel Gap Less Than并设置平行线之间的标准值为6mil。

8.点击Viewlog,接着在下方的Vision Report界面就可以查看平行线之间的距离小于标准值的层以及网络的报告,双击报告中的某一项内容,allegro会自动定位到未满足距离要求的走线上。

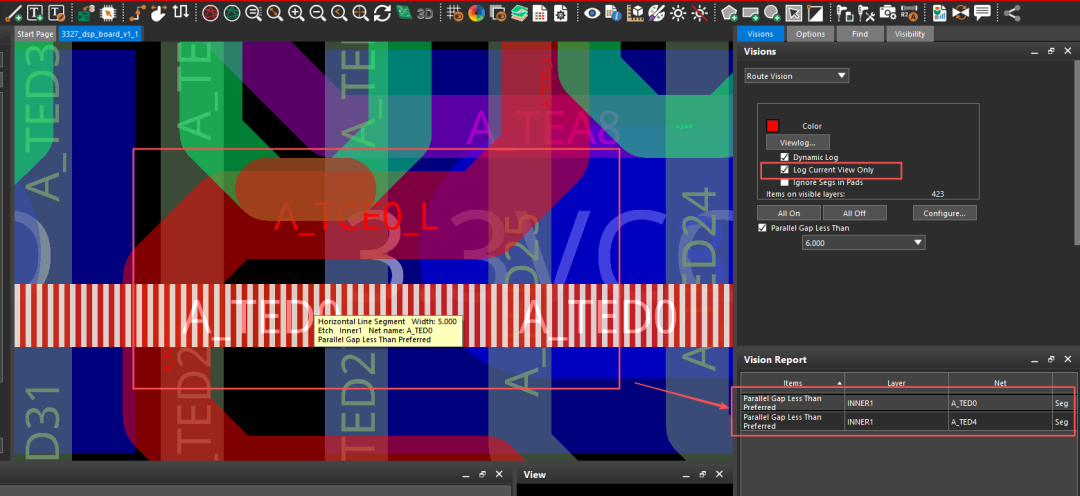

9.在Visions界面勾选Log Current View Only,当在Allegro的布线界面进行缩放操作时,Vision Report会迅速缩减为仅包含在视图中显示的区域的项目,更好的对布线进行局部优化;当我们在视图中对于布线进行优化完成后,走线将由红色恢复为正常走线颜色,同时动态日志也会自动更新。

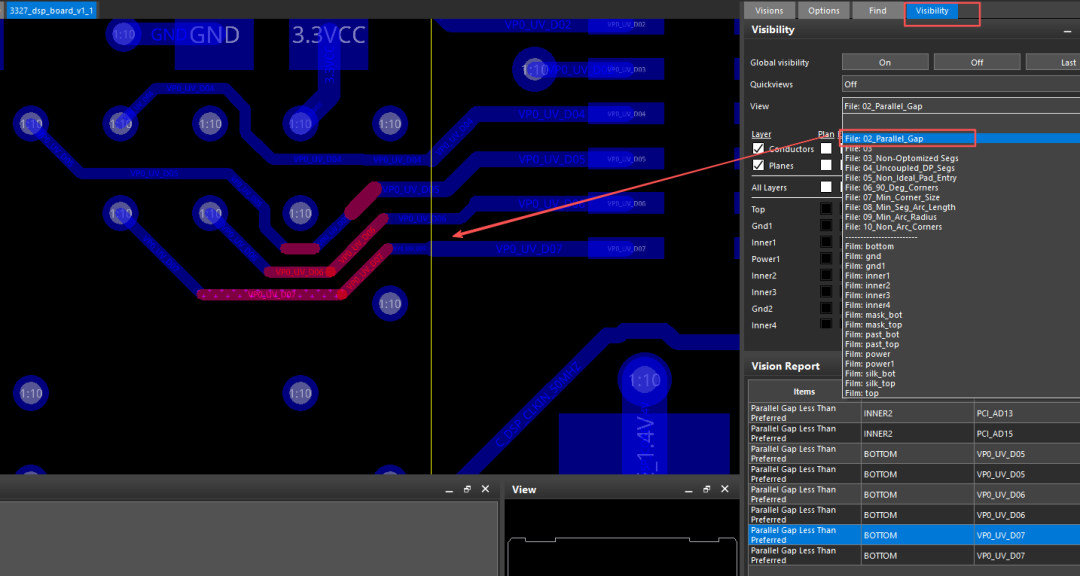

10.也可以来到Visibilityjiamian ,在view对话框下拉选择File:02_Parallel_Gap,也可以实现快速定位。

几种布线优化命令

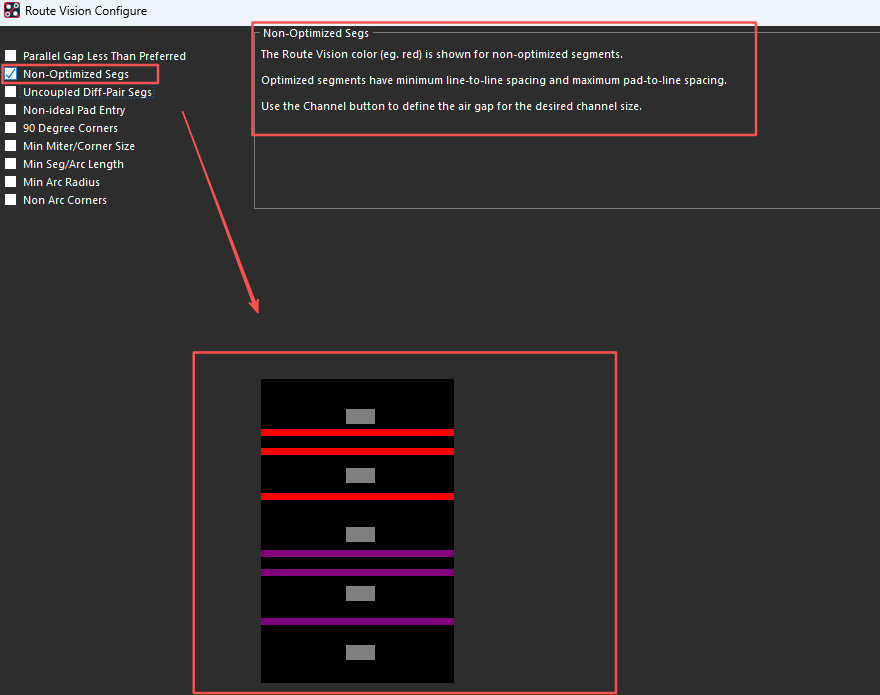

1.Non-Optimized Segs:优化焊盘之间的布线间距以及走线与焊盘之间的间距。

2.Uncoupled Diff-Pair Segs:未耦合差分对检查,差分对用于实现相位控制则需要分离和解耦,快速定位解耦线段。

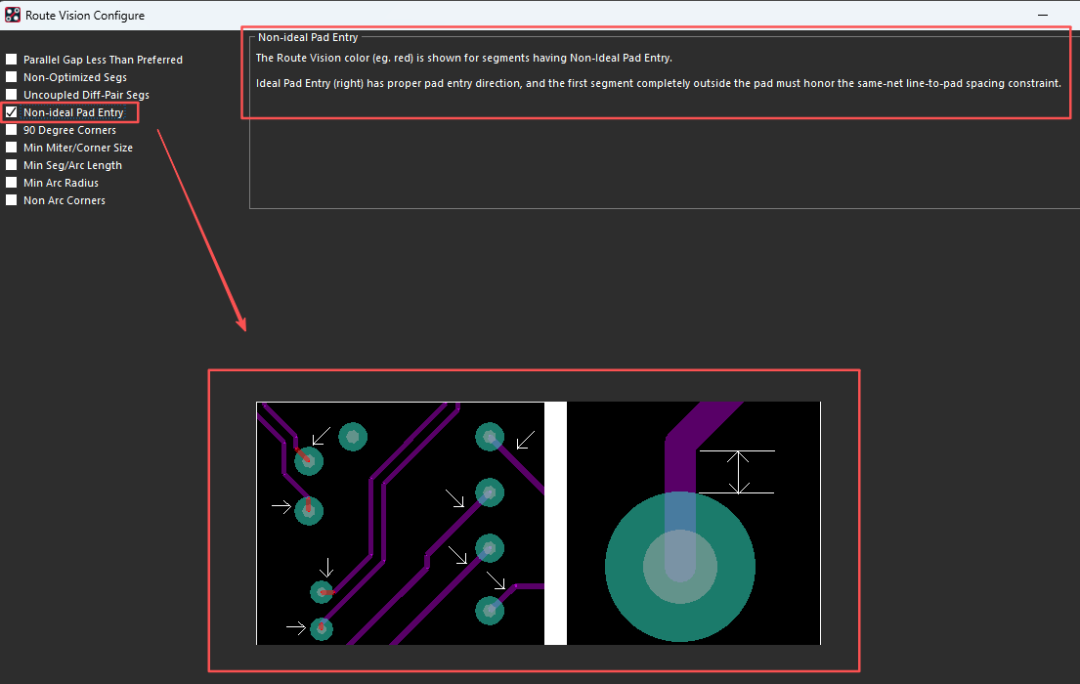

3.Non-ideal Pad Entry:检查同一网线与引脚之间的间距,以确保在转弯前各段能正确地从引脚处伸出。

4.90 Degree Corners:识别出那些在设计中通常不被接受的90度拐角。

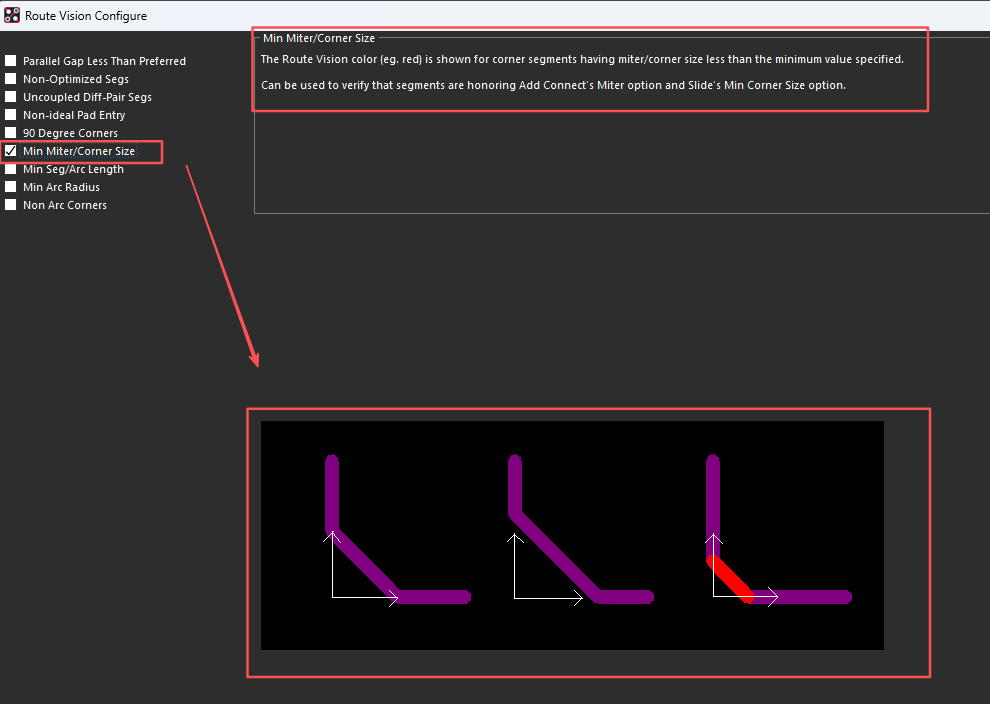

5.Min Miter/Corner Size:用于确定低于设定参数的转角位置,验证走线中的斜坡/管脚是否满足要求。

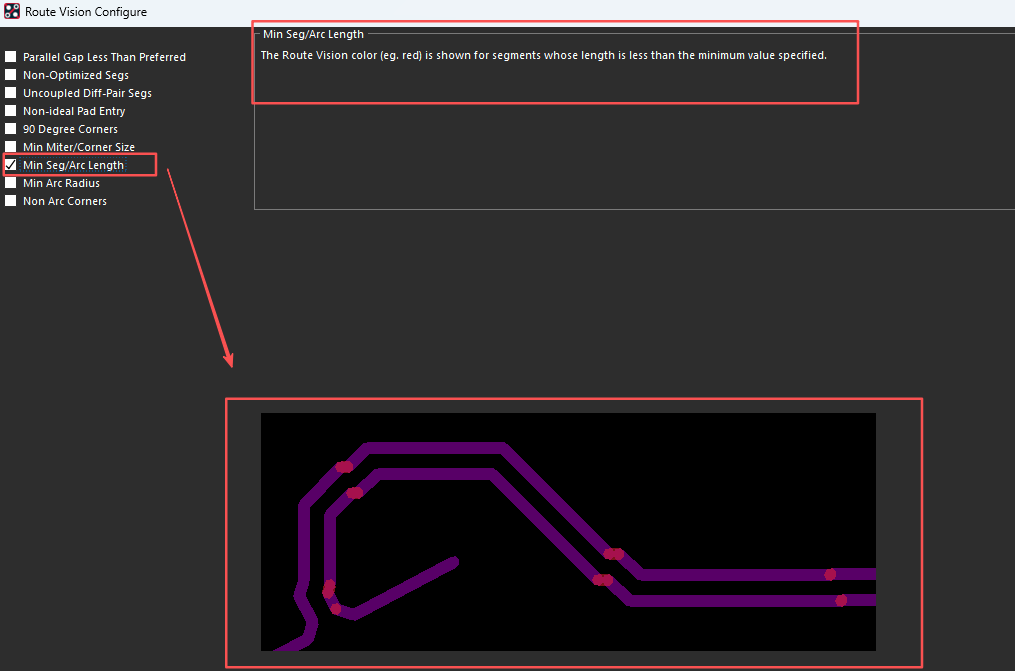

6.Min Seg/Arc Length:突出显示低于设定参数的分段或弧形部分。

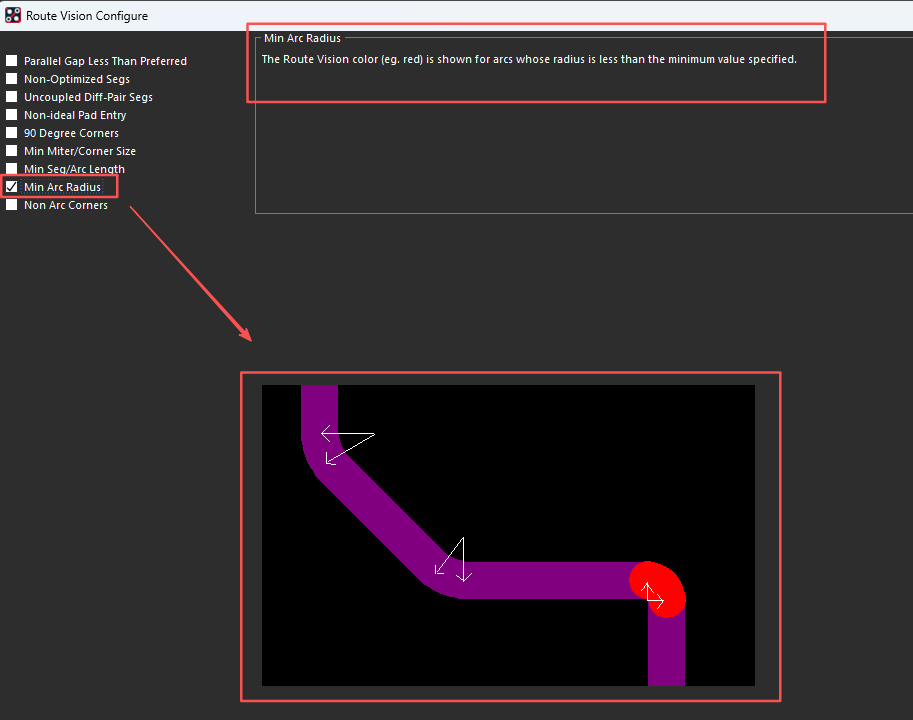

7.Min Arc Radius:找出任何低于设定参数的弧线。

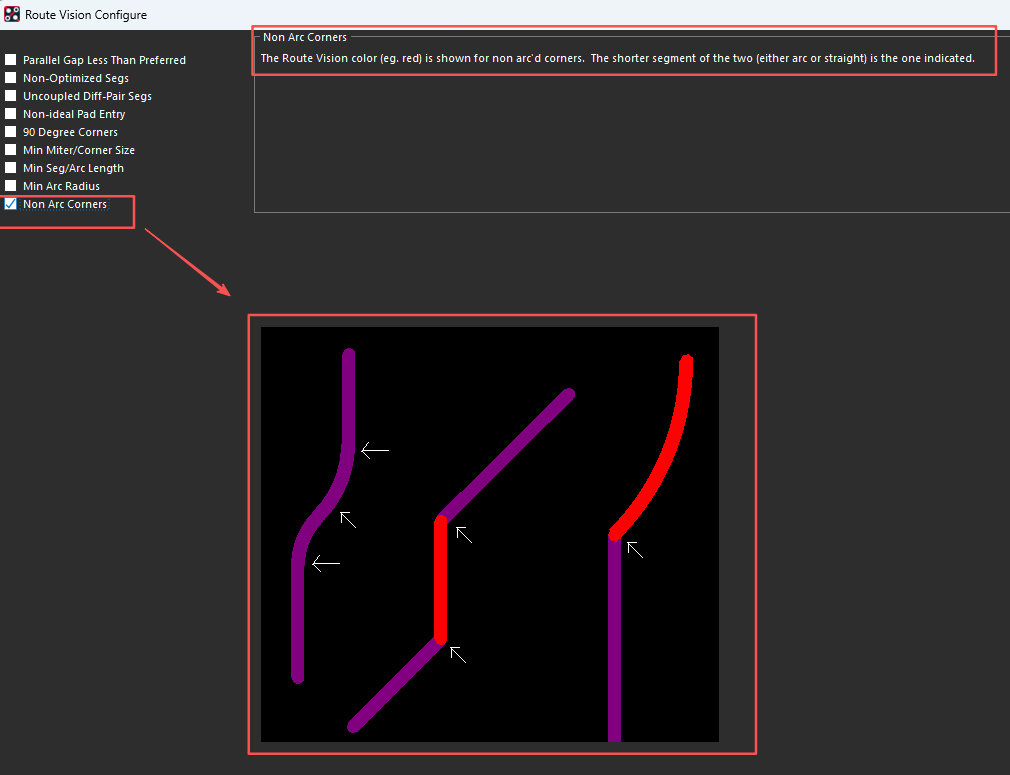

8.Non Arc Corners:用于查找任何非弧形的拐角或弧形部分。

总结栏

本期主要为大家揭秘了如何实现布线精准定位并优化,下一期我们将为大家呈现不同封装器件的快速扇出孔,为大家的PCB布局布线带来便利。

-

PCB设计

+关注

关注

396文章

4854浏览量

91915 -

布线

+关注

关注

9文章

804浏览量

85456 -

allegro

+关注

关注

42文章

744浏览量

148273 -

电子设计

+关注

关注

42文章

832浏览量

49417

发布评论请先 登录

Cadence新的Allegro平台变革下一代PCB设计生产力

PCB抄板之PROTEL到ALLEGRO的转换技术

Cadence新Allegro平台为PCB设计工程师树立全新典范

Cadence Allegro平台先进的约束驱动PCB流程和布线能力

Allegro技术如何助力EDA360目标的实现

AD PCB封装转Allegro封装或者AD PCB转Allegro PCB

技术资讯 I 高效差分对布线指南:提高 PCB 布线速度

PCB设计布线Cadence 20问

Allegro X 23.11 版本更新 I PCB 设计:DFA_BOUND 用于 DFA 规则设定

技术资讯 I 如何使用 Allegro X PCB Editor 优化RF布线和阻抗

技术资讯 I Allegro PCB 设计中布线优化

技术资讯 I Allegro PCB 设计中布线优化

评论