Texas Instruments LMX1204EVM评估模块 (EVM) 设计用于评估LMX1204的性能,LMX1204是一款四路输出、超低附加抖动射频 (RF) 缓冲器、分频器和乘法器。该评估模块可以在3.2GHz至6.4GHz输出范围内缓冲高达12.8GHz射频时钟输入,实现x2、x3或x4倍,最多将输入分成8个。

数据手册:*附件:Texas Instruments LMX1204 EVM评估模块 (EVM)数据手册.pdf

Texas Instruments LMX1204EVM包含一个独立的辅助时钟分频器,用于现场可编程门阵列 (FPGA) 和逻辑时钟计时。每个输出均包含一个系统参考 (SYSREF) 补充,具有皮秒精度和延迟调谐功能。可以同步多个器件以实现宽时钟分布树。

特性

- 12.8GHz缓冲器,高达6.4GHz乘法器,最多可以分成8个

- 6GHz时噪声本底为-160dBc/Hz

- 四个射频输出和SYSREF对

- SYSREF发生器,具有每输出皮秒精密延迟调谐功能

- 用于FPGA和逻辑的辅助分频器,带SYSREF

- 支持多器件同步

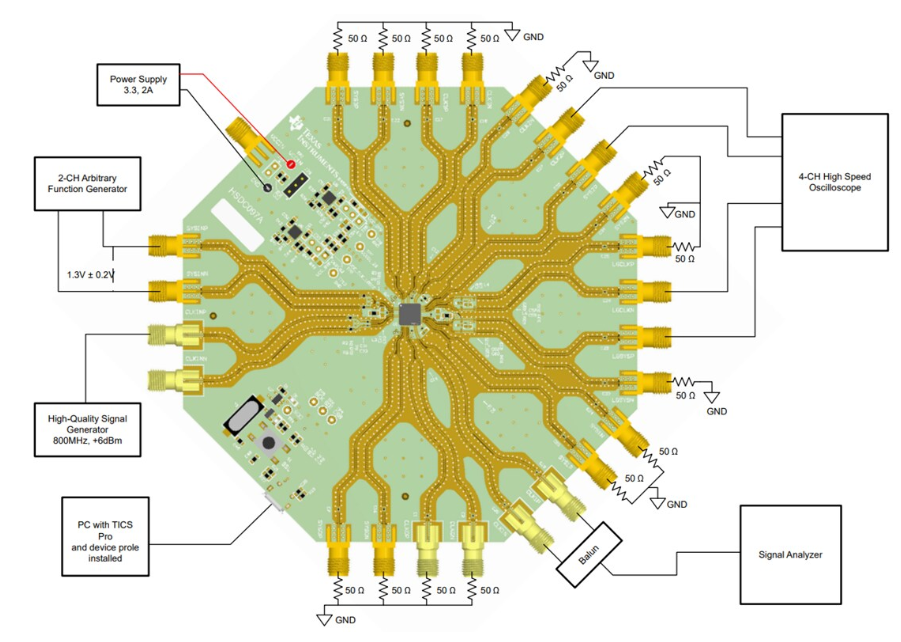

测试设置

LMX1204低噪声高频JESD缓冲器/倍频器/分频器技术解析

一、器件概述

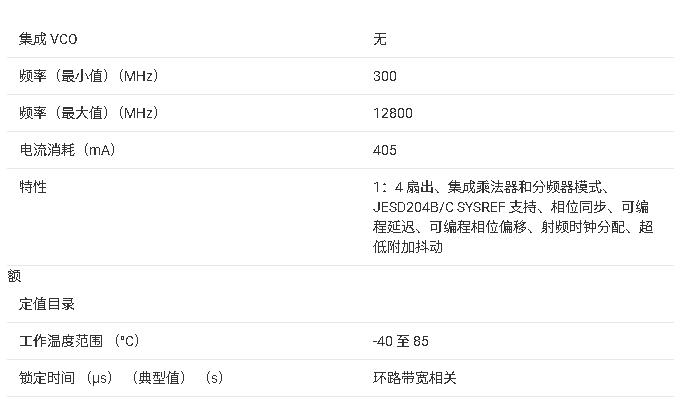

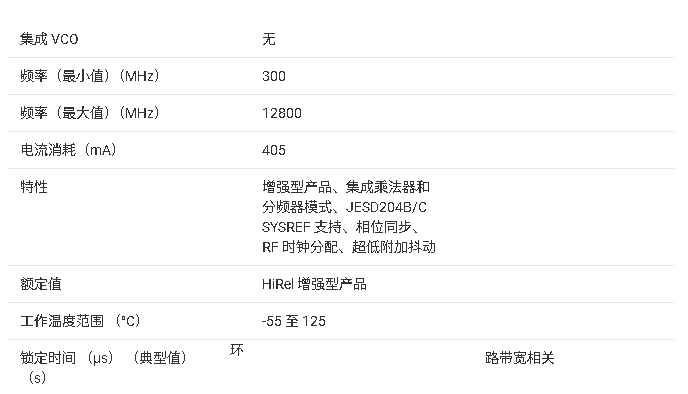

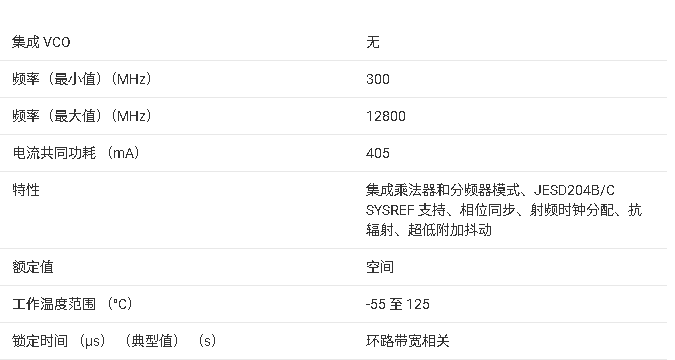

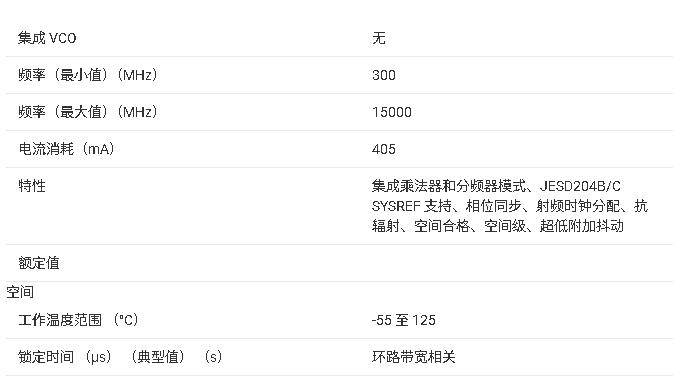

LMX1204是德州仪器(TI)推出的一款高性能时钟管理芯片,具有超低噪声特性,输出频率范围覆盖300MHz至12.8GHz。该器件集成了缓冲、倍频和分频功能,特别适合高精度数据转换器的时钟应用。

关键特性

- ?超低噪声性能?:在6GHz输出时噪声基底低至-161dBc/Hz,1/f噪声为-154dBc/Hz@10kHz偏移

- ?灵活的频率处理?:支持×1(缓冲模式)、×2、×3、×4倍频和÷2至÷8分频

- ?多通道输出?:提供4路高频时钟输出和1路独立逻辑时钟输出(LOGICLK)

- ?JESD204B/C兼容?:每路时钟输出配有同步SYSREF输出,支持生成器和中继器模式

- ?宽工作范围?:2.5V供电电压,-40°C至85°C工作温度

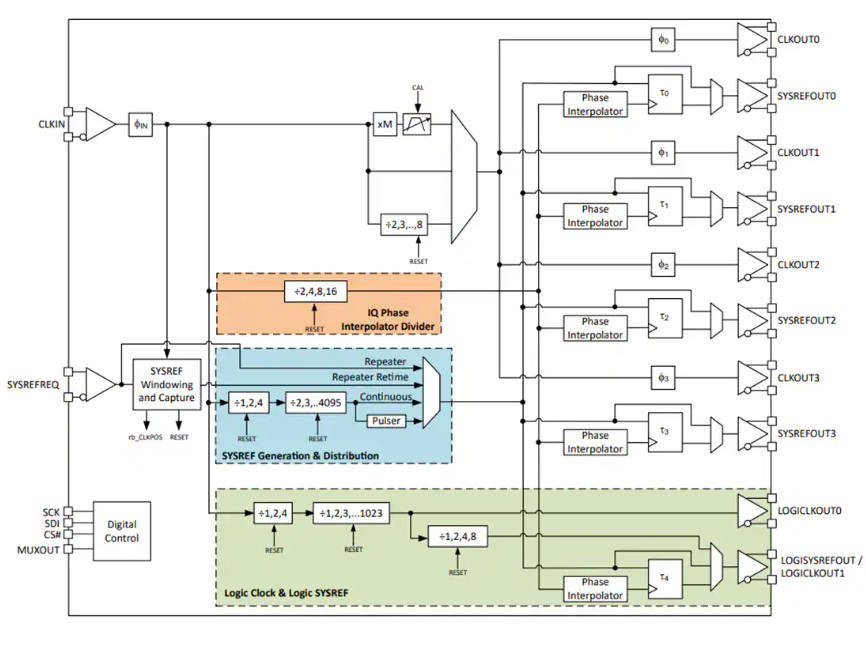

二、功能架构分析

2.1 核心功能模块

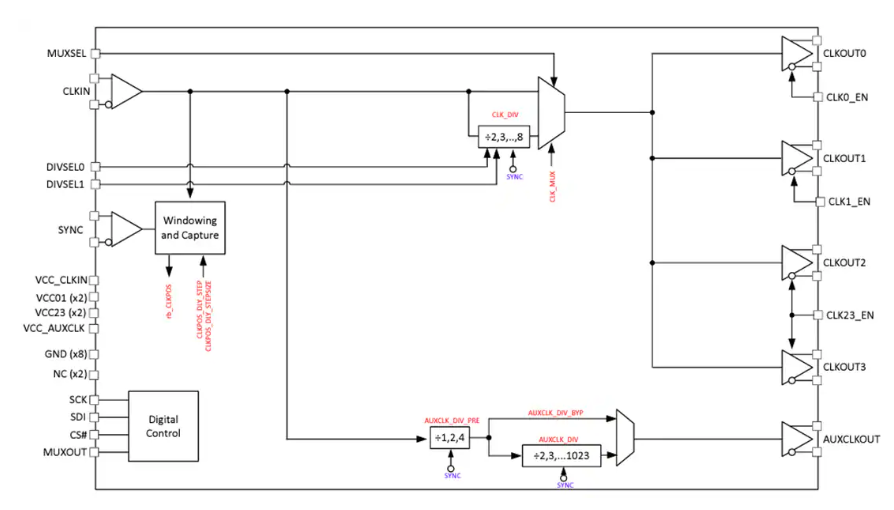

LMX1204采用模块化设计,主要包含以下功能单元:

- ?时钟输入处理单元?

- 支持差分输入,内部集成50Ω终端

- 可配置为缓冲、倍频或分频模式

- 倍频模式采用PLL架构,集成VCO

- ?时钟分配网络?

- 4路主时钟输出(CLKOUT0-3)

- 1路独立逻辑时钟输出(LOGICLKOUT)

- 每路输出可单独配置功率等级(8级可调)

- ?SYSREF生成系统?

- 支持内部生成或外部输入中继

- 可编程延迟调节(508步进,每步<2.5ps@12.8GHz)

- 支持脉冲模式和连续模式

2.2 工作模式配置

LMX1204提供三种主要工作模式,通过CLK_MUX寄存器选择:

| 模式 | 配置寄存器 | 功能描述 |

|---|---|---|

| 缓冲模式 | CLK_MUX=0x1 | 直接缓冲输入时钟,保持原始频率和相位特性 |

| 分频模式 | CLK_MUX=0x2 | 支持÷2至÷8分频,奇数分频时占空比非50% |

| 倍频模式 | CLK_MUX=0x3 | 支持×1(滤波模式)、×2、×3、×4倍频,需进行VCO校准 |

三、典型应用场景

3.1 测试测量系统

在示波器、无线设备测试仪等应用中,LMX1204可提供:

3.2 航空航天与国防

适用于相控阵雷达、电子战等关键系统:

- 12.8GHz高频输出满足毫米波应用

- -40°C至85°C宽温工作范围

- 抗辐射增强设计(需特殊版本)

3.3 数据转换器时钟

- 抖动性能优于多数数据转换器的孔径抖动

- 支持多器件级联架构

- 可编程输出功率匹配不同负载需求

四、设计考量要点

4.1 电源设计建议

4.2 布局布线指南

- ?时钟输入?:

- 保持差分对严格等长(±50ps以内)

- 单端驱动时,未用端接50Ω至地

- ?输出端接?:

- ?热管理?:

- 40引脚VQFN封装(6mm×6mm)

- θJA=24.8°C/W,全功率工作时需考虑散热

五、性能实测数据

根据TI提供的测试数据,LMX1204在6GHz输出时表现优异:

| 参数 | 典型值 | 条件 |

|---|---|---|

| 相位噪声(10kHz偏移) | -154dBc/Hz | 缓冲模式 |

| 附加抖动(12k-100MHz) | 5fs RMS | 缓冲模式 |

| 二次谐波抑制 | <-25dBc | 6GHz输出,差分驱动 |

| 输出-输出偏移 | <15ps | 任意两路输出间 |

六、设计注意事项

-

缓冲器

+关注

关注

6文章

2100浏览量

47679 -

分频器

+关注

关注

43文章

500浏览量

51613 -

四路输出

+关注

关注

0文章

2浏览量

5863 -

评估模块

+关注

关注

0文章

1498浏览量

8100 -

EVM

+关注

关注

3文章

1032浏览量

42617

发布评论请先 登录

倍频器分频器与混频器相噪恶化公式,请问100KHz处相位噪声-115dBc/Hz过了二分频器或二倍频器后100KHz处相噪为多少?

ADI发布新款时钟缓冲器和分频器IC AD9508

对混频器、倍频器和分频器的异同点进行简单描述和选型

Texas Instruments LMX1205 JESD缓冲器/乘法器/除法器数据手册

?LMX1205 低噪声高频JESD缓冲器/乘法器/分频器技术文档摘要

LMX1204低噪声高频JESD缓冲器/倍频器/分频器技术解析

LMX1204低噪声高频JESD缓冲器/倍频器/分频器技术解析

评论