Texas Instruments LMX1205 JESD缓冲器/乘法器/分频器具有高频能力、极低抖动以及可编程时钟输入和输出延迟。得益于以上特性,该器件非常适用于时钟高精度高频数据转换器,且不会降低信噪比。四个高频时钟输出和具有较大分频器范围的额外LoICLK输出均与SYSREF输出时钟信号配对。用于JESD204B/C接口的SYSREF信号可以作为输入通过或内部生成,并重新计时到器件时钟。高频时钟输入和单独时钟输出路径的输入路径上的无噪声延迟调整可确保多通道系统中的低偏移时钟。对于数据转换器时钟应用,时钟抖动小于数据转换器的孔径抖动至关重要。在需要计时超过四个数据转换器的应用中,可以使用多个器件开发各种级联架构,分配所需的所有SYSREF信号和高频时钟。Texas Instruments LMX1205与超低噪声参考时钟源结合使用时,非常适用于时钟数据转换器,尤其是在高于3GHz时。

数据手册:*附件:Texas Instruments LMX1205 JESD缓冲器,乘法器,除法器数据手册.pdf

特性

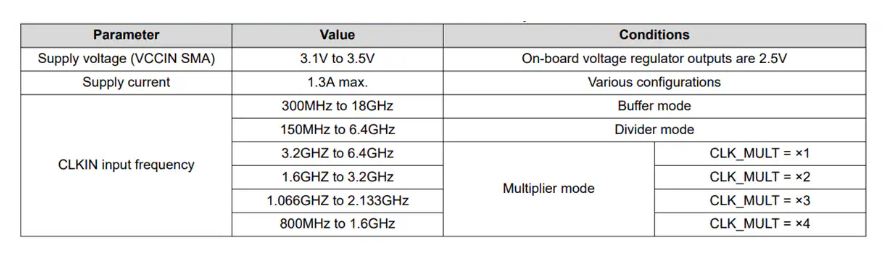

- 输出频率:300MHz至12.8GHz

- 无噪声可调输入延迟高达60ps,分辨率为1.1ps

- 独立可调输出延迟高达55ps,分辨率为0.9ps

- 四个具有相应SYSREF输出的高频时钟

- 共享1分频(旁路)、2、3、4、5、6、7和8

- 共享可编程乘法器x2、x3、x4、x5、x6、x7和x8

- 具有相应SYSREF输出的LOGICLK输出

- 在单独的分频器组上

- 1、2、4预分频器

- 1(旁路)、2、......、1023后分频器

- 第二个逻辑时钟选项,带额外分频器1、2、4和8

- 超低噪声

- 噪声基底:-159dBc/Hz(6GHz输出时)

- 附加抖动(直流至fCLK):36fs

- 附加抖动(100Hz至100MHz):10fs

- 六个可编程输出功率电平

- 同步SYSREF时钟输出

- 508个延迟步进调整,在12.8GHz时小于2.5ps

- 发生器、中继器和中继器重时模式

- 系统参考请求引脚的窗口功能,以优化时序

- 针对所有分频和倍频器件的同步功能

- 工作电压:2.5V

- 工作温度:-40?C至85?C

应用

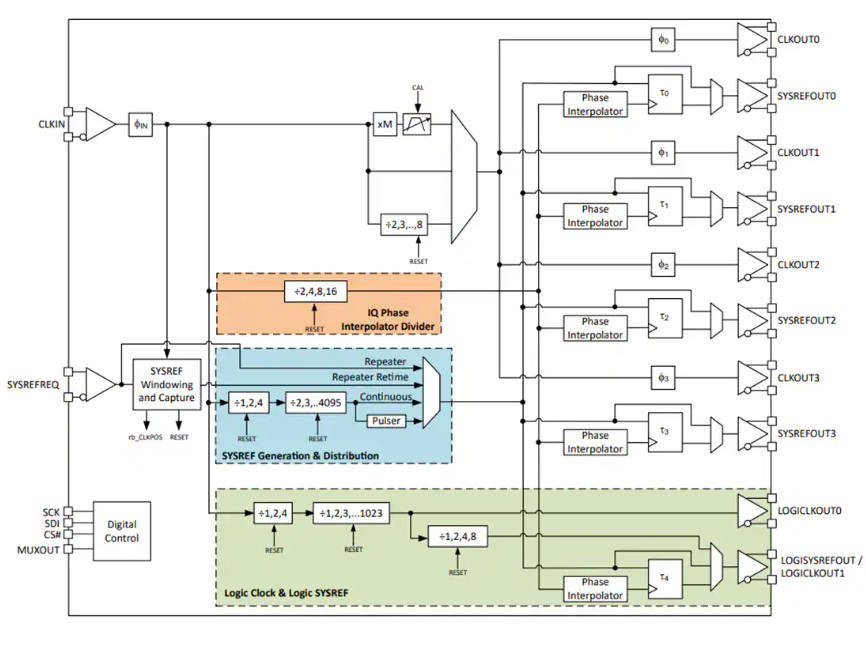

框图

-

缓冲器

+关注

关注

6文章

2065浏览量

47264 -

分频器

+关注

关注

43文章

493浏览量

51282 -

乘法器

+关注

关注

9文章

213浏览量

38030

发布评论请先 登录

求助,LMX2572LP参考时钟路径中的乘法器MULT的输入频率范围问题求解

并行除法器 ,并行除法器结构原理是什么?

MPY600 具有负载驱动功能的乘法器

使用verilogHDL实现乘法器

乘法器原理_乘法器的作用

CDCS503带可选SSC的时钟缓冲器/时钟乘法器数据表

Texas Instruments LMX1860SEPEVM评估模块数据手册

Texas Instruments LMX1205 JESD缓冲器/乘法器/除法器数据手册

Texas Instruments LMX1205 JESD缓冲器/乘法器/除法器数据手册

评论