01引言:先进封装设计的破局之路

随着“后摩尔时代”的到来,芯粒(Chiplet)与 2.5D/3D 先进封装技术正成为突破晶体管微缩瓶颈的关键路径。通过异构集成将不同的芯片模块化组合,依托2.5D/3D封装实现高带宽互连与低功耗协同,推动从芯片到系统级的性能飞跃。这为半导体技术发展带来重大机遇,也对传统设计方法构成全新挑战。在实际设计中,您是否正面临以下问题?

1先进封装设计困境

芯片间互联数量呈指数级增长,从芯片经通孔/Bump至基板的连线可达十几万根。手动布线作业量大,不仅耗时费力,还易因线路复杂导致视觉混淆与迭代困难。

2传统版图工具掣肘

大规模封装数据输入时,传统版图工具存在响应迟缓、操作卡顿等问题,直接影响设计效率。

3低效DFM需求处理困扰

面对Dummy填充、泪滴处理等 DFM(可制造性设计)需求,现有处理方式效率低下,无法满足生成制造量产的版图后处理需求。

4繁琐的验证流程

设计完成后,DRC/LVS 等物理验证流程复杂,需多次迭代,耗费大量时间与精力,延长项目周期。

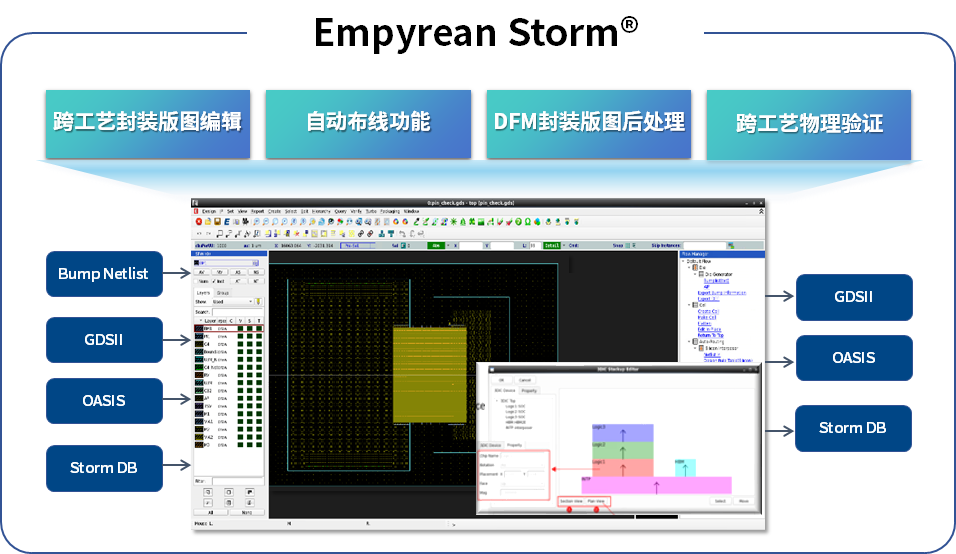

针对上述痛点,解决方案已正式推出。华大九天先进封装版图设计解决方案Empyrean Storm,作为一款具备革新意义的 EDA 工具,可直击传统封装设计核心问题,显著提升设计效率,推动先进封装设计进入新阶段!

02什么是Empyrean Storm?

Empyrean Storm是一款专为先进封装设计打造的具备自动布线与物理验证的版图平台。它支持跨工艺封装版图数据导入与设计编辑,深度适配当下主流的硅基(Silicon Interposer)以及有机转接板(Organic RDL)工艺,可实现 HBM和UCIe等通讯协议多芯片的大规模自动布线;同时能够完成Dummy填充等保障量产的DFM版图后处理,更是内置无缝集成的跨工艺物理验证Argus,通过DRC/LVS等检查确保版图的正确性。凭借上述强大功能,Storm能够轻松驾驭多芯片间大规模、高密度的互联布线和复杂的Layout需求,以高效的平台性能为先进封装设计注入强劲动力,助力设计工作实现质的飞跃。

核心亮点一:

强大智能的自动布线功能

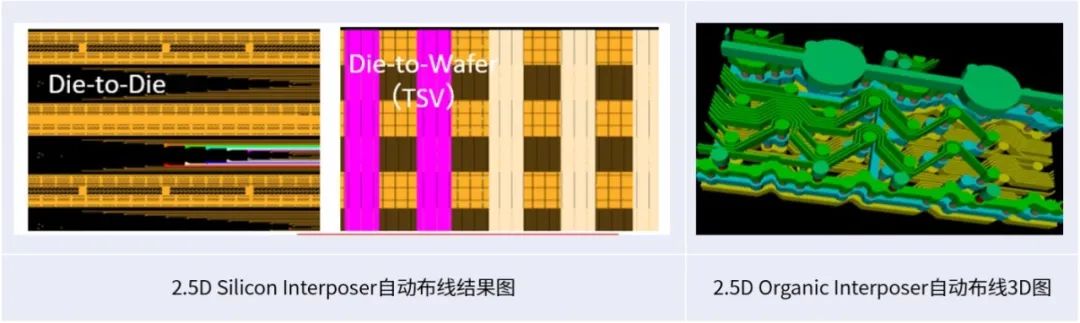

传统芯粒设计中,复杂布线是一大难点。以2.5D中介板(Interposer)的跨层布线为例,HBM2/2E/3高带宽存储器是面向高性能计算HPC、AI加速等场景的堆叠式DRAM技术,通过2.5D/3D集成提供超高带宽(如HBM3可达 819GB/s),但需通过硅中介层与处理器/SoC互联,布线密度高、信号完整性要求严苛。UCle通用芯粒互联接口标准,旨在实现不同工艺、厂商的Chiplet高效集成,支持高吞吐低延迟通信,但跨Die布线需协调时序、阻抗匹配,手动优化难度大。两者均为2.5D封装中的关键模块,但手工布线需处理几十万根高密度互连线,易导致串扰、时序违例等问题,而Storm搭载的智能化自动化布线引擎,可通过简单操作流程改变这一现状,用户仅需完成规则配置并触发指令,即可启动自动布线。其核心能力包括:

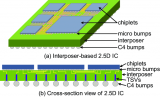

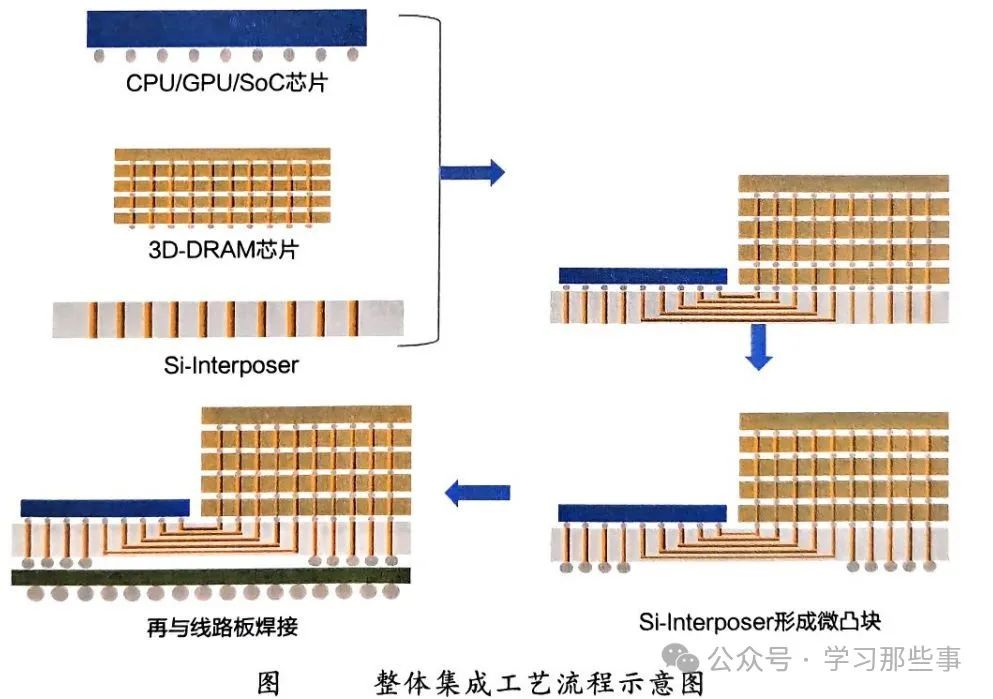

硅基中介层自动布线:依托智能算法支持从顶层Micro-Bump到底层C4 Bump的跨层布线,可高效完成多芯片间Die-to-Die、芯片到晶圆间Die-to-Wafer(含TSV硅通孔)的自动布线任务,精准规划芯片间、晶圆级与裸片级混合互联结构,保障信号传输稳定性。

有机中介层自动布线:通过优化垂直互连通道布局实现全局RDL高效布线,同时具备能够满足约束条件的电源网络(PDN)版图的自动布线功能。同时,为了更便捷地看到走线连接,Storm可生成三维布线图,直观呈现线路走向。

多样化布线角度适配:兼容芯片式曼哈顿布线与PCB式135度布线模式,能够精准匹配客户工艺标准,确保布线效率与准确性。

核心亮点二:

为量产护航的DFM版图后处理能力

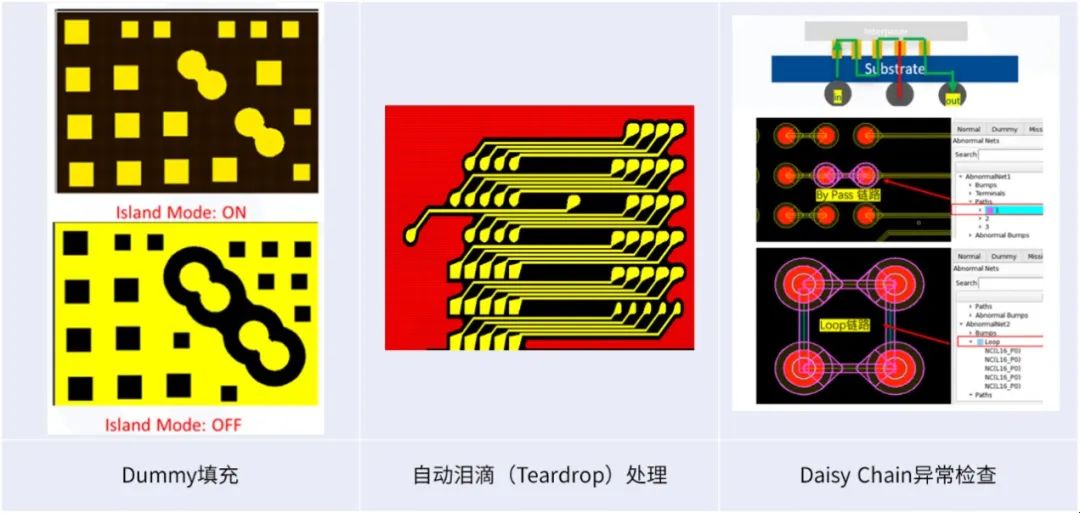

设计的最终目标是实现成功量产。Storm凭借完善的版图后处理功能,可有效提升设计的可制造性(DFM),为芯粒量产提供有力支持,具体包括:

智能金属哑元(Dummy)填充:能够自动、快速完成大面积Dummy填充,且支持特殊形状(例如Island不规则岛状)的填充。这一功能可解决工艺中的不均匀性问题,有助于提升晶圆制造的稳定性和芯片性能的一致性。

自动泪滴(Teardrop)处理:提供一键式操作,为焊盘和过孔精准添加泪滴,从而增强连接的可靠性,降低线路断裂风险,进而提升产品良率。

封装测试结构(Daisy Chain)模块:可自动完成封装测试结构的连接与分析,能够识别封装中Interposer、Substrate等结构的连接情况,分类展示Bumps、Terminals、Paths及Abnormal Bumps等信息。针对Bypass链路,可精准标记异常路径;对于 Loop链路,能清晰罗列关联节点,帮助工程师在芯片封装设计阶段快速定位异常并排查问题,提升设计可靠性。

核心亮点三:

不止于布线与后处理,更是一站式设计平台

Storm并非单一的布线与后处理工具,而是先进封装设计领域的综合性平台。其功能覆盖设计全流程,可提升设计流畅度并推动流程优化,具体包括:

全功能版图编辑:传统EDA工具在导入多个GDSII文件时,会出现同图层覆盖问题,导致无法区分Die1,Die2,在异构集成场景中效率低下。Storm平台可以支持多个GDSII/OASIS数据无损导入导出,创新性研发出针对封装版图的层次化(hierarchy)编辑设计功能,突破传统工具仅支持扁平化(Flatten)封装版图编辑模式、难以快速批量修改封装版图的局限。同时Storm支持直观形象的3D堆叠Stack显示、编辑与快速查询功能,形成完整的异构版图集成解决方案。

实时分析与检查:在沿用传统2D操作习惯的基础上,Storm平台创新性地提供了多工艺节点跨芯片线网追踪(Trace)功能,设计师通过点击、拖拽等简单操作,即可实现快速追踪跨芯片关键线网走向,清晰呈现信号传输路径,可在版图绘制阶段提前检查信号连通性与短路风险,推动设计左移。此外,平台具备封装测试结构(Daisy Chain)异常检查等功能,能在设计阶段及时发现问题,降低后期修改成本。

无缝集成验证工具:与华大九天物理验证工具Empyrean Argus实现无缝集成,能够提供快速的Online DRC以及开/短路检查,也同时提供Signoff级别的DRC/LVS,覆盖从设计到验证的全流程,保障版图正确性,缩短迭代周期,提升设计效率。

改版数据比对:通过同步视图端口实现高效版本差异对比,借助双版本同步透视可并列显示改版前后的布局/GDS 视图,自动高亮差异区域,支持跨工艺库参数比对;点击差异标记可即时跳转至对应层级,实现变更点的快速识别与动态定位。

03Empyrean Storm 平台带来的价值

华大九天版图设计解决方案Empyrean Storm平台在先进封装设计中优势显著。

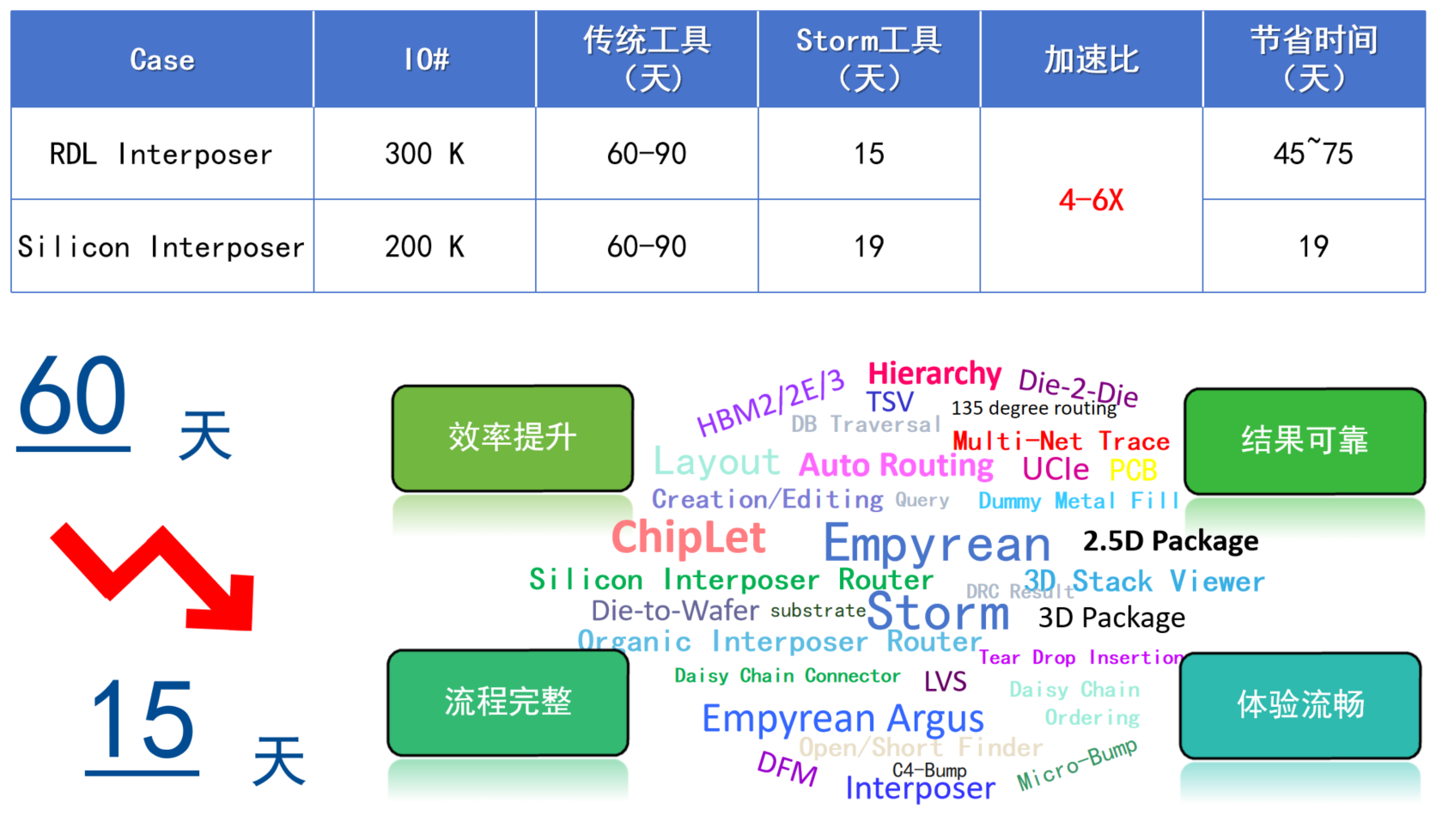

例如,在处理HBM2/2E/3与UCle等高速接口时,传统工具需耗时约两三月、60-90天之久,而Storm的自动布线引擎可在15天内完成IO数量高达200K的Micro-bumps与TSV跨层走线。该平台能高效处理TSV布线、微凸点(Microbumps)连接及BGA球栅阵列布局,同时支持中介层+基板的物理验证,并兼容CoWoS(Chip on Wafer on Substrate,晶圆基底封装)架构。某客户案例显示,在完成工具参数Option设置后,自动布线功能仅需10分钟即可完成1次设计迭代,显著提升了反复修改的效率:“Storm有效解决了先进封装的设计瓶颈,效率提升1-2个月”。

04结语

在先进封装设计这一兼具机遇与挑战的前沿领域,若持续使用落后设计工具,将直接影响效率提升与创新突破。Empyrean Storm 凭借卓越的自动布线核心引擎、一站式设计平台的全面功能,以及保障量产的DFM特性,已成为顶尖设计公司的主流选择。目前,多家大型设计公司已通过 Storm 完成完整的先进封装版图设计并成功流片,其强大的版图处理能力也被众多封测 OSAT 厂商纳入标准流片TO(Tapeout流片)流程。风暴来袭,借助 Storm 平台的全方位功能为集成电路产业赋能,在先进封装创新赛道上提升竞争力,重塑全球半导体产业格局。

北京华大九天科技股份有限公司(简称“华大九天”)成立于2009年,一直聚焦于EDA工具的开发、销售及相关服务业务,致力于成为全流程、全领域、全球领先的EDA提供商。

华大九天主要产品包括全定制设计平台EDA工具系统、数字电路设计EDA工具、晶圆制造EDA工具、先进封装设计EDA工具和3DIC设计EDA工具等软件及相关技术服务。其中,全定制设计平台EDA工具系统包括模拟电路设计全流程EDA工具系统、存储电路设计全流程EDA工具系统、射频电路设计全流程EDA工具系统和平板显示电路设计全流程EDA工具系统;技术服务主要包括基础IP、晶圆制造工程服务及其他相关服务。产品和服务主要应用于集成电路设计、制造及封装领域。

华大九天总部位于北京,在南京、成都、深圳、上海、香港、广州、北京亦庄、西安和天津等地设有全资子公司,在武汉、厦门、苏州等地设有分支机构。

-

eda

+关注

关注

71文章

2950浏览量

178898 -

华大九天

+关注

关注

5文章

95浏览量

13419 -

chiplet

+关注

关注

6文章

463浏览量

13072 -

先进封装

+关注

关注

2文章

483浏览量

682 -

芯粒

+关注

关注

0文章

70浏览量

302

原文标题:全球首发!先进封装设计平台Storm横空出世,Chiplet布线效率提升1-2月 !

文章出处:【微信号:华大九天,微信公众号:华大九天】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

华大九天“芯聚九天”系列活动助力集成电路产业蓬勃发展

多芯粒2.5D/3D集成技术研究现状

芯原推出面向可穿戴设备的超低功耗OpenGL ES GPU,支持3D/2.5D混合渲染

华大九天ALPS模拟仿真器的Snapshot功能解析

2.5D集成电路的Chiplet布局设计

华大九天推出PowerMOS版图自动化工具

最全对比!2.5D vs 3D封装技术

显示体验升级:2.5D GPU技术逐渐成为标配,3D GPU加码可穿戴

深入剖析2.5D封装技术优势及应用

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm

评论