以下文章来源于学习那些事,作者小陈婆婆

2.5D封装

关于2.5D封装的关键工艺,特别是凸块制作技术,我们可以进一步详细阐述如下:

封装关键工艺概述

铜柱凸块简介及关键工艺分析

金凸块(Au-Bump)工艺

1封装关键工艺概述

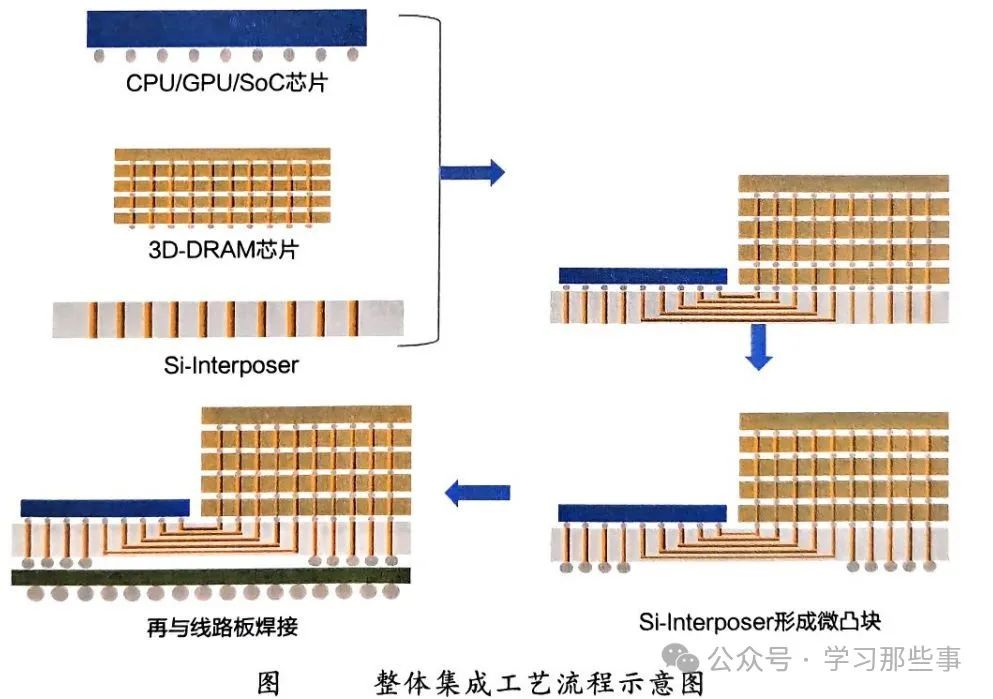

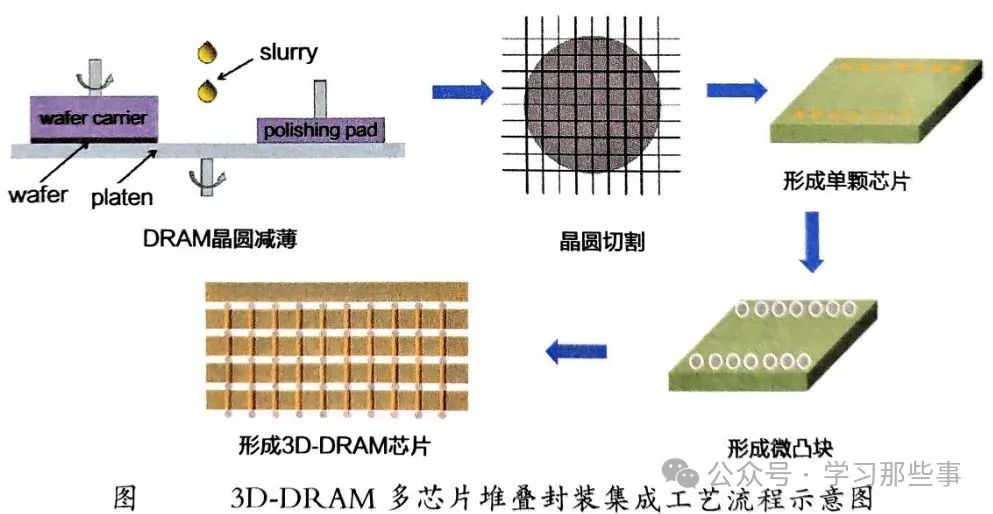

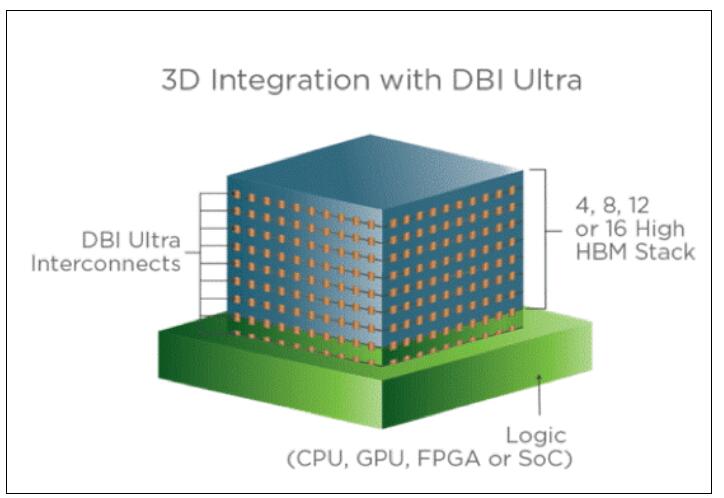

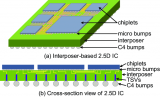

2.5D封装工艺是一种先进的半导体封装技术,它通过中介层(Interposer)将多个功能芯片在垂直方向上连接起来,从而减小封装尺寸面积,减少芯片纵向间互连的距离,并提高芯片的电气性能指标。这种工艺的关键步骤包括形成3D-DRAM芯片集成、形成Si-Interposer,以及将芯片与Si-Interposer集成。

凸块是在倒装芯片或带TSV(硅通孔)的多个部件之间叠加焊接所需的焊盘上添加的凸点。它在2.5D和3D封装工艺中扮演着至关重要的角色,因为它提供了芯片与中介层或线路板之间的电气连接。

凸块制作的主要方法

电镀法:电镀法是目前应用最广泛的凸块制作方法。它通过在镀液中施加电流,使金属离子在镀件表面还原沉积形成金属镀层。电镀法可以制作尺寸小、生产效率高、可靠性好的凸块。

化学镀法:化学镀法是一种无电解的镀金属过程,它利用还原剂将溶液中的金属离子还原成金属原子并沉积在镀件表面。这种方法适用于复杂形状和难以电镀的部件。

蒸发法:蒸发法是通过加热金属使其蒸发,然后在镀件表面冷凝形成金属镀层。这种方法适用于制作高纯度和高附着力的凸块。

锡膏印刷法:锡膏印刷法是将含有金属颗粒的锡膏通过印刷方式涂覆在焊盘上。这种方法适用于大规模生产和自动化生产。

凸块制作技术的优点与挑战

优点:凸块制作技术提供了芯片与中介层或线路板之间的高可靠性电气连接;有助于减小封装尺寸和提高封装密度;凸块制作技术还可以提高芯片的散热性能。

挑战:凸块制作过程中需要精确控制凸块的高度、形状和位置;对于高密度封装,凸块之间的间距越来越小,这对制作精度提出了更高的要求;凸块制作过程中还需要考虑金属材料的选择、镀液的稳定性和环保性等问题。

2铜柱凸块简介及关键工艺分析

凸块制作技术是2.5D封装工艺中的关键步骤之一。通过选择合适的凸块制作方法和优化制作工艺参数,可以制作出高质量、高可靠性的凸块,从而满足2.5D封装对电气连接、封装密度和散热性能等方面的要求。

铜柱凸块的主要构成及作用

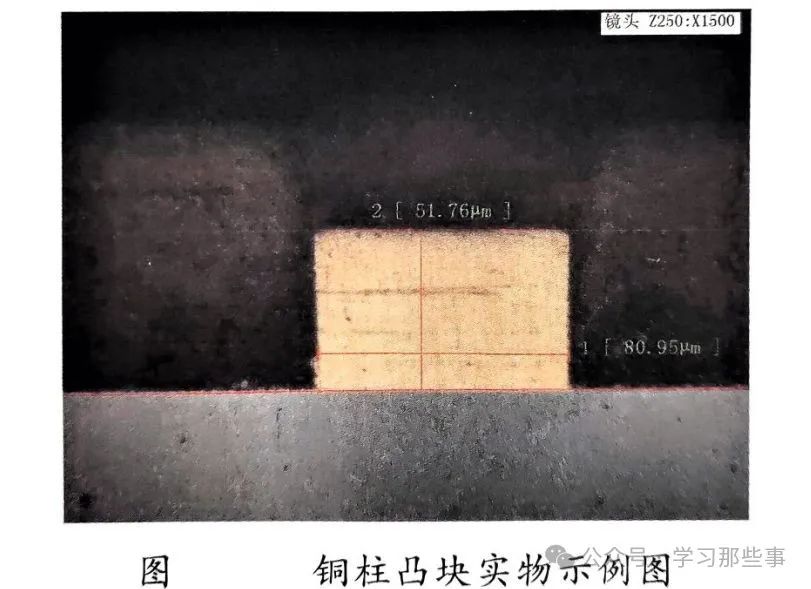

铜柱凸块主要由电镀铜柱、电镀镍阻挡层和电镀锡合金凸块三部分组成。

电镀铜柱提供良好的导电功能,镍层作为阻挡层防止铜和锡的扩散,而锡合金凸块则通过回流焊与其他部件进行焊接连通。

电镀铜柱的关键性能要求

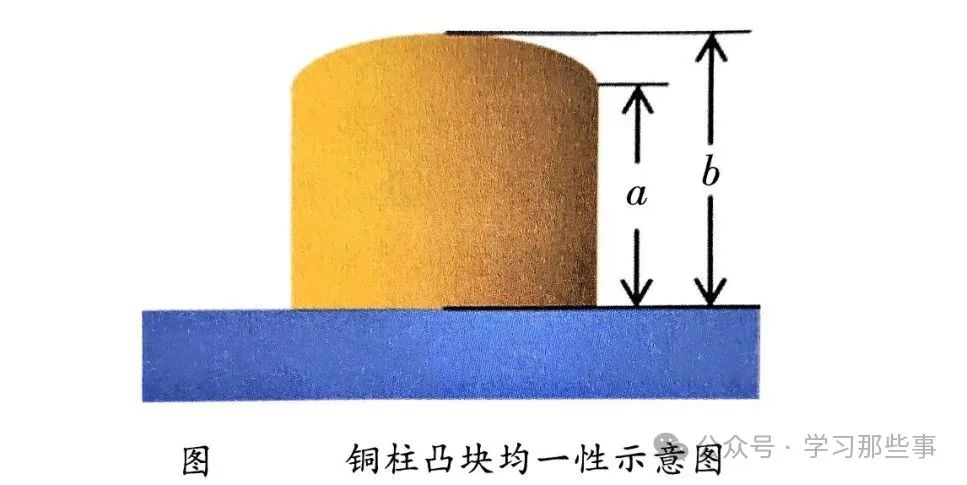

单颗铜柱的均一性:要求单颗铜柱的高度均匀性在±5%范围内,以确保凸块连接的稳定性和可靠性。

高电流密度操作能力:为了提高生产效率,电镀铜柱需要具备在高电流密度(如10ASD以上)下稳定操作的能力。这要求电镀液和设备具有较高的铜离子补充能力和药水运动能力。

是否需要电镀镍:根据产品要求决定是否需要电镀镍作为阻挡层。无镍阻挡层时,需确保铜柱和锡凸块老化后不会出现柯肯达尔空洞(KV)缺陷。

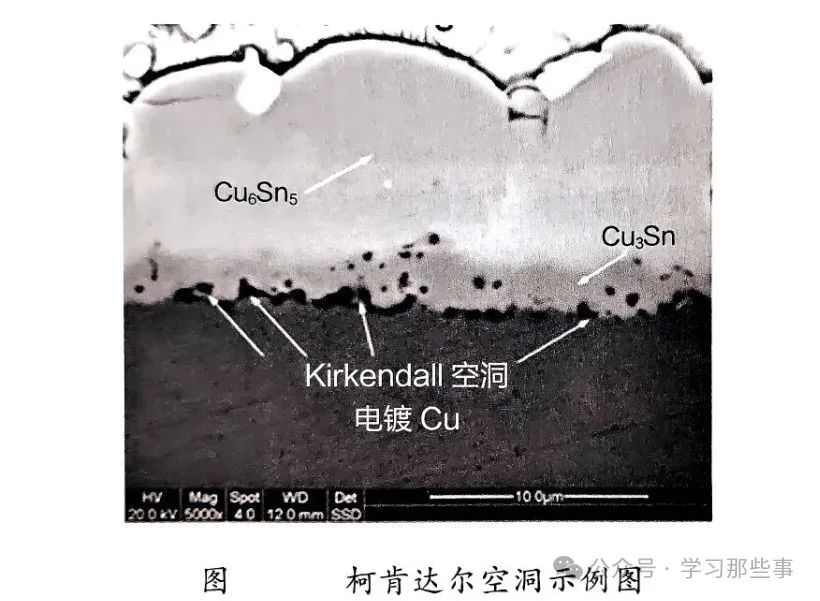

柯肯达尔空洞(KV)的影响及消除措施

柯肯达尔空洞是铜柱和锡凸块之间界面层出现的一种空洞缺陷,会严重影响凸块连接的电学和力学可靠性。

KV与铜镀层结晶有很大关系,合适的电镀溶液和工艺参数是消除KV的关键。通过调整电镀溶液中的卤素、硫化物浓度等参数,可以优化铜柱的晶粒大小,从而减少或消除KV。

电镀镍阻挡层的作用及特殊情况

电镀镍一般作为阻挡层使用,其厚度为2~5微米,可以大幅降低铜和锡合金凸块之间的扩散。然而,在特殊应用场合,如担心镍层对半导体器件性能的影响时,会拒绝使用镍镀层。此时,需要采取其他措施来防止铜和锡的扩散。

电镀锡银凸块的无铅化趋势

电镀锡银凸块是目前电镀凸块工艺中最主要的镀种之一,其银含量通常在1.8%±0.5%范围内。随着环保意识的提高,无铅化成为凸块工艺的重要趋势。然而,焊料合金中存在的容易发生阿尔法衰变的重金属元素(如铅、铋等)会引起半导体器件的单粒子效应,导致数据丢失、功能中断等危害。因此,在凸块工艺中需要关注焊料合金的阿尔法射线问题,并采取相应措施来降低其影响。

铜柱凸块作为倒装芯片技术中的关键组成部分,其性能和质量对半导体器件的可靠性和性能具有重要影响。通过优化电镀铜柱的工艺参数和溶液配方、选择合适的阻挡层材料、关注焊料合金的阿尔法射线问题等措施,可以进一步提高铜柱凸块的质量和可靠性。随着半导体技术的不断发展,铜柱凸块工艺将继续向着更高密度、更高性能的方向发展。

3金凸块(Au-Bump)工艺

金凸块是指在芯片的焊盘上通过电镀或其他技术形成的微小金属凸点,这些凸点作为芯片与封装基板之间电路导通的桥梁。

除了单纯的金凸块外,还有铜镍金凸块等衍生结构,它们以铜、镍取代一部分的金,以提高凸块整体硬度,降低与基板结合受力而变形的风险,同时减少金的用量和降低成本。

性能特点

导电、导热能力强:金凸块具有优秀的导电和导热能力,能够确保芯片与封装基板之间稳定而高效的信号传输和热量传递。

硬度高:通过添加铜、镍等元素,金凸块的硬度得到提升,从而增强了其在使用过程中的稳定性和可靠性。

抗氧化能力强:金具有良好的抗氧化性能,能够保护凸块免受氧化腐蚀的影响,延长使用寿命。

尺寸小、密度高:金凸块的尺寸通常很小,且能够在有限的空间内实现高密度的电路连接,满足现代电子产品对小型化和高性能的需求。

金凸块主要应用于以下领域:

显示器驱动芯片:金凸块是显示驱动芯片封测核心量产工艺之一,其市场需求随着手机、电脑等终端市场的快速发展而不断增加。

射频芯片:在射频芯片封装中,金凸块能够提供稳定的电路连接和信号传输,确保射频信号的准确性和稳定性。

摄像头芯片:摄像头芯片对电路连接的稳定性和信号传输的质量要求较高,金凸块能够满足这些要求,因此被广泛应用于摄像头芯片的封装中。

指纹识别系统:指纹识别系统需要高精度的电路连接和信号传输,金凸块以其优异的性能成为指纹识别系统封装的优选方案。

金凸块的电镀工艺流程通常包括以下几个步骤:

清洗:使用等离子体等技术清洗晶圆表面,去除有机物、氧化物等污染物,为后续的沉积过程提供一个干净、无污染的基底。

溅射:在清洗后的焊盘上沉积一层钛钨(TiW)作为粘附层,再沉积一层金(Au)作为种子层,为后续的电镀工序提供导电通道。

涂布光刻胶:在晶圆表面涂布一层较厚的光刻胶,其厚度设计需高于最终金凸点的高度。

光刻:通过曝光、显影等步骤,将设计好的电路图案转移到光刻胶上,露出需要电镀的部分。

电镀:在已暴露的金属区域进行电镀,沉积一层金形成微小的金属凸点。

剥离光刻胶:去除晶圆表面的光刻胶,暴露出底层的钛钨/金层。

刻蚀:使用湿法刻蚀工艺去除未覆盖电镀层的多余钛钨和金层,保留已经形成的金凸点。

退火:通过退火处理使电镀的金凸点结构更加坚硬,提高机械强度和稳定性。

-

芯片

+关注

关注

460文章

52624浏览量

442788 -

半导体

+关注

关注

335文章

29039浏览量

240321 -

封装技术

+关注

关注

12文章

580浏览量

68657 -

2.5D封装

+关注

关注

0文章

24浏览量

362

原文标题:2.5D封装的关键工艺详述

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

研发的铜混合键合工艺正推动下一代2.5D和3D封装技术

2.5D封装应力翘曲设计过程

深入剖析2.5D封装技术优势及应用

2.5D封装的热力挑战

SK海力士考虑提供2.5D后端工艺服务

2.5D封装为何成为AI芯片的“宠儿”?

一文详解2.5D封装工艺

一文详解2.5D封装工艺

评论