完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

标签 > chiplet

chiplet是什么意思?chiplet国内公司有哪些?chiplet关键技术在哪里?chiplet对行业的优劣怎么评估? chiplet工艺和chiplet和SoC区别分析,这里一文读懂chiplet!

chiplet 的概念其实很简单,就是硅片级别的重用。设计一个系统级芯片,以前的方法是从不同的 IP 供应商购买一些 IP,软核(代码)或硬核(版图),结合自研的模块,集成为一个 SoC,然后在某个芯片工艺节点上完成芯片设计和生产的完整流程。

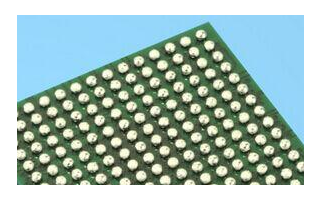

很多的行业大佬都把chiplet 看成是未来芯片的重要基础技术。简单来说,chiplet 技术就是像搭积木一样,把一些预先生产好的实现特定功能的芯片裸片(die)通过先进的集成技术(比如 3D integration)集成封装在一起形成一个系统芯片。而这些基本的裸片就是 chiplet。从这个意义上来说,chiplet 就是一个新的 IP 重用模式。未来,以 chiplet 模式集成的芯片会是一个“超级”异构系统,可以为 AI 计算带来更多的灵活性和新的机会。

chiplet 的概念最早来自 DARPA 的 CHIPS(Common Heterogeneous Integration and IP Reuse Strategies)项目。该项目试图解决的主要问题如下“The monolithic nature of state-of-the-art SoCs is not always acceptable for DoD or other low-volume applications due to factors such as high initial prototype costs and requirements for alternative material sets. To enhance overall system flexibility and reduce design time for next-generation products, the Common Heterogeneous Integration and Intellectual Property (IP) Reuse Strategies (CHIPS) program seeks to establish a new paradigm in IP reuse.”。而它的愿景是:“The vision of CHIPS is an ecosystem of discrete modular, reusable IP blocks, which can be assembled into a system using existing and emerging integration technologies. Modularity and reusability of IP blocks will require electrical and physical interface standards to be widely adopted by the community supporting the CHIPS ecosystem. Therefore, the CHIPS program will develop the design tools and integration standards required to demonstrate modular integrated circuit (IC) designs that leverage the best of DoD and commercial designs and technologies.” 从这段描述来看 chiplet 可以说是一种新的芯片设计模式,要实现 chiplet 这种新的 IP 重用模式,首先要具备的技术基础就是先进的芯片集成封装技术。

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

在摩尔定律逐渐放缓的背景下,Chiplet(小芯片)技术和3D封装成为半导体行业突破性能与集成度瓶颈的关键路径。然而,随着芯片集成度的提高,气泡缺陷成为...

奇异摩尔荣获2025中国创新IC强芯-创新突破奖,助力国产化芯片技术突破

7月11日,2025年度中国创新IC-强芯奖颁奖典礼在ICDIA创芯展上揭晓获奖名单。 奇异摩尔申报的Kiwi 3D Base Die产品从申报的142...

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布扩大与三星晶圆代工厂的合作,包括签署一项新的多年期 IP 协议,在三星晶圆代工厂的...

7月15日,由“集成芯片前沿技术科学基础”重大研究计划指导,中国科学院计算技术研究所、中国电子科技集团公司第五十八研究所主办的第三届芯粒开发者大会即将在...

专家对话:新思科技×无问芯穹 AI与EDA的双向赋能,重构芯片设计,破局算力瓶颈

2025年5月23日,新思科技直播间邀请到清华大学电子工程系博士、博士后曾书霖(无问芯穹001号员工)、无问芯穹智能终端技术总监胡杨,以及新思科技战略生...

Cadence携手台积公司,推出经过其A16和N2P工艺技术认证的设计解决方案,推动 AI 和 3D-IC芯片设计发展

同时宣布针对台积公司 N3C 工艺的工具认证完成,并基于台积公司最新 A14 技术展开初步合作 中国上海,2025 年 5 月 23 日——楷登电子(美...

从产业格局角度分析Chiplet技术的战略意义,华芯邦如何通过技术积累推动中国从“跟跑”到“领跑”。

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | abg欧博DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |