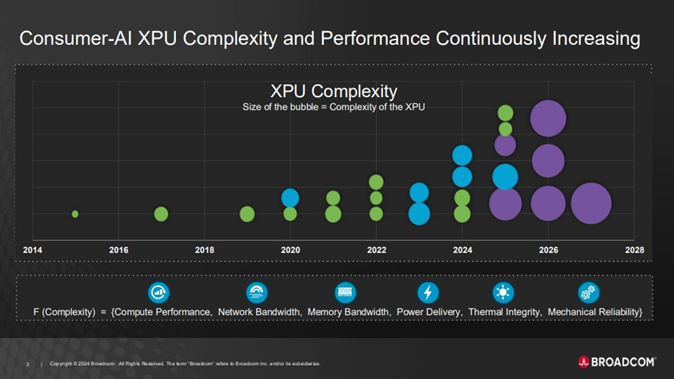

2025年又是充满无限可能的一年。开年之际,DeepSeek事件以燎原之势席卷全球,再次印证了AI时代"一切皆有可能"的黄金法则。人工智能行业对计算的需求变革几乎每天都在上演。从半导体的终端需求出发,芯片供给端正在经历一场根本性的架构变革。在这场变革中,3D Chiplet异构集成技术逐步崭露头角,走向更广阔的舞台。

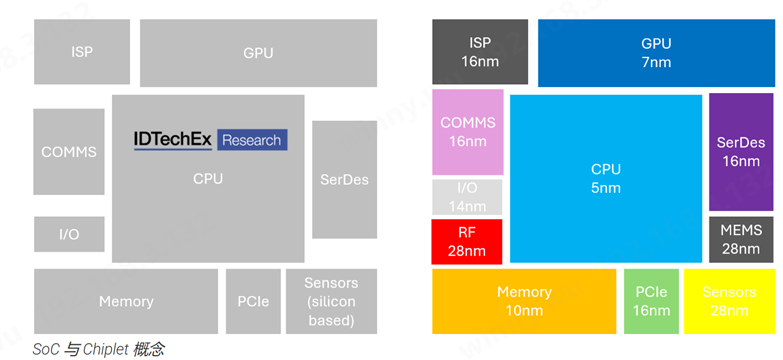

我们知道受制于最大光刻面积的限制,单芯片的面积无法无限制扩展。为此,需采用多次曝光拼接技术,这大幅增加了工艺难度,导致芯片良率显著下降。面对晶体管数量持续增长与芯片横向面积扩展受限的矛盾,Chiplet芯粒技术应运而生。

(来源:IDTechEx )

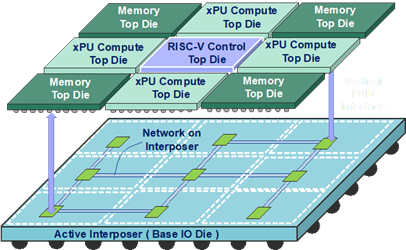

3D IC技术展现出了“超越摩尔定律”的巨大潜力,被视为后摩尔时代突破SoC集成度、性能等瓶颈的关键所在。通过3D IC 芯粒架构,多个同质和异质的小芯片/裸片得以在垂直尺度上整合于同一设计之中,这不仅提升了芯片的功能密度和单位性能,还增强了设计灵活性,同时降低了开发成本。典型的3D IC制造技术包括台积电的 3D Fabric(SoIC)、 英特尔的Foveros、三星的X-Cube、日月光的VIPack 3D IC 等;从芯片最终商用角度来说,AMD MI300 GPU及Ryzen系列处理器;Intel 的Meteor Lake、Lunar Lake都是3D IC多芯粒堆叠的代表性案例。

(图:3DIC Architecture)

AI时代驱动下的3D IC 应用趋势

AI网络加速CPO Chiplet部署进程

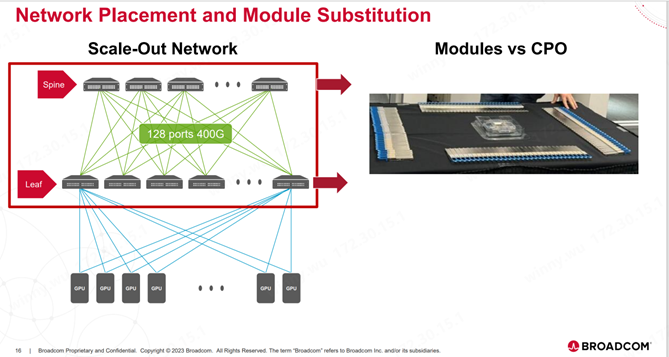

在AI高速发展的背景下,硅光集成凭借高速率+低功耗的优势,有望成为数据中心互连的重要方案之一。作为一种新型光电子集成技术,CPO通过将光引擎与交换芯片近距离互连,缩短光信号输入和运算单元间的电学互连长度。其优势包括:高带宽密度、低功耗、高集成度、低延时、小尺寸,并可通过半导体制造技术实现规模化生产。

报告大摩近期的报告预测,随着英伟达Rubin服务器机架系统在2026年开始量产,CPO市场规模将在2023-2030年间以172%的年复合增长率扩张,预计2030年达到93亿美元;在乐观情景下,年复合增长率可达210%,市场规模将突破230亿美元。

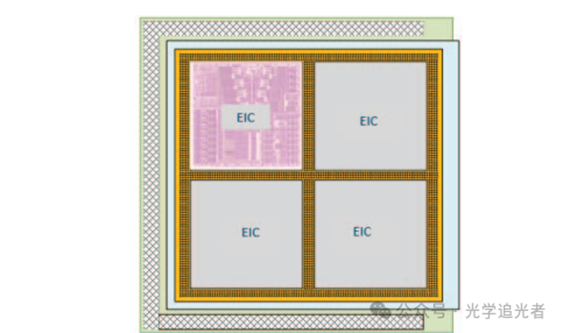

去年IEEE ECTC 2024上,Cisco公布了其基于3D封装的3.2Tbs 光学引擎的技术细节,该技术集成了光子集成电路 (PIC) 和电气 IC (EIC),使用晶圆级再分布层 (RDL) 实现紧凑的设计和低寄生电气连接。

(来源:光学追光者公众号)

上图为4个800G EIC和1个3.2T PIC的封装顶视图,达到3.2Tb总带宽,EIC互联使用RDL层,PIC bump倒贴在FPOP上,使用边缘耦合FAU光学封装,EIC通过RDL连接到PIC bump上,EIC周围和中间高的铜柱将顶部RDL和底部RDL连接到一起。

AI网络Scale-out主要通过高速互联容纳更多节点,进而提升集群整体算力规模。当前机间通信主要以 400G-800G 为主,未来有望通过更高速率如 1.6T 组网互联,以提高互联带宽,支持更多节点高速互联;采用 CPO (Co-Packaged Optics) /NPO (Near Packaged Optics)、多异构芯片 C2C (Chip-to-Chip)封装等方式降低延时,进而提升数据传输效率。

(来源:Broadcom)

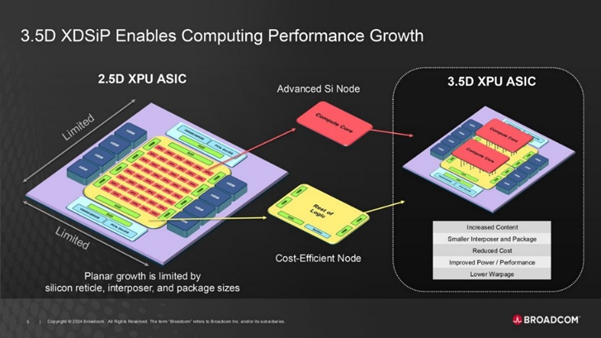

博通引领多芯片设计转向 3.5D 封装技术

2024年年底,Broadcom 推出了其 3.5D eXtreme Dimension 系统级封装 (3.5D XDSiP) 平台,该平台适用于 AI 和 HPC 工作负载的超高性能处理器。新平台依赖于 TSMC 的 CoWoS 和其他先进封装技术。它使芯片设计人员能够构建 3D 堆栈逻辑、网络和 I/O芯粒片以及 HBM 内存堆栈的系统级封装 (SiP)技术。

(来源:Broadcom)

博通计划将系统核心中的加速器核心或其他处理单元(如上图红色部分所示)划分为任意数量的硅片。这些逻辑芯片可以包含通用 CPU 核心或高性能 AI 加速器,从 GPU 到张量处理单元 (TPU),或其他定制模块。其余逻辑被重新安置在一个单独的芯片上,在图中以黄色显示,其中包含从 I/O(包括基于PHY 的芯片间互连、高速 SerDes 和 HBM 内存接口)到充当处理器缓存的 SRAM 的所有内容。 这种设计方式同样让计算逻辑Die与I/O芯粒等其他模块实现解耦,从而使用各自适用的相关工艺节点来实现更高性能和更佳的制造性价比。

“

简单的来说,红色部分称作为计算Die ,而下面黄色的部分称作3D Base Die,该芯粒可以包含各种I/O所需接口。这种设计方式让计算Die与I/O芯粒等其他模块实现解耦,从而使用各自适用的相关工艺节点来实现更高性能和更佳的制造性价比。运用3D Base Die作为3D IC 芯片的I/O基础芯粒的架构设计已经成为AI时代异构芯片发展可预见的创新趋势。

博通使用混合键合将上面较小的计算Die模块堆叠在较大的Base芯片上,以实现连接和存储。通常,芯片之间使用硅通孔 (TSV) 相互通信,这些硅通孔充当 3D 堆栈内的电梯井,在它们之间传输电力、信号和数据。而整个芯片的外围,环绕着六个 HBM 模块,采用了台积电先进的工艺节点和 CoWoS 技术进行 2.5D 封装。

(来源:Broadcom)

然而,随着生成式AI模型的计算需求指数级增长,2.5D方案的带宽和功耗限制变得愈发明显。3.5D技术的出现,通过在封装内堆叠更多的芯片模块,实现了性能、功耗和成本的最佳平衡。3.5D 集成技术通过将 3D 硅堆叠与 2.5D 封装相结合,能够在不单纯依赖制程工艺提升的情况下,实现芯片性能的显著提升、功耗的有效降低以及成本的合理控制,从而成为了下一代 XPU 发展的必然趋势。

国内存算一体3D IC 案例实现工艺节点效能突破

随着AI高性能计算、自动驾驶等进入行业爆发期,巨大的算力催生了新的计算架构。由于芯片内数据提取与传输的需求日益增长,“存储墙”成为了数据计算应用的一大障碍。深度学习加速的最大挑战就是数据在计算单元和存储单元之间频繁的移动。

存算一体芯片技术的创新在很大程度上解决了芯片内不必要的数据搬移的延迟与功耗消耗,提升百倍千倍的AI计算效率,尤其是国内三维存算一体芯片的诞生将打破仅限于Intel与AMD等国际芯片企业在3DIC领域的垄断地位。

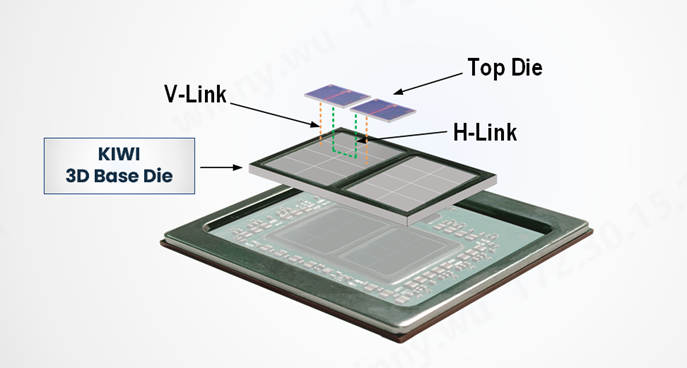

2024年,奇异摩尔与复旦大学共同打造的三维存算一体芯片通过3D三维集成堆叠芯粒的形式实现晶体管密度等效2倍的提升,另一方面又实现了存储与计算的紧耦合从而实现了高能效、降低存储墙的性能。这款芯片利用3D封装工艺加成存算一体技术仅使用28nm工艺就可以达到8/7nm工艺性能。在规避地缘政治管控的同时,实现先进工艺节点,成就高性能芯片。奇异摩尔自创立以来从片内互联着手,不断深耕Chiplet赛道,是国内首批布局3D Base Die互联芯粒的科创企业。凭借在有源基板3D Base Die的设计能力以及先进封装方面的资源整合成功联合学术界实现三维存算一体芯片技术突破。(更多阅读:芯片界奥林匹克放榜 !奇异摩尔与复旦大学三维集成芯片成果入选ISSCC 2025)

(来源:奇异摩尔)

奇异摩尔的3D Base die(可理解为基于3D封装的I/O Die)可以把原本集成在SoC中的Power、SRAM、I/O等非数字功能模块拆分并拼搭进去,从而构成一个高度集成并节能的多核异构计算架构,同时实现上层的逻辑芯片面积最大化和芯片单位面积的最小化。在互联方面,3D Base Die支持水平方向和垂直方向的异构芯片互连。垂直方向,通过TSV、microbump等3D互连技术与顶层逻辑芯粒、substrate垂直通信,从而以最小限度实现die与die之间的互连、片外连接,显著提高芯粒集成密度,从而大规模提升芯片的算力。3D Base Die具有可复用功能,它与计算和存储等芯粒解耦,进一步满足存算一体芯片下一代技术的演进需求。

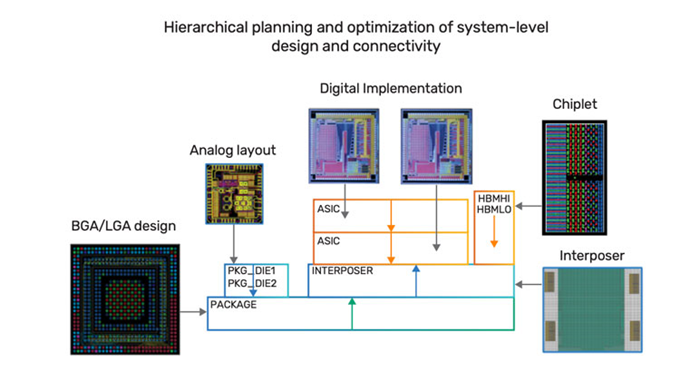

3D IC应用普及化的挑战

目前3D IC先进制造工艺技术仍旧掌握在少数企业手中,先进的节点工艺因为地缘政治的原因获取上存在挑战。从芯片制造本身来说,3D-IC的热管理与机械应力、互联、测试及相关材料的选择等一系列复杂问题还存在设计与与制造方面的挑战。此外,3D IC本身架构设计、EDA工具、封装设计等板块都具备复杂性和生态互通需求。设计人员需要要把这些必须具备的功能全部打通串联,形成协同作战,所以这是一个相对庞大的系统工程。

(来源:Cadence)

另一方面, 芯粒之间的互联互通一直是3D IC 通用化落地的一个关键。国际标准方面,UCIe2.0 标准在去年下半年正式发布,标准的升级让Chiplet生态又往前迈了一大步。UCIe 2.0解决了跨多个芯粒的 SiP 生命周期的可测试性、可管理性和调试 (DFx) 的设计挑战。此次更新的一个关键功能是支持 3D 封装,使芯粒能够显著提高带宽密度和功率效率。UCIe 2.0 通过标准化接口和管理架构,促进了开放 Chiplet 生态系统的发展。

UCIe 2.0 在国内的生态通用化程度还需要不断提高,尽管UCIe已经慢慢被国内芯片市场所接受,应用层面开始逐步出现落地案例。但仍然在芯粒协议、电源和热管理等方向需要进行标准化和优化。3D IC 的大规模落地需要产业链上下游协同来实现生态的共荣,从封测制造、跨领域技术融合、标准共建与统一化等多维度方向来构建协调矩阵。

奇异摩尔作为Chiplet互联的先行者将充分利用自身在3D IC设计与封装量产的经验资源与行业共赴这个价值万亿的产业新蓝海。当设计软件、材料科学、制造工艺、测试验证等18个关键环节形成共振,当3000家上下游企业构建起创新联合体,3D IC技术才能真正释放其颠覆性潜能。这不是零和博弈的战场,而是需要全行业以"硅基生命体"的共生理念,共同绘制半导体产业的下一个黄金时代。

关于我们AI网络全栈式互联架构产品及解决方案提供商

奇异摩尔,成立于2021年初,是一家行业领先的AI网络全栈式互联产品及解决方案提供商。公司依托于先进的高性能RDMA 和Chiplet技术,创新性地构建了统一互联架构——Kiwi Fabric,专为超大规模AI计算平台量

身打造,以满足其对高性能互联的严苛需求。

我们的产品线丰富而全面,涵盖了面向不同层次互联需求的关键产品,如面向北向Scale out网络的AI原生智能网卡、面向南向Scale up网络的GPU片间互联芯粒、以及面向芯片内算力扩展的2.5D/3D IO Die和UCIe Die2Die IP等。这些产品共同构成了全链路互联解决方案,为AI计算提供了坚实的支撑。

奇异摩尔的核心团队汇聚了来自全球半导体行业巨头如NXP、Intel、Broadcom等公司的精英,他们凭借丰富的AI互联产品研发和管理经验,致力于推动技术创新和业务发展。团队拥有超过50个高性能网络及Chiplet量产项目的经验,为公司的产品和服务提供了强有力的技术保障。我们的使命是支持一个更具创造力的芯世界,愿景是让计算变得简单。奇异摩尔以创新为驱动力,技术探索新场景,生态构建新的半导体格局,为高性能AI计算奠定稳固的基石。

-

芯片

+关注

关注

460文章

52736浏览量

444128 -

AI

+关注

关注

88文章

35758浏览量

282453 -

人工智能

+关注

关注

1810文章

49221浏览量

251538 -

chiplet

+关注

关注

6文章

465浏览量

13075

原文标题:Chiplet&互联专题:AI时代变革下 3D IC 芯粒技术的最新应用趋势解读

文章出处:【微信号:奇异摩尔,微信公众号:奇异摩尔】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

NVIDIA助力影眸科技3D生成工具Rodin升级

3D IC背后的驱动因素有哪些?

腾讯混元3D AI创作引擎正式发布

腾讯混元3D AI创作引擎正式上线

揭秘3D集成晶圆键合:半导体行业的未来之钥

中兴通讯携手中国移动推出AI裸眼3D创新产品

中兴通讯全场景AI终端应用与裸眼3D新品亮相

发掘3D文件格式的无限潜力:打造沉浸式虚拟世界

AI时代驱动下的3D IC应用趋势

AI时代驱动下的3D IC应用趋势

评论