来源:SERVUSTEK;作者:DR.X1

600-650V功率器件是Si SJ MOS(又称Si 超结MOS),SiC MOS和GaN HEMT竞争最为激烈的产品区间,其典型应用为高频高效高功率密度电力电子。通过对比分析Infineon,ST, ON, GaN Systems(已为Infineon收购)和Toshiba最新技术平台产品,本文梳理了Si SJ MOS,SiC MOS和GaN HEMT的个性,共性,以及相对定位。

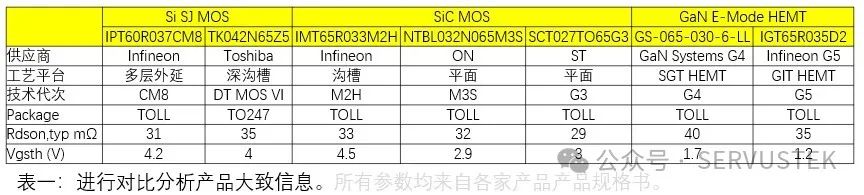

所选对比产品代表业界最新技术水平

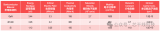

表一列出了进行对比分析的国际一线品牌产品。所选Infineon和Toshiba Si SJ MOS为其最新代次体二极管快恢系列。快恢技术平台对MOS体二极管进行了专门优化(如进行pt掺杂),从而显著降低Qrr,其性能更优应用范围更广,同时兼容软开关和硬开关拓扑。所选Infineon CM8典型导通电阻31mΩ,采用多层外延技术;Toshiba DTMOS VI采用深沟槽技术,典型导通电阻35mΩ;代表业界Si SJ MOS两个不同的技术路径。

SiC MOS Infineon M2H系列为沟槽MOS,导通电阻典型值33mΩ,ON M3S和ST G3系列为SiC平面MOS,导通电阻典型值分别为32和29mΩ。目前业界GaN有常开型(D-Mode)和常关型(E-Mode) HEMT(High Electron Mobility Transistor)两种技术路径。为减少对比复杂度,所选GaN HEMT为常关型纯单管。其中GaN Systems G4典型导通电阻40mΩ,Infineon G5导通电阻典型值35mΩ。

所选Toshiba DT MOS VI为TO247封装,其他产品为TOLL封装。封装形式对产品静态参数对比没有影响,对散热能力和开关速度等参数则有一定影响。进行对比时如涉及封装影响则不把Toshiba器件纳入对比。进行对比分析所有数据的原始出处来自产品规格书,从用户的视角来审视各个产品。

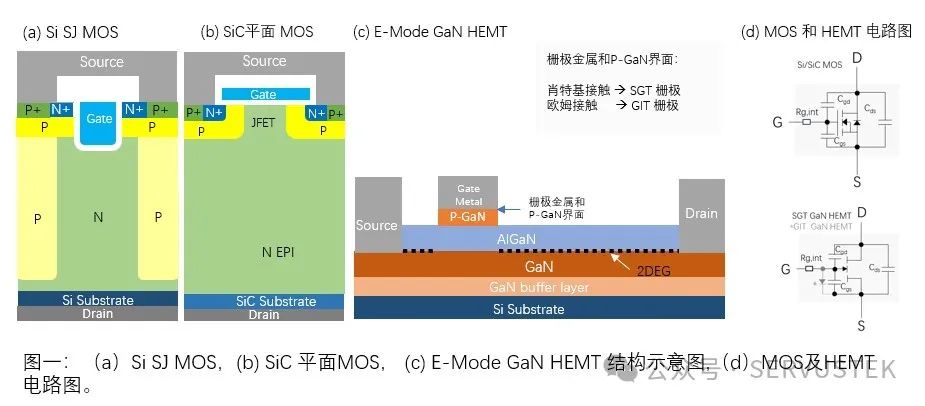

Si和SiC采用垂直型MOS结构,GaN采用水平型HEMT结构

Si SJ MOS和SiC MOS本质上是MOS,而GaN则采用HEMT结构来释放其材料优势。参见图一(a),Si SJ MOS其漂移层由周期性排列的高掺杂P-N-P柱组成,利用电荷补偿原理显著降低漂移层电阻。Si SJ MOS经多年发展技术相对成熟,业界主要通过多层外延和深沟槽来实现SJ结构。多层外延技术引领者英飞凌技术平台已演进到第八代(CM8),Toshiba则推动深沟槽技术的持续发展,其最新技术平台为DT MOS VI。图一(b)为SiC平面MOS结构示意图。目前业界最为成熟的是SiC平面MOS,沟槽MOS也在不断成熟和发展。SiC平面MOS的技术引领者为ON M3S和ST G3,SIC沟槽MOS的典型代表为Infineon和Bosch。

参见图一(c),由于无法在GaN上生长热氧化物,GaN功率器件采用了HEMT结构。AlGaN和GaN之间由于独特的能带特性在其界面处形成一层二维电子气,通过p-GaN可耗尽栅极下自由电子气,从而阻断沟道达到器件常关之目的。 根据p-GaN和栅极金属的接触形式,E-Mode GaN HEMT可以分为SGT (Schottky Gate Transistor) HEMT和GIT (Gate Injection Transistor) HEMT。Si SJ MOS和SiC MOS的源极和漏极分别在芯片的顶部和底部,为垂直型器件;而GaN HEMT的源极和漏极均在芯片的顶部,为水平型器件。

图一(d)为MOS和HEMT的电路示意图,HEMT相对于MOS的最大器件区别是HEMT没有体二极管,这使得GaN HEMT有双向耐压的独有潜力,双向沟道导电则是MOS和HEMT的共性。业界多年的工程研发已实现HEMT器件双向耐压和双向导电,且陆续有产品投向市场(非本文聚焦)。没有体二极管也让GaN HEMT无雪崩能力,一般通过提高GaN HEMT器件耐压典型值从而规避器件面临雪崩的可能性。

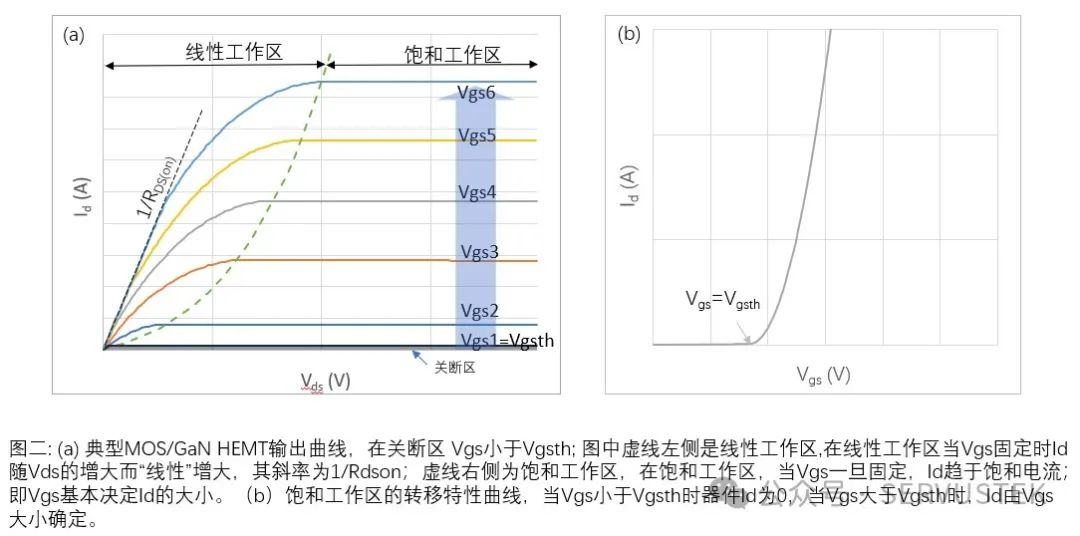

MOS和HEMT均有关断区,线性工作区,饱和工作区

图二(a)和(b)分别为MOS和HEMT的输出曲线和转移特性曲线。参见图二(a)MOS和HEMT有三个工作区间:关断区,线性工作区和饱和工作区。当Vgs小于Vgsth时沟道被关断,器件处于关断区。当Vgs大于Vgsth时(如为Vgs4),器件的导通电流Id一开始随Vds的增加而增加,此时器件处于线性工作区;当Vds增加到一定程度时Id逐渐趋于饱和电流,此时器件处于饱和工作区。

图二(b)为MOS和HEMT在饱和工作区的转移特性曲线,当Vgs大于Vgsth时,Id随Vgs的增大而迅速增大,且基本不受Vds的影响。转移特性曲线可以用来确定器件开关的米勒(Miller)平台电压。

在大部分应用中,器件在其漫长的生命周期要么处于关断区,要么处于线性工作区;器件硬开通时从关断区穿越饱和工作区进入线性工作区,而硬关断时从线性工作区穿越饱和工作区进入关断区。器件处于线性工作区时,栅极阈值电压Vgsth,推荐驱动电压,导通电阻Rdson,体二极管Vfsd等,是比较关键的静态参数。开关时的动态参数,如Ciss / Crss / Qgs / Qgd/ Qg, Coss / Eoss / Qoss,Qrr,开关时间及损耗,则比较关键。下面将对这些动静态参数进行对比,从而了解Si SJMOS,SiC MOS和GaN E-mode HEMT的异同。

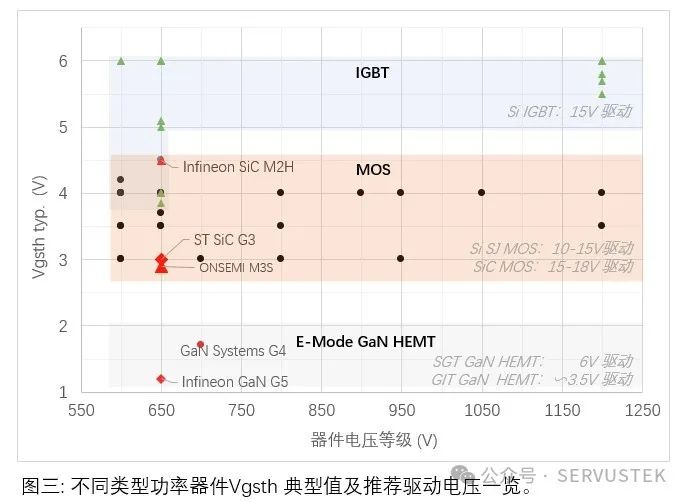

GaN HEMT Vgsth和推荐驱动电压相对较低,Si SJ MOS和SiC MOS适中

作为背景信息,图三给出600V – 1200V Si基IGBT和SJ MOS的Vgsth典型值。Si SJ MOS Vgsth一般位于3-4.5V之间。普通IGBT Vgsth一般为5-6V,针对电源类应用的IGBT Vgsth也可优化到4V左右。Si SJ MOS一般推荐10-15V驱动,而Si IGBT则推荐15V驱动。

沟槽型SiC MOS其Vgsth典型值为4-4.5V左右,SiC平面MOS Vgsth则介于2.7-3V之间。主流SiC平面和沟槽MOS均首推18V驱动且兼容15V驱动。GaN Systems G4采用SGT GaN HEMT结构,Vgsth典型值为1.7V,推荐驱动电压6V左右,Infineon G5 GaN为GIT HEMT结构,Vgsth为1.2V左右,推荐驱动电压3-3.5V。

考虑到GaN的高速开关特性,GaN HEMT的低Vgsth和推荐驱动电压给应用带来一定的挑战;SiC MOS则很好的和Si SJ MOS和Si IGBT相兼容,客户可相对容易从Si SJ MOS和Si IGBT过渡到SiC MOS。

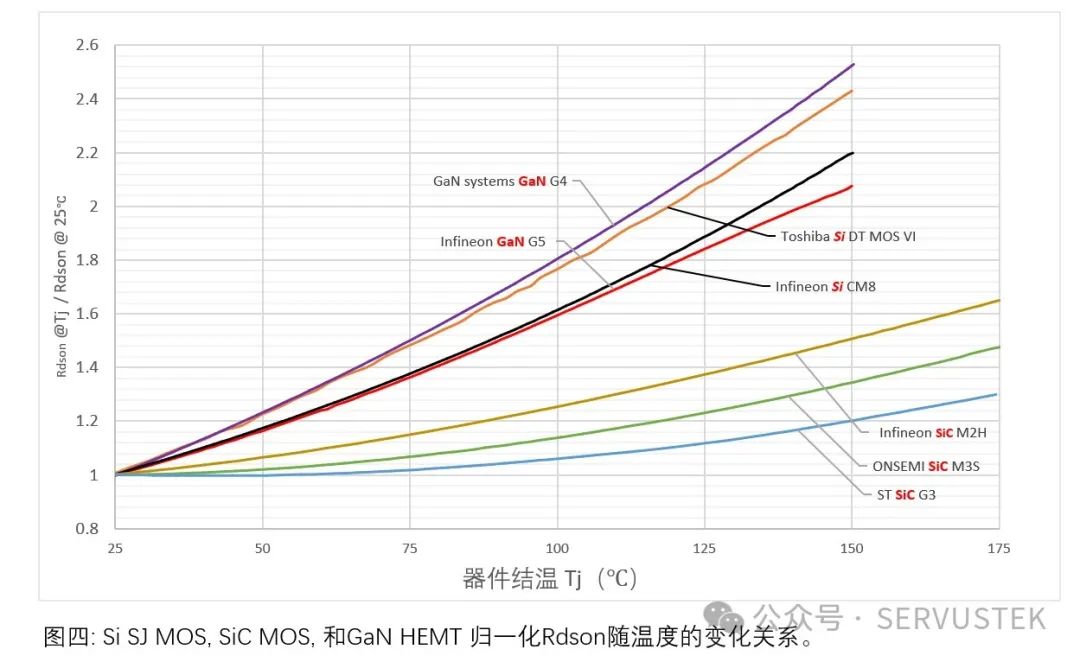

SiC MOS Rdson随温度变化最小,Si SJ MOS和GaN则旗鼓相当

在实际使用场景中功率器件一般工作于高温状态,对比Rdson随温度的变化对应用更有意义。图四对比了Si SJ MOS,SiC MOS和GaN HEMT Rdson随温度的变化,为方便对比图中对Rdson进行了归一化处理,即常温下的Rdson归一化为“1”。

参见图四由于漂移层电阻的影响Si SJ MOS,SiC MOS和GaN HEMT Rdson均随温度增加而增加,Si SJ MOS和GaN HEMT Rdson的增速类似,并大于SiC MOS。在150℃时Si SJ MOS和GaN HEMT的Rdson温度系数介于2.1-2.5,SiC MOS则处于1.2 – 1.5。Si SJ MOS和GaN HEMT最大标称结温为150℃,而SiC MOS为175℃。这给SiC MOS带来两大优势:高结温可降低散热要求并提高器件电流能力;在确保高温同样导通电阻的前提下,可用室温电阻稍大挡位产品,如用50-60mΩSiC MOS产品替代Si SJ MOS和GaN HEMT 30-40mΩ产品。

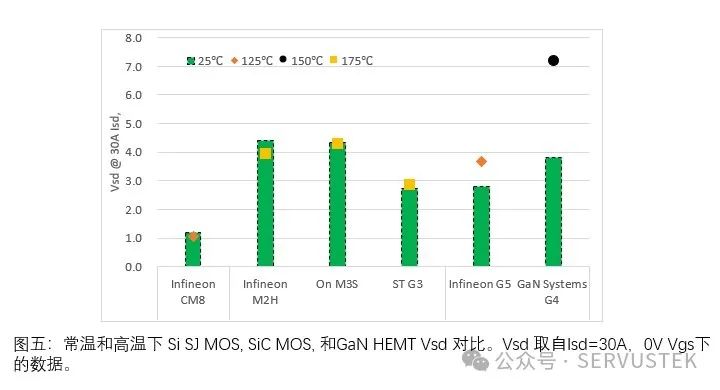

Si SJ MOS体二极管Vfsd相对较小,SiC MOS和GaN HEMT则不相上下

当对器件漏极加负压时,如GaN HEMT漏极和栅极压差大于Vgsth,则器件沟道被打开从而导电;这让HEMT表现出“准体二极管“特性,但其本质还是沟道导电,而非像MOS那样由体二极管导电。

图五对比了Si SJ MOS, SiC MOS和GaN HEMT的Vsd常温和高温性能,图中柱状为常温下数据,其它为高温下数据。Si SJ MOS Vfsd在1V左右,较SiC MOS和GaN HEMT低2-3V,SiC MOS Vfsd介于3-4.5V,GaN HEMT常温下Vfsd介于3-4V而高温下则升到4-7V左右。SiC MOS和GaN HEMT因体二极管导电而产生的损耗相对较大,但这并不妨碍其整体优异特性。

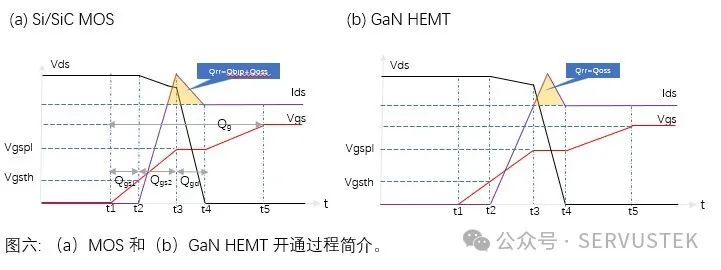

MOS和HEMT的动态开关过程类似

MOS和HEMT的开关就是对各类电容如Ciss, Coss和Crss充放电。其中Ciss=Cgs+Cgd,Coss=Cgd+Cds,Crss=Cgd,图六为MOS和HEMT硬开通时Vgs,Ids (又称Id),及Vds随时间变化的示意图,在t1到t2阶段,器件处于关断,栅极驱动主要对Cgs充电,在t2到t3阶段,栅极驱动仍然对Cgs充电,由于Vgs大于Vgsth,Id遵循饱和工作区转移特性曲线迅速增加。由于陪测体二极管Qrr的作用MOS Id在t3时达到最大值,而GaN HEMT的Id则在此时达到器件的目标输出电流,在t2-t3区间的Vds下降则由系统的寄生电感引起,此区间内器件处于饱和工作区。

在t3到t4阶段,Vgs位于米勒平台电压Vgspl,此阶段Cgd和Cds经历放电(Cgd也经历进一步反向充电)Vds下降到器件开通时的电压,由于陪测管Qoss的作用GaN HEMT Id达到最大值且在t4时刻恢复到器件导通时的输出电流,此阶段结束时器件进入线性工作区。在t4到t5阶段,栅极驱动进一步的对Ciss充电,达到目标驱动电压,降低器件的导通电阻。

MOS和HEMT的关断过程和开通过程类似,通过对各种电容的相关过程进行分析,可以得到关断时相应Vgs, Vds及Id波形。

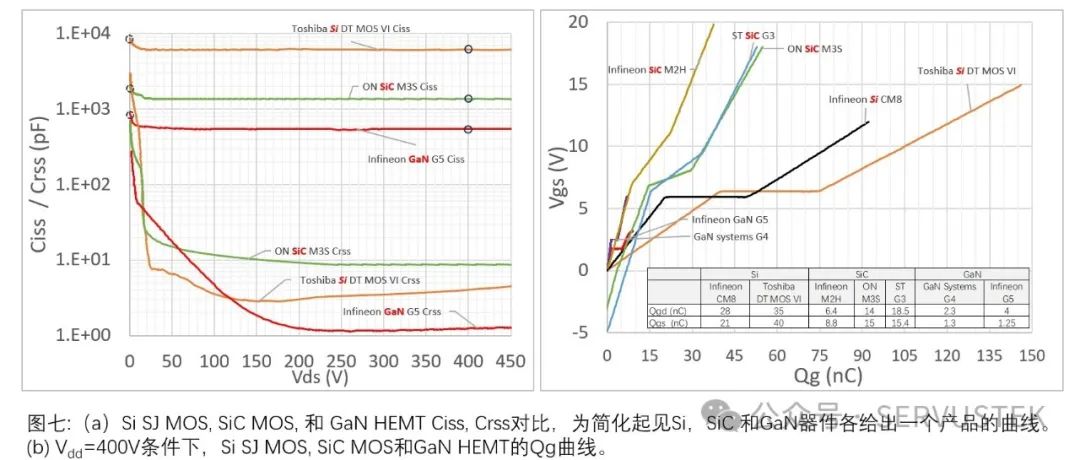

GaN HEMT Qgs, Qgd, Qg最低,SiC MOS其次,Si SJ MOS较大

如前文所述,栅极驱动在器件开启时与Cgs和Cgd的作用分为三个阶段,在第一阶段主要对Cgs充电,对Ciss(Ciss @ Vdd)进行积分可得Qgs(即图6 Qgs1+Qgs2),此阶段结束时Vgs达到米勒平台电压;在第二阶段Cgd经历放电及反向充电,对Cgd积分即得Qgd;在第三阶段对Cgs进行充电以达到推荐驱动电压,对Ciss(Ciss@Vdson)进行积分即可得相应的充电量。上述三阶段所需电荷的总和即为Qg。Qg越大相应的驱动损耗也越大,Qg和驱动电流共同决定器件的开关速度。

图七(a)给出了典型Si SJ MOS,SiC MOS和GaN HEMT Ciss和Crss随Vds变化的曲线。整个Vds电压范围内GaN HEMT Ciss最低,SiC MOS其次,Si SJ MOS最大。相应的GaN Qgs也最低(参见图七(b)及插图),为1.3nC左右,SiC MOS Qgs介于8-15nC,而Si SJ MOS Qgs则介于21-40nC之间。对Crss即Cgd来说,GaN HEMT普遍低于SiC MOS,在0-10V的Vds区间Si SJ MOS Cgd显著大于SiC MOS和GaN HEMT,然后迅速降至SiC MOS和GaN HEMT同等水平,这导致Si SJ MOS Qgd最大为28-35nC,而SiC MOS和GaN HEMT的Qgd则分别处于6–18.5nC和2-4nC的区间。仔细观察图七(b)可以发现SiC MOS米勒平台电压随Qg的增大而增大,这是由于其短沟道效应造成。

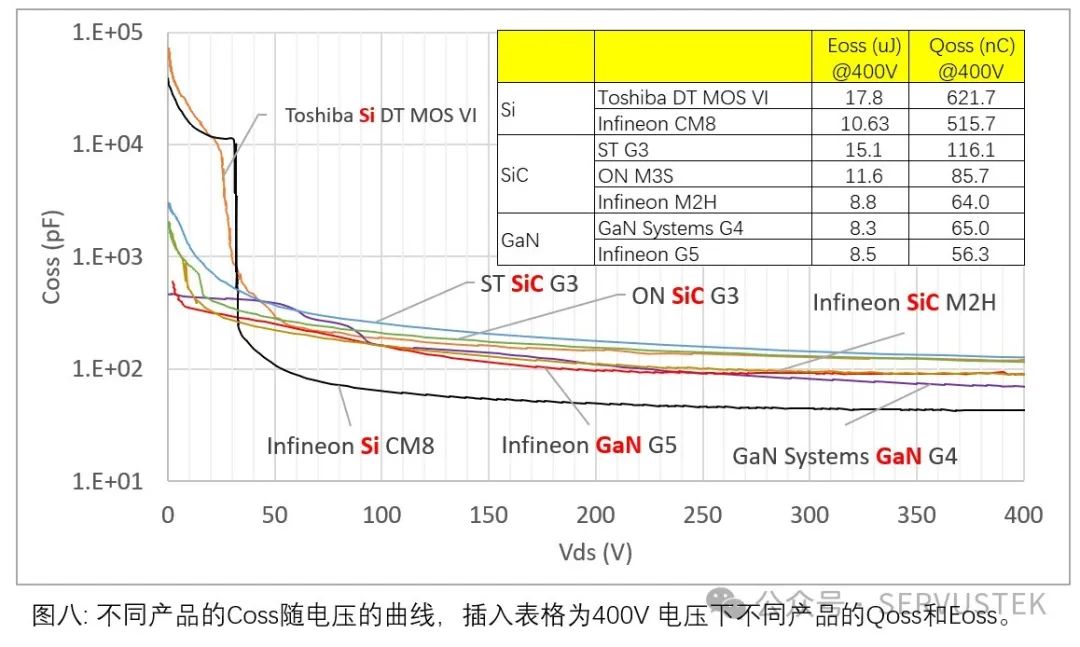

Si SJ MOS,SiC MOS和GaN HEMT Eoss旗鼓相当,Qoss Si SJ MOS最大

Coss*Vds对Vds的积分为Eoss,器件硬开通时Eoss对器件加热而损失掉。Coss对电压的积分则为Qoss,代表器件耐压时存储在Coss的电量,Qoss大小不随外界条件(如温度)变化而变化,陪测管的Qoss作为开通时电流尖峰的一部分(参见图6 t3-t4 Id阴影部分)增加器件的开通损耗。

图八为Si SJ MOS, SiC MOS和GaN HEMT Coss随Vds的变化,插图为母线电压400V时器件的Eoss和Qoss。Vds在0-30V时Si SJ MOS的Coss比SiC MOS和GaN HEMT至少大一个数量级,然后迅速下降到SiC MOS和GaN HEMT的同等甚至更低水平。GaN HEMT Eoss最低为∽8uJ,SiC MOS其次为8.8-15uJ,而Si SJ MOS位于10.6-17.8uJ之间。Si SJ MOS Qoss显著大于SiC MOS和GaN HEMT。

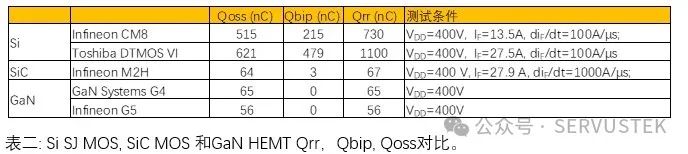

SiC MOS和GaN HEMT Qrr类似,Si SJ MOS较大

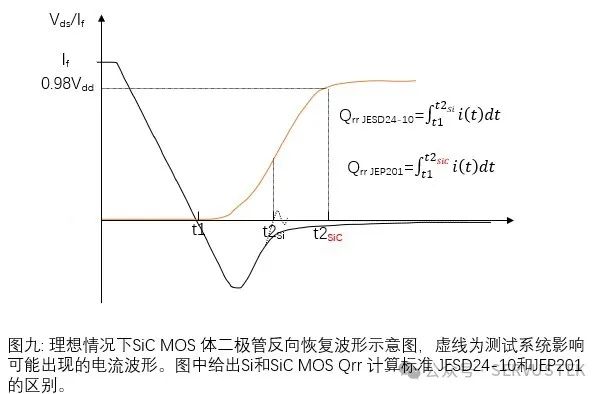

从严格意义上说Qrr=Qbip+Qoss,其中Qbip与体二极管正向导通时存贮在器件漂移层的少子电荷有关。 与Qoss不同,Qbip大小受di/dt, If,温度等多个因素影响。且测试时系统寄生电感的影响也需要考虑,JEDEC 2024年8月发布的针对SiC MOS Qrr的测试标准JEP201,有利于正确测试Qrr。

图九给出JEDEC201 SiC MOS Qrr计算方式,与Si MOS Qrr计算最大的区别是SiC MOS Qrr的积分上限为Vds达到0.98Vdd的时刻,而非反相电流第一次达到0的时间点(Si mos Qrr积分上限)。其原因为:由于系统寄生参数的影响,当反相电流达到0时(参见图中电流虚线)器件耐压会仍低于母线电压,这让按照Si MOS标准计算的Qrr失去参考意义。快速判断产品规格书Qrr计算是否合适时可检查其Qrr相对Qoss的大小。本文进行Qrr对比时Qrr统一定义为Qbip+Qoss。

表二列出Si/SiC MOS和GaN的Qrr,Qoss和Qbip。Qoss根据Coss曲线计算而得,Qbip为Qrr和Qoss的差值。Si SJ MOS Qoss比SiC MOS大一个数量级,Qbip贡献占Qrr 30-44%。SiC MOS和GaN HEMT Qrr类似,比Si SJ MOS小10倍以上,Qbip占Qrr 5%不到。这使得SiC MOS和GaN HEMT相对于Si SJ MOS更能胜任各类软开关和硬开关拓扑。硬开通时SiC MOS和GaN HEMT由于Qrr贡献而产生的损耗也显著低于Si SJ MOS。

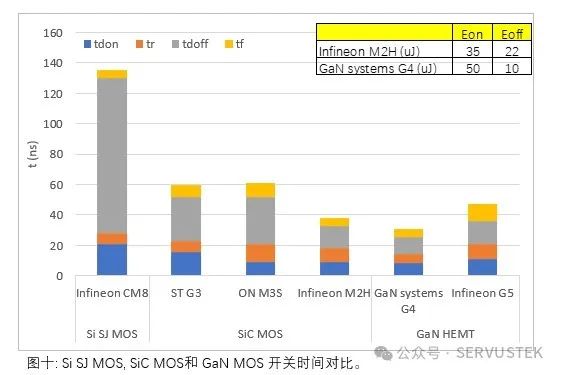

SiC MOS和GaN HEMT开关速度和损耗旗鼓相当,Si SJ MOS相对较大

器件开关速度和开关损耗是客户最为关注的核心动态参数,这些参数和器件所处的外界环境,如产品封装形式,驱动设计,系统寄生杂感等息息相关,且每个器件的最佳工作条件也不尽相同。尽管如此,对这两类参数的对比可给出一个定性的参考,从而有利于器件选型和系统优化。

图十给出了各类TOLL封装Si SJ MOS,SiC MOS和GaN HEMT产品的开关时间对比,由于tdoff的贡献Si SJ MOS开关相对SiC MOS和GaN HEMT较慢,而SiC MOS和GaN HEMT的开关时间则介于30到60 ns之间,Infineon M2H SiC MOS和GaN Systems G4 GaN HEMT开关速度最快,分别为37.7和31ns,其开关损耗也基本类似为57-60uJ(参见图十表格),考虑到GaN和SiC MOS导通电阻的高温特性,M2H整体性能优于GaN HEMT G4。也可用50-60mΩSiC MOS去对标30-40mΩGaN HEMT,从而获得性能和成本的平衡。

Si,SiC和GaN功率器件异同小结

综上所述,GaN HEMT Vgsth和驱动电压较小,在实际应用中对系统设计能力要求较高。由于材料本身或器件结构的原因SiC MOS和GaN HEMT Vfsd较Si MOS大,这导致体二极管续流时损耗大。在开关速度,开关效率和Qrr(Qoss+Qbip)方面SiC MOS和GaN HEMT旗鼓相当优于Si SJ MOS。由于体二极管的缺失GaN HEMT Qrr不存在Qbip贡献,这让器件缺失雪崩能力,但也成就其独有的双向耐压能力。SiC MOS是Si SJ MOS在高频,高效,高功率密度应用方面的自然延伸。当应用和器件设计能充分发挥GaN HEMT特有的双向耐压特性时,GaN会在自己独有的领域大放异彩。目前GaN相对于SiC MOS主要聚焦在小功率应用,如何解决散热从而进军大功率应用则是GaN的下一挑战。

-

封装

+关注

关注

128文章

8832浏览量

145927 -

功率器件

+关注

关注

42文章

1953浏览量

93141 -

SiC

+关注

关注

32文章

3263浏览量

65894 -

GaN

+关注

关注

19文章

2238浏览量

77381 -

HEMT

+关注

关注

2文章

76浏览量

13774

原文标题:Si SJ MOS, SiC MOS和GaN HEMT之异同

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

CC2640的4x4,5x5,7x7三种封装,区别是什么?

VCC、VDD和VSS三种不同的符号区别

请问zstack的三种安全模式有什么区别?

三种STOP模式的区别是什么

继电保护的三种状态解析

三种功率器件的应用区别

三种功率器件的区别解析

三种功率器件的区别解析

评论