文章来源:学习那些事

原文作者:赵先生

3D闪存有着更大容量、更低成本和更高性能的优势,本文介绍了3D闪存的制造工艺与挑战。

使用 3D 闪存的意义

现存的包含 BE - SONOS 的 2D 闪存架构,在 1x 纳米节点处遭遇了密度集成难题,这与逻辑电路持续微缩时面临的困境类似,即现有的结构已无法契合继续缩小尺寸后的性能需求。鉴于此,业界研发出 3D NAND 闪存架构,旨在解决在追求更低每比特成本以及实现更高密度过程中所面临的问题。2012 年,韩国三星公司推出全球首款 3D NAND 闪存芯片,该芯片首次采用 32 层单层单元结构(single - level cell,SLC),存储单元以垂直方式堆叠成多层。相较于现有的 2D 闪存,这是一种更为先进的闪存架构。

从 2D 闪存向 3D 闪存过渡时,工艺环节需增添多层存储单元以及各层之间的互连结构。一款典型的 3D NAND 闪存芯片,层数可达 32 层、48 层、64 层、96 层,甚至 128 层。与 2D 闪存相比,层数的增加使得 3D 闪存的制造过程更为复杂且耗时。不过,多层架构让存储器件在拥有更短连接路径的情况下,得以实现更高的位密度,进而展现出更优的性能。3D 闪存具备以下优势:

容量优势:与 2D NAND 闪存相比,3D NAND 闪存拥有更大的存储容量与数据密度。通过堆叠多层存储单元构建三维存储矩阵,在相同的芯片面积 —— 即占用空间内,能够提供更大的存储容量。同理,更为密集的芯片可被集成到更紧凑、容量更高的设备之中。

成本优势:闪存与其他存储技术一样遵循每字节成本的关联规律。相较于 2D NAND 闪存,3D NAND 闪存能够显著降低每字节成本。

性能与功率优势:当存储单元以 2D 矩阵布局时,数据移入和移出单元的距离存在限制。而这一距离等同于时间 —— 也就是延迟。为增大 2D 矩阵的存储容量,这些距离以及延迟也必然随之增加,这实际上降低了更大容量 2D NAND 闪存设备的性能。3D 闪存通过堆叠并互连闪存存储单元层,能够缩短物理距离,进而减少延迟,使得在更高存储容量下仍能维持较高性能。此外,3D NAND 闪存可实现单次写入,功耗相较于 2D NAND 降低 50%。

闪存的制造工艺

在当下的 3D NAND 闪存工艺技术领域,栅极形成工艺主要朝着两个不同方向发展,分别为电荷陷阱工艺技术以及浮栅技术工艺。一方面,像三星、SK 海力士以及东芝等公司,正在运用电荷陷阱闪存技术。该技术运用氮化硅构成的非导电层,此层环绕在单元的控制栅极周围,能够捕获电荷,以此维持单元的完整性。与之形成对比的是,Intel 和美光公司并未选用电荷陷阱技术。相反,他们将原本应用于 2D 闪存的浮栅结构拓展至 3D NAND 闪存当中。在浮栅结构里,栅极本质上是一种导体,而看似浮栅的电荷陷阱层实则为绝缘体。浮栅技术在实施过程中,涉及一些较为复杂的图案化步骤,尤其是在制作垂直孔的侧面时,图案化操作难度较大,必须历经诸多额外的流程步骤。相对而言,电荷陷阱技术的优势在于无需进行图案化处理,然而其缺点在于电荷传输效率方面存在问题,而这一问题实际上也反映为成本问题。图 1 展示了不同公司所采用的 3D NAND 工艺技术情况。

图1:现代3DNAND闪存结构

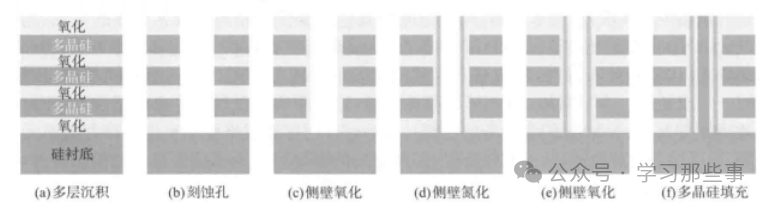

以位列堆叠(bit column stacked,BiCS)架构为例,3D NAND 闪存的具体工艺步骤如下:首先,在硅晶圆衬底之上制造一层 CMOS 逻辑芯片,将其作为外围逻辑。同时,在衬底上构建导电路径,用于连接成对的相邻列,随后使用一层二氧化硅进行绝缘处理。接着,在其顶部沉积导电多晶硅层,以此形成第一字线和控制栅极,并且让二氧化硅层在多晶硅顶部生长,目的是使其与后续将沉积在上方的多晶硅层相互绝缘。这一系列操作将重复多次,成对的多晶硅层和二氧化硅层会在整个晶片上层层堆叠,最终形成薄片结构。这种结构类似于蛋糕坯和糖霜交替层叠而成的夹心蛋糕,如图 2(a)所示。

一旦在晶片上沉积了所需数量的上述层之后,便要在晶片上对圆孔阵列进行图案化处理,随后将这些孔刻蚀贯穿所有层,直至抵达基板。图 2(b)展示了其中一个孔的情况。这种刻蚀技术与 DRAM 沟槽单元技术类似,仅需一个掩模步骤,便能为器件中的所有层形成孔。即便串中可能包含 16、32、64 或更多数量的晶体管,也仅需这一个掩模步骤。相较于现今的 2D NAND 制造工艺,这无疑是一种极为经济高效的光刻技术。

接下来便是制作浮栅极和沟道孔的内壁。首先,涂抹一层二氧化硅层 [见图 2(c)],以此创建栅极电介质(即控制栅极和浮栅之间的电介质)。可以将其想象为一个衬在洞里的管子。其次,通过在二氧化硅层上沉积氮化硅层来制作浮栅,这就如同在管内又形成了一个管 [见图 2(d)]。随后,在氮化硅层上再沉积另一个氧化物层,用于形成隧道电介质 [见图 2(e)],这便是排列在孔壁上的三个同心管中的第三个。最后,通过向其中沉积多晶硅 [见图 2(f)],来填充整个孔(或者在这些同心管在侧壁上完成分层之后所剩余的空间)。BiCS 技术属于一种电荷陷阱技术,因其使用的是绝缘层,所以即便每个单元的电荷陷阱之间并无差异,两个相邻的电荷陷阱也不会相互干扰。而且这一层完全无需进行图案化操作。

图2:BICS构架3DNAND闪存的基本工艺步骤

闪存的工艺挑战

尽管 3D NAND 闪存的存储单元结构相对直观易懂,然而,不管采用何种架构,无论是电荷陷阱工艺技术,还是浮栅工艺技术,3D NAND 闪存的制造工艺都极为艰难复杂。从原始晶圆加工成完整的晶粒裸片或芯片,需历经数千个独立工艺步骤。制造过程中,任何一处出现错误或遭受污染,都可能产生缺陷,致使整个芯片报废。因此,要实现高质量制造,必须采取极为严格的污染预防措施,对制造过程进行精准控制,并确保材料纯度极高。接下来,主要探讨现代 3D 闪存工艺面临的难点与挑战。

1) 交替层的堆叠沉积

在 2D NAND 的制造中,先进的光刻技术起着关键作用。但在 3D NAND 制造里,供应商采用的是 40nm 至 20nm 的后缘设计规则。虽说先进光刻技术仍在使用,可已不再是最关键的环节。对于 3D NAND 而言,工艺挑战已从光刻工艺转移至沉积工艺与刻蚀工艺。实际上,3D NAND 为业界带来了诸多全新且难度颇高的工艺步骤。通过将位串拓展至第三维度,该技术虽缓解了诸多图案微缩难题,却引入了一些极为复杂的新流程。这些流程的一致性至关重要,挑战主要聚焦于对几个关键流程的可变性控制。

3D NAND 的工艺流程始于衬底。随后,供应商便面临首个主要挑战 —— 交替堆叠沉积。利用化学气相沉积(CVD)技术,交替堆叠沉积指的是在基板上逐层沉积并堆叠薄膜的过程。这一过程恰似制作夹心蛋糕,简单来讲,就是先在基板上沉积一层材料,接着在其上再沉积另一层材料,如此重复多次,直至特定器件达到所需的层数。不同制造商采用不同的材料组合来构建层堆栈。比如,三星公司在硅衬底上交替沉积氮化硅和二氧化硅层;东芝的 3D NAND 技术则由导电多晶硅和绝缘二氧化硅的交替层构成。交替堆叠沉积必须具备良好的均匀性与低缺陷率。所有沉积层的均匀性都要好,这样才能实现良好的应力控制。由于交替的薄膜各不相同,对于每一层薄膜,都可能因材料不匹配而产生应力问题。而且,随着 3D NAND 闪存层数的增加,工艺难度与挑战也在持续攀升。

2) 高深宽比刻蚀

完成交替堆叠沉积步骤后,需在表面施加硬掩模,并进行图案化处理,以形成所需的孔。此时便进入工艺流程中最为棘手的部分 —— 高深宽比刻蚀,即从器件顶部向衬底刻蚀微小的沟槽或通道。为了说明这一步骤的复杂程度,以某类 3D NAND 芯片为例,同一芯片中存在 250 万个微小通孔,且每个通孔都必须保持平行且均匀。目前的高深宽比刻蚀工具能够满足 32 层和 48 层器件的需求,对于这些芯片,深宽比范围在 30:1 至 40:1 之间。这种刻蚀过程极为复杂,要在大量刻蚀过程中保持高度的统计学一致性,对存储设备的性能有着极为严苛的要求。而对于 64 层及以上的芯片,以目前的刻蚀能力而言,难度过高,现有的刻蚀和硬掩模技术未必适用于 60:1 或 70:1 这样的高深宽比。

因此,NAND 供应商目前同时推进两条技术发展路径。第一条路径是等待下一代高深宽比刻蚀工具以及其他相关技术的问世。一旦刻蚀机按时研发完成,现有的 3D NAND 技术将按照如下顺序实现扩展:从现有的 32 层和 48 层,逐步发展到 64 层,进而迈向 96 层,最终达到 128 层。而在第二条路径中,NAND 制造商致力于开发下一代串堆叠技术。所谓串堆叠技术,简言之,就是把多个 3D NAND 闪存器件进行堆叠,并且每个器件之间可能会用绝缘层加以隔离。例如,制造商计划开发 48 层的 3D NAND 闪存器件,这一过程需要历经前文所提及的各类工艺流程,诸如交替层沉积、刻蚀等操作。供应商会采用同样的流程制造出另外的 48 层 NAND 芯片,之后将它们堆叠在一起。需要注意的是,该工艺并不局限于 48 层芯片。倘若相关技术成熟,制造商甚至可以对 64 层、96 层乃至 128 层的芯片进行堆叠。从理论层面考量,通常会优先选用 32 层和 48 层芯片来实施串堆叠,原因在于相较于 96 层或 128 层芯片,单个 32 层或 48 层器件所承受的应力相对较小。

然而,最终带有串堆叠的 3D NAND 技术或许会在堆叠层数达到 300 层左右时遭遇瓶颈。随着堆叠层数的增加,因堆叠过程中产生的缺陷而导致的良品率损失会持续攀升,这无疑将成为限制技术发展的一大因素。此外,所有堆叠的薄膜材料都会受到应力方面的制约。可以确定的是,字符串堆叠技术目前仍存在诸多未知因素以及挑战。即便不考虑字符串堆叠技术,整个行业在 3D NAND 技术领域依旧面临着一些难题。无论处于何种情形,业界都必须持续深入研究并完善 3D NAND 的各个工艺步骤。否则,该项技术的成本仍将居高不下。

3) 金属沉积

在完成栅极的制作后,接下来的通孔形成工艺同样充满挑战。此环节需要借助金属沉积步骤,利用金属导体对 3D NAND 闪存器件进行回填操作。

通常情况下,会选用钨作为回填通孔孔洞的材料。这一沉积步骤极具难度,因为它属于非视线沉积方式。倘若没有合理设计工艺流程,在沉积过程中极有可能错误地镀出金属钨的前体金属。这些前体金属在进入接触柱孔洞时,可能会立刻脱落,进而导致接触柱出现空隙。

-

NAND

+关注

关注

16文章

1723浏览量

138336 -

制造工艺

+关注

关注

2文章

205浏览量

20431 -

闪存芯片

+关注

关注

1文章

132浏览量

19931 -

3D闪存

+关注

关注

0文章

22浏览量

6706

原文标题:3D闪存工艺

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

制造业革命——3D打印的主流工艺盘点

美光推出首款3D XPoint闪存 展现出了3D XPoint闪存的强大实力

3D打印技术是怎么推动制造业的

一种用于制造电动机永磁体的冷喷涂3D打印工艺

3D工艺的转型步伐较慢,NAND闪存依然处于供给吃紧的状态

3D打印助力汽车零部件制造工艺提升

三星正在研发160层及以上的3D闪存

三星正在开发160堆栈3D闪存 将大幅改进制造工艺

美光发布176层3D NAND闪存

不要过于关注3D NAND闪存层数

英国大学开发了一种全新3D打印工艺

3D闪存的制造工艺与挑战

3D闪存的制造工艺与挑战

评论