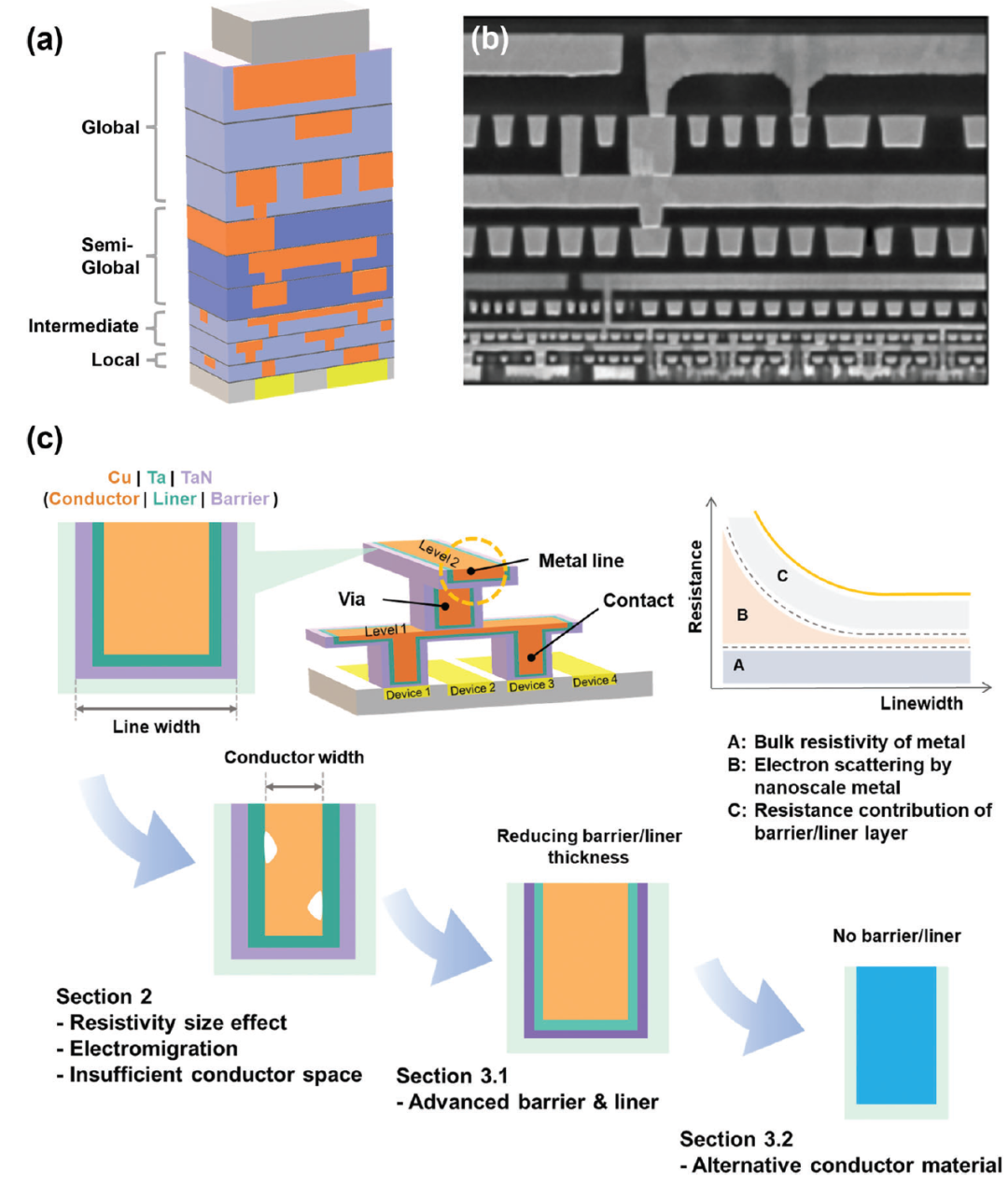

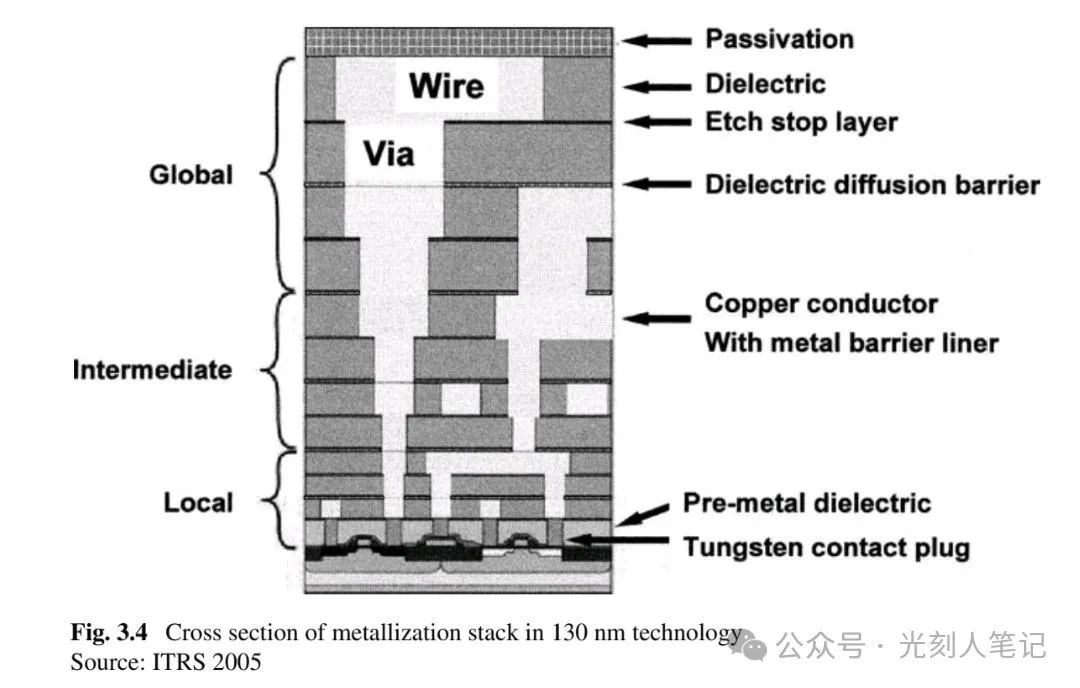

随着集成电路的集成度越来越高,器件尺寸变得越来越小,金属互连设计也紧跟这个趋势,布线的密度增加了,更长的互连线会导致了更高的电阻。与此同时,互连体积的减少会引起电容耦合和串扰的几率显著增加。当互连尺寸很小时,RC 延迟的大小深刻影响着芯片的性能(R代表了互连线电阻,C代表了介质层分隔的金属连线之间的寄生电容)。该延迟即时间,它应该足够的小且能够准确地传递信号。

Liner:衬垫层,有助于金属粘合;Barrier:阻挡层,阻止金属扩散至介质层

有效减小RC延迟的方法之一是用铜互连代替过去的铝互连;另一种方法是在互连线之间插入介电常数更低(Low-k)的材料,有效降低寄生电容和串扰。本文这里就不详细展开了,读者可以参阅《低介电常数材料的发展历程简介》

一、铜互连面临的问题

目前铜互连已经发展成为主流工艺,并日益完善。然而铜互连也面临一些问题。随着线宽(Line Width)的缩小,采用铜作为互连材料的可靠性问题日益突出。列举一个对比数据:工艺节点从45nm下降到22nm,RC延迟会增加7%,下降到10nm,RC延迟会增加22%,再下降到7nm,RC延迟会增加48%。

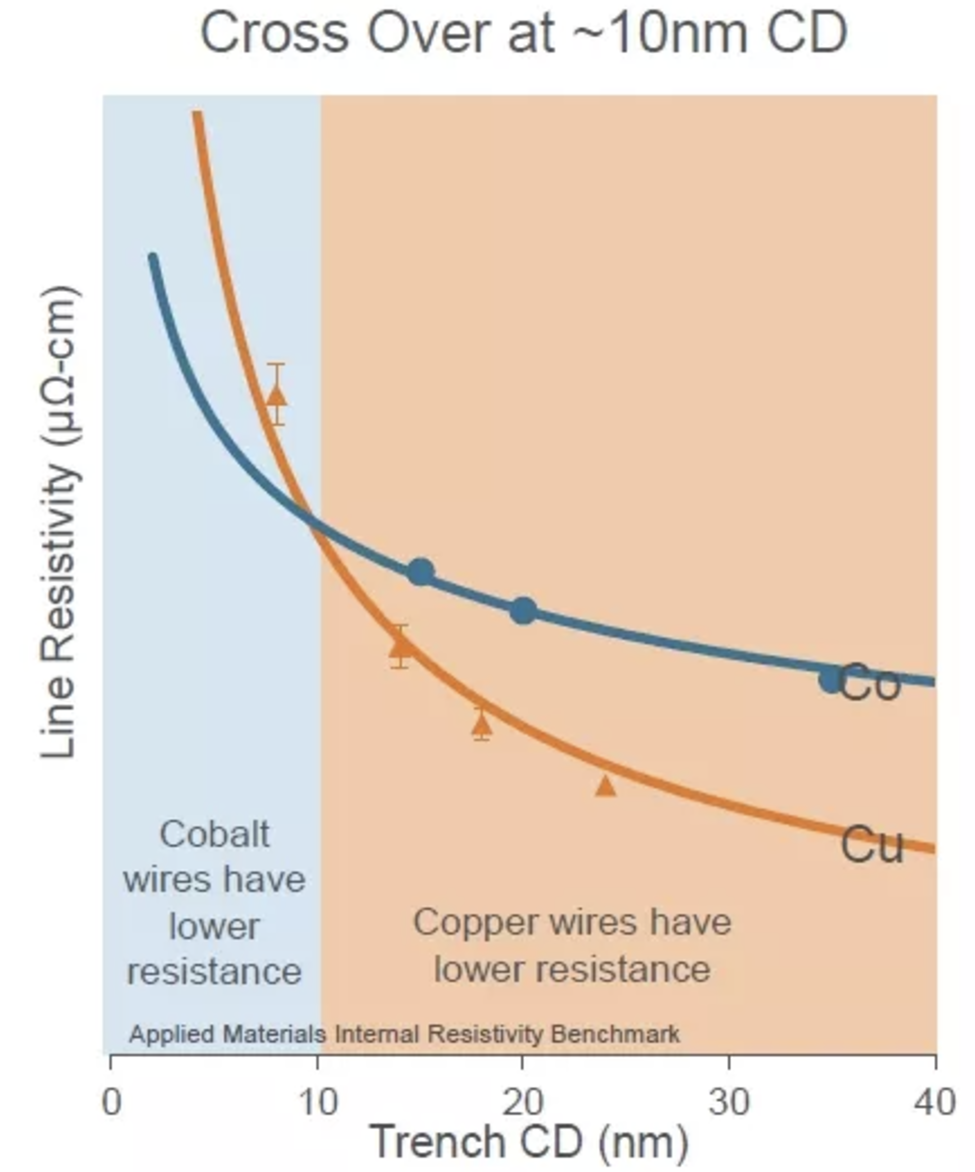

RC延迟增加的一个重要原因是,随着线宽的缩小,互连线的电阻率在急剧增加,限制器件的性能并阻碍缩放。在宏观尺度下,铜的体电阻率往往是影响线电阻率的主要因素,然而随着线宽减小至铜的平均电子自由程(40nm)以下,表面和晶界的电子散射急剧增强,这种会导致线电阻率的急剧增加,并最终造成RC延迟升高。例如,当线宽从20nm下降到10nm时,线电阻率从约1.8μΩ/cm增加到约20μΩ/cm。这种在纳米尺度上发生的载流子增强散射现象,被称为尺寸效应(Size Effect)。

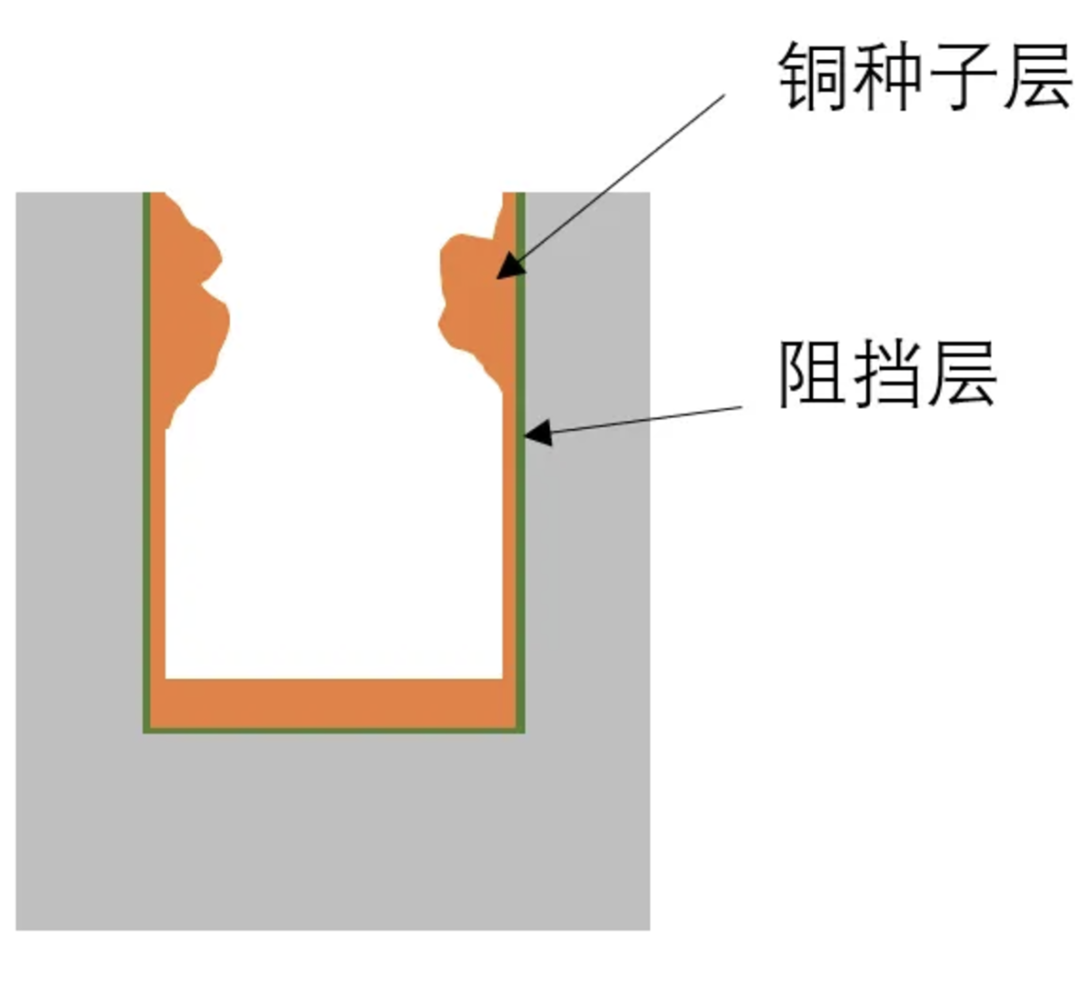

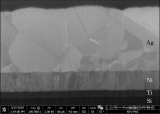

线宽的缩小除了导致线电阻率的增加,还伴随着电流密度和器件工作温度的升高,所产生的电迁移(EM)或应力空洞将严重损害互连材料的可靠性。如上图,阻挡层、种子层以及电镀工艺可能无法完美的契合,导致金属淀积时很容易出现空洞等缺陷。在制作种子层时,通常会在沟槽或通孔的顶部产生悬垂,甚至沟槽顶部会存在开口不足的情况。此外,一些添加剂很容易在沟槽的开口处附着并堵塞,导致铜淀积不完整,形成空洞等缺陷。

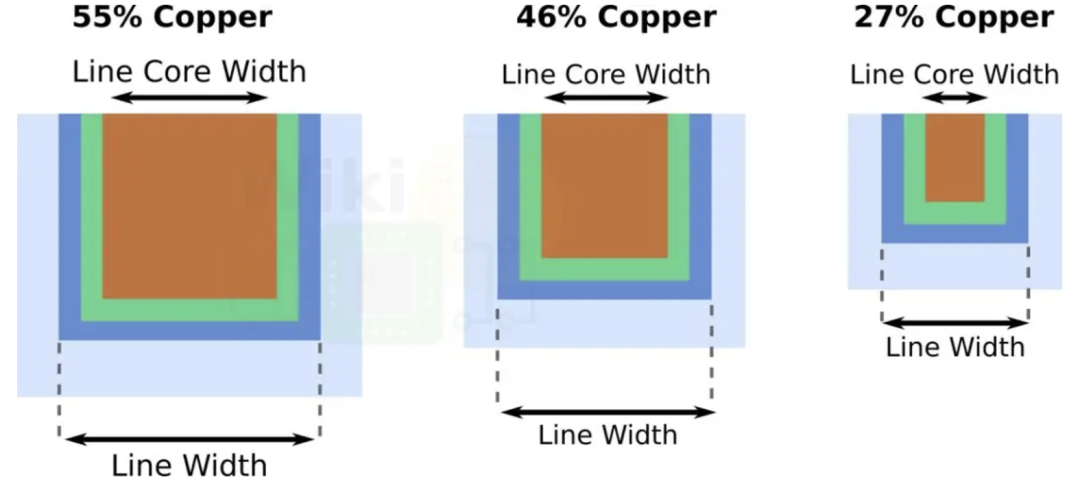

在阻挡层(体电阻率较高)厚度固定的前提下,随着线宽缩小,沟槽内铜的比例会越来越低,这样就进一步缩小了铜互连线的截面积。换句话说,不断缩小互连尺寸会显著增加阻挡层的体积比,从而加速互连线电阻率的升高。

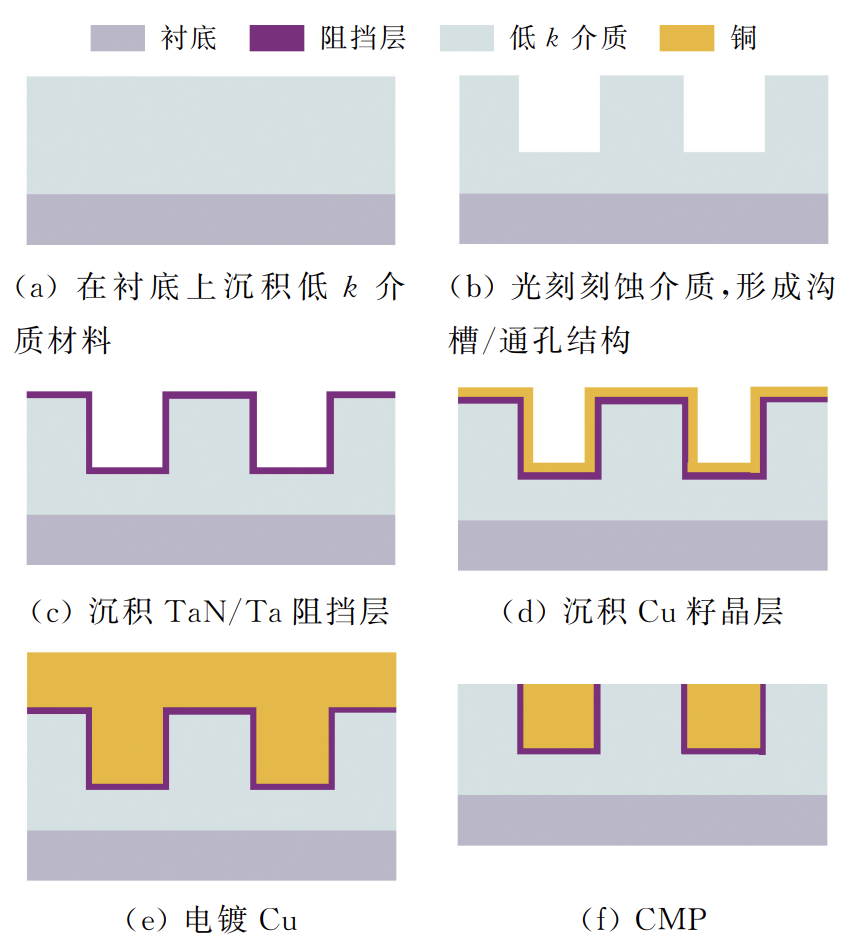

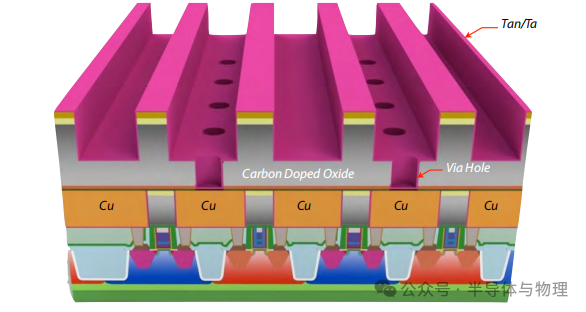

二、大马士革镶嵌工艺

由于铜不能产生挥发性的氯化物,很难用反应性离子刻蚀(RIE)的方法来制作互连线图形,因此铜互连多采用大马士革镶嵌工艺(下图)。在镶嵌工艺中,先在低 k 介质层上刻蚀所需沟槽和通孔,然后沉积一层阻挡层,有时介质层也可充当阻挡层,再把铜淀积到这些沟槽或通孔中。最后用化学机械抛光的方法对互连线作整体平坦化,去掉多余物质。

大马士革工艺通常有两种:双镶嵌和单镶嵌。所谓双镶嵌工艺是同时制备通孔及本层的工艺连线,而在单镶嵌则是两者被分别制备出来。由于双镶嵌比单镶嵌工艺少大约30% 的工序,因此最为常用。铜淀积可以用化学气相沉积(CVD)、溅射、电镀等方法。由于溅射工艺的台阶覆盖性差,CVD会有杂质在沉积过程中夹杂在薄膜里,且沉积速度慢,而电镀的优势在于设备成本低、工作温度低、薄膜均匀、质量好,对通孔及沟槽的填充能力强。因此电镀技术是铜淀积技术的主流。

三、阻挡层的发展历程

阻挡层在增强金属互连的机械完整性和电气可靠性方面发挥着重要作用,可以防止金属扩散并提供与周围介质层之间牢固的附着。比如铜在低温下会在硅和二氧化硅中迅速扩散,减少器件的少子寿命并造成pn结漏电流。当器件尺寸微缩时,阻挡层在保护器件免受金属毒害方面起到关键作用。

好的阻挡层材料应该具有高熔点,因为扩散性与材料熔点直接相关。高熔点金属(Cr、Ti、Nb、Mo、Ta 和 W)作为铜与硅之间的阻挡层被大量研究。从电阻率和使用二次离子质谱(SIMS)探测阻挡铜扩散这两方面,证实在难熔金属中 Ta和 W是性能较为优良的阻挡材料。

多晶薄膜有晶界的缺陷,并且晶界被认为是扩散的主要途径,这限制了它们的应用。不过可以通过加入氮元素来填塞晶界,TaN和 WaN被证实是性能更为优秀的阻挡材料,如TaN阻挡层的热稳定性达到了 650℃。三元非晶材料也是目前研究的热点,在形成氮化过程中掺入硅形成三元非晶氮化物,如Ta36Si14N50由于晶界的消除其热稳定性达到了 900℃。不过,这些二元和三元扩散阻挡层有太高的电阻率(100~1000μΩ/cm),而且稳定性也只是在厚度大于 10nm才有效。随着线宽的缩小,阻挡层的厚度也只会越来越小,并且要求有接近于铜的低电阻率,这对阻挡层材料微结构的质量控制以及材料淀积工艺(如台阶覆盖能力)提出了更高的要求。

在 14nm 以下的技术节点中,基于传统PVD的Ta/TaN衬垫/阻挡层所能发挥作用变得愈发受限,究其主要原因:一是随着线宽的缩小,体电阻率更高的Ta/TaN层占据了越来越高的布线横截面,导致线电阻率增加;二是为了在14nm及以下技术节点中保持铜体积分数约在83%,必须将Ta/TaN衬垫/阻挡层薄化至小于3nm;三是使用PVD工艺难以制作小于3nm厚度下高度整体、连续和均匀的Ta/TaN层;四是在深槽内形成所需的具有连续、平滑和整合性的铜种子层(约2~3nm)与Ta/TaN阻挡层结合力很差。为了克服与金属互连微缩相关的这些挑战,研究人员发现选择钴(Co)作为铜的替代品极具吸引力,除了它具有较低的电阻率并在高深宽比孔内具有更好的整合覆盖外,还可以直接在阻挡层上沉积而无需种子层,并且不会损伤衬底。相较于铜互连,钴互连所需的阻挡层会更薄。这就是钴互连的故事起源,本文就不过多展开了。

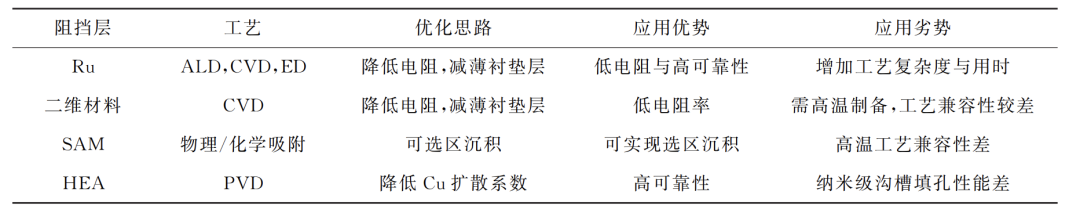

当然随着先进工艺的发展,多种新型阻挡层候选材料及其工艺处在不同研发和验证阶段,其往往具有比传统材料 TaN/Ta 更小的电阻率和更优秀的阻挡性能,但也面临着材料体系优化、制备和工艺兼容性、技术成熟度等巨大挑战。新一代阻挡层材料,包括如铂族金属基材料(PGM)、二维材料、自组装单分子层(Self-Assembled Molecular Layers,SAM)和高熵合金(High-Entropy Alloy, HEA)等有望在不远的将来得到技术应用。

-

集成电路

+关注

关注

5431文章

12173浏览量

369312 -

RC

+关注

关注

0文章

236浏览量

49834

原文标题:【推荐】一文了解金属互连中阻挡层

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

为什么LED芯片正电极要插入二氧化硅电流阻挡层,而负极没有?

详解原子层沉积薄膜制备技术

一文了解铝基覆铜板

什么是渗透作用_金属封装又是如何发生渗透

互连中的信号畸变(信号完整性揭秘)

一文了解金属互连中阻挡层

一文了解金属互连中阻挡层

评论