本文介绍了集成电路工艺中的金属。

集成电路工艺中的金属

概述

在芯片制造领域,金属化这一关键环节指的是在芯片表面覆盖一层金属。除了部分起到辅助作用的阻挡层和种子层金属之外,在集成电路工艺里,金属主要发挥着三种重要功能:

1.接触(contact):这是指在硅芯片的表面,把芯片内部的结构(像是源极、漏极、栅极等)与第一层金属层连接起来。通常会采用钨金属来实现这种接触。

2.互连(interconnect):其作用是利用由诸如铝、铜这类导电材料制成的连线,将电信号传送到芯片的不同部位。

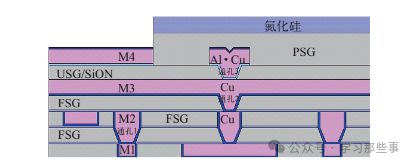

3.通孔(via):如今的芯片常常具备不止一层的互连线结构,需要多层金属连线,以下图 为例,它采用了 4 层金属层。在介质层中,从某一金属层通向相邻另一金属层、形成电通路的开口,就被称作通孔。通孔材料可以选择钨或者铜。

4层金属与3层通孔结构

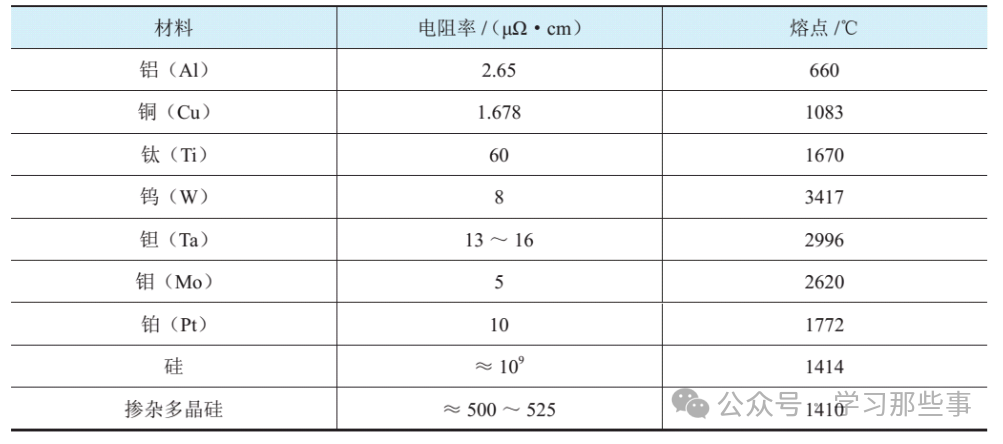

在集成电路工艺中,常见的金属以及金属合金包含铝、铝铜合金、铜、硅化物、金属填充塞、阻挡层金属。常用金属与硅、掺杂多晶硅的电阻率和熔点数据呈现在下表中。

常用金属与硅、掺杂多晶硅的电阻率与熔点

从这些数据里能够总结出两个特性:其一,铝的熔点相对较低,而其他金属的熔点普遍较高;其二,掺杂多晶硅的电阻率相比硅大幅减小,不过依旧比金属的电阻率高一些。

铝

在室温条件下,铝的电阻率为 2.65uΩ?cm,处于较低水平,只是比金和银的电阻率略高一点。然而,金和银的价格要比铝昂贵许多,并且它们在氧化膜上的附着效果不佳,同时银还容易遭受腐蚀,在硅和二氧化硅中的扩散率也比较高。所以,在早期的互连金属选择上,人们倾向于使用铝。铝作为互连金属。

具备以下优势:

电阻率低,导电性能出色:能够高效地传输电信号。

2.化学反应促进粘附:铝能够与氧化硅发生化学反应,在加热的情况下会生成氧化铝(ALO),这一反应增强了铝和氧化硅之间的粘附力。

3.易于沉积:可以较为轻松地在硅片上完成沉积操作。

4.易于刻蚀:能够通过湿法刻蚀进行处理,并且不会对下层薄膜产生影响。

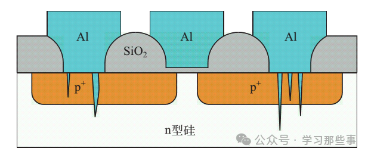

铝氧化后所生成的氧化铝,一方面强化了与衬底的粘附,另一方面能够抵御空气中潮气等因素对芯片造成的不良影响,从而起到保护芯片的作用。也正是基于这个原因,尽管现代高端芯片的下层金属互连不再使用铝,但它最顶层的互连金属常常还是选用铝基的金属薄膜。不过,在加热过程中,铝和硅之间容易引发不良反应,这种反应会促使铝和硅形成微合金,这个过程被叫做结 “穿通”。如下图所示,当出现这种情况时,铝会像尖刺一样扎入有源区,硅向铝中扩散,同时在硅片中留下空洞。针对结尖刺的问题,可以通过向铝中添加少量(大约 1%)的硅来解决,借助在 400℃热退火工艺下,在铝、硅界面形成铝硅合金。此外,预先沉积一层阻挡层(比如氮化钛)也能够解决这一问题。

结“穿通”现象

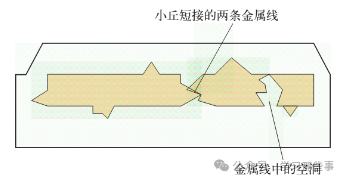

铝铜合金

铝作为一种多晶材料,其内部由众多单晶粒组合而成。当铝被用于互连时,存在一个不可忽视的弊端,即电迁移现象。从下图中能够清晰看到,在大电流密度的环境下,电子与晶粒中的铝原子频繁碰撞,这会使得铝原子逐步发生移动。随着铝原子的移动,空洞逐渐产生,进而导致铝连线不断变薄,甚至有可能引发断路故障。就算暂时没有出现空洞,剩余部分也会因电流分布变化而形成更高的电流密度,如此一来,会进一步加剧电迁移现象的发生,最终还是会导致线路断开。另外,铝原子移动到其他区域后,会堆积起来形成小丘。这些小丘可能会造成相邻的原本不导通的连线之间发生短路。由此可见,铝的电迁移现象严重威胁芯片的可靠性,即便在短时间内芯片能够正常工作,但随着时间的推移,大概率还是会出现问题。

铝的电迁现象

在超大规模集成电路中,问题更为突出。芯片温度会随着电流密度的增大而升高,而这两个因素 —— 较高的温度和大电流密度,都会使得芯片中的铝金属更容易出现电迁移现象。为了解决这一棘手的问题,通常会采用向铝中掺入少量铜的方法,使用铝铜合金来作为金属互连线。当铝和铜形成合金,并且铜含量保持在 0.5% 左右时,连线中的电迁移现象能够得到有效的抑制。在这种情况下,铜就如同胶水一般,将铝内部的各个小晶粒紧密地黏合在一起,从而有效阻止它们随意移动,保障了芯片互连线路的稳定性和可靠性。

铜

在集成电路工艺持续进步的大背景下,芯片集成度呈现出飞速提升的态势,金属互连布线的层数也在不断增多。在这种发展趋势下,传统用作互连金属的铝,因其电阻率相对偏高,已经难以满足日益增长的技术需求,迫切需要一种拥有更低电阻率的金属来替代它。就在这时,铜以其独特的优势进入了人们的视线。将铜作为互连金属材料,具有以下一系列突出优点:

1.更低的电阻率:在室温环境下,铜的电阻率仅为 1.678μΩ?cm ,相较于铝的 2.65μΩ?cm 有了大幅下降。这一特性能够有效降低 RC 信号的延迟时间,进而显著提高芯片的运行速度,使得芯片能够在更短的时间内处理更多的数据。

2.更高的集成度:由于铜的使用允许采用更窄的线宽,这就使得芯片在有限的空间内能够容纳更多的电路元件。举例来说,原本使用铝作为互连金属时,每平方毫米只能容纳 1000 个电路元件,而换成铜之后,同样面积下可以容纳 1500 个甚至更多。集成度的提升,不仅可以减少所需的金属层数,还能优化芯片的整体结构,降低芯片的制造成本。

3.更好的抗电迁移性能:与铝不同,铜在正常工作条件下几乎不存在电迁移问题。电迁移是指在大电流密度的作用下,金属原子会发生移动,从而导致金属连线变薄甚至断裂。而铜不存在这个问题,这极大地提高了芯片的可靠性,减少了因电迁移导致的故障风险,延长了芯片的使用寿命。

4.更小的功耗:随着铜线宽的减小,器件在运行过程中的功耗也随之降低。这不仅有助于延长芯片的使用寿命,还能提高能源利用效率,符合当前绿色环保的发展理念。例如,在一些移动设备中,采用铜作为互连金属后,电池的续航时间得到了明显提升。

5.更少的工艺步骤数:通过采用新颖的铜双大马士革工艺(详细流程将在 7.5 节进行详细介绍),可以同步完成通孔和互连的制作。这种创新工艺能够使工艺步骤数减少 20% - 30% ,大大提高了生产效率,降低了生产成本,为大规模生产提供了有力支持。

尽管铜具备诸多优点,但在实际应用过程中,人们还是遇到了一些挑战:

1.扩散与金属沾污问题:铜具有较强的扩散能力,能够迅速进入氧化硅和硅材料中,进而导致严重的金属沾污现象。一旦铜进入有源区,就会对器件造成不可逆的损坏,使得芯片无法正常工作。比如,在一些高端芯片制造过程中,由于铜的扩散问题,导致芯片的良品率大幅下降。

2.刻蚀难题:常规的等离子体刻蚀工艺并不适用于铜,很难通过这种刻蚀方式得到精确的铜图案。这给芯片制造过程中的图形化工艺带来了极大的困难,增加了芯片制造的难度和成本。

3.氧化问题:铜在空气中容易被氧气氧化,而且氧化铜无法形成有效的保护层来阻止铜的进一步氧化。这不仅会影响铜的性能,还可能对芯片的整体稳定性产生负面影响,降低芯片的可靠性。

面对这些挑战,科研人员和工程师们积极探索解决方案,最终找到了一系列行之有效的对策:

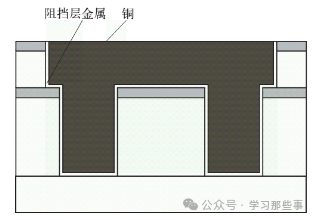

1.扩散阻挡:为了阻止铜的扩散,在进行铜工艺之前,先沉积一层阻挡层,如钽和氮化钽。这些阻挡层能够有效地阻挡铜的扩散,保护芯片中的其他材料不被铜污染。在与源、漏和栅区接触时,依然采用传统的钨塞,从根本上杜绝了铜沾污硅的问题。

2.图形化工艺创新:针对铜不易被刻蚀成图形的特性,人们采用了一种全新的图形化工艺。先刻蚀介质层,然后再将铜镶嵌其中,巧妙地避开了直接刻蚀铜的难题,成功得到了所需的铜图形结构。这种创新工艺不仅解决了铜的刻蚀问题,还提高了图形的精度和质量。

3.氧化防护:在制作最上层的金属时,仍然选用传统的铝基金属。这是因为铝表面氧化后会形成一层致密的氧化铝保护膜,能够有效地保护下面的金属,防止其继续被氧化。例如,在一些电子设备的外壳中,采用铝基金属作为表面材料,既美观又能保护内部的电子元件。

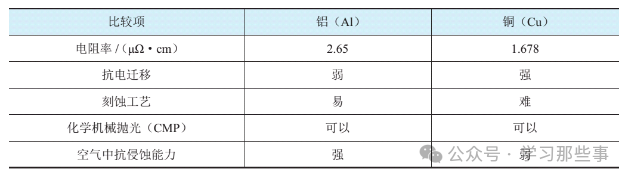

下表总结了铝和铜的特性以及工艺特点。

铝、铜的特性及工艺特点对比

硅化物

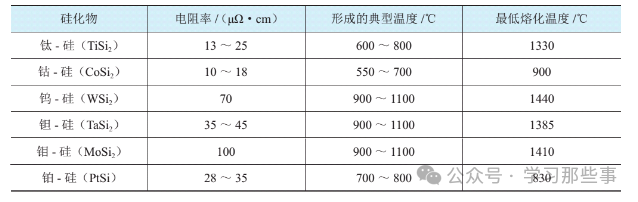

除了铝和铜,硅化物(silicide)在集成电路中也有着重要的应用。硅化物是硅与难熔金属发生化学反应后形成的一种具有热稳定性的金属化合物。硅化物之所以备受关注,是因为它具有较低的电阻率,这对于减小源漏和栅区硅的接触电阻起着至关重要的作用,能够显著提升芯片的性能。常用来形成硅化物的金属有钛、钴、钨等,它们及其他硅化物的特性如下表所示,这些特性为芯片制造工艺的选择和优化提供了重要依据。

硅化物的特性

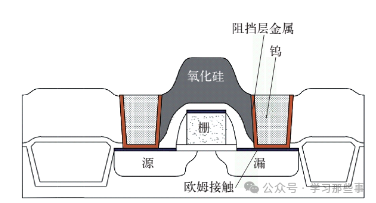

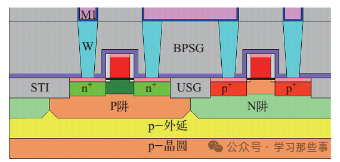

在硅材料表面对金属进行加热处理,以此形成符合预期的电接触界面,这一界面被称作欧姆接触(如下图所示),而整个工艺过程则被叫做烧结或者退火。在当下的芯片设计领域,现代工艺常常利用难熔金属与硅片上暴露出来的源区、漏区以及多晶硅栅极发生化学反应,从而生成硅化物。这种技术被命名为自对准硅化物技术,其独特之处在于这些难熔金属仅会与硅或者多晶硅发生反应,而不会和二氧化硅产生反应。正因如此,生成的硅化物能够精准地与源区、漏区以及栅极实现对准,极大地提升了接触的精准度。自对准硅化物技术提供了一种能够有效降低接触电阻、增强附着稳固性以及构建稳定接触结构的工艺方案,对于提高芯片性能有着不可或缺的作用。

欧姆接触

常见的硅化物包含钛 - 硅(TiSi?)、钴 - 硅(CoSi?)、钨 - 硅(WSi?)、钽 - 硅(TaSi?)、钼 - 硅(MoSi?)、铂 - 硅(PtSi) 等。当难熔金属与多晶硅发生反应生成的硅化物,我们将其称为多晶硅化物。值得注意的是,多晶硅化物的电阻率相较于多晶硅要低出许多。倘若直接采用掺杂多晶硅来作为栅电极,由于其具有较高的电阻率,大约为 500μΩ?cm ,这必然会导致 RC 延迟显著增加,进而影响芯片的运行速度和性能。所以,必须借助多晶硅化物来降低电阻率,减少 RC 延迟,以满足芯片对于高性能的需求。

金属填充塞

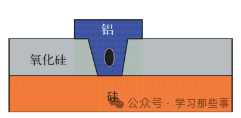

金属填充塞在集成电路中扮演着连接不同金属层,或者连接第一层金属与硅的重要角色,它是一种金属填充物。在早期的集成电路制造中,曾经使用铝作为金属填充塞的材料。然而,随着器件尺寸不断朝着更小的方向发展,铝电迁移的问题逐渐凸显。如下图所示,铝电迁移会造成空洞,而这些空洞极有可能引发断路风险,严重影响集成电路的稳定性和可靠性。

铝电迁移造成的空洞

鉴于钨(W)拥有极高的熔点,即使处于高电流密度的工作环境下,其扩散率依旧很低,不会像铝那样产生空洞和小丘,也不存在电迁移现象。此外,钨还具备出色的台阶覆盖能力以及在高深宽比间隙中的填充能力。基于这些优势,钨常常被用作第一层金属与下方硅之间的连接材料,这种连接结构被称为钨塞(如下图所示) 。在铜双大马士革工艺问世之前,钨也是连接不同金属连线的优先选择材料。钨属于难熔材料,它的熔点高达 3417℃,在 20℃时,其体电阻率为 52.8μΩ?cm。

CMOS器件中的钨塞

钨塞的制作工艺有着严谨的流程:首先要进行氧化硅的沉积操作,并将其表面处理至平坦状态;接着通过光刻和刻蚀技术,精确地形成接触孔的图案;随后沉积一层阻挡层,用于防止后续工艺中材料之间的相互干扰;最后进行钨的淀积,并再次进行平坦化处理,以确保整个结构的平整和稳定。

阻挡层金属

阻挡层金属,从其名称便可以理解,它是用于阻挡金属扩散的其他金属或者金属化合物。在进行金属淀积或者制作金属塞之前,通常都需要先沉积一薄层阻挡层金属,目的是防止上下层材料相互混合,避免对集成电路的性能产生不良影响。

对于阻挡层金属,有着多方面严格的要求。除了需要具备卓越的阻挡扩散能力之外,还应当具备抗电迁移的性能,以保证在电流作用下自身结构的稳定性;具备抗侵蚀能力,能够抵御外界环境和工艺过程中的各种侵蚀;具备抗氧化能力,防止在空气中被氧化而影响性能;要有良好的附着特性,确保与其他材料紧密结合;拥有高导电率,保障电流的顺畅传输;具有很低的欧姆接触电阻,减少接触电阻带来的能量损耗;并且要求它在高温环境下依然能够保持良好的稳定性,不发生性能劣化。例如,在沉积钨之前,常常会先沉积氮化钛(TiN)和钛(Ti)作为阻挡层和促黏层,以满足上述各项要求。在沉积铜之前,一般会预先沉积氮化钽和钽作为阻挡层(如下图所示) 。氮化钽具有电阻率低、熔点高、界面稳定、晶格和晶界扩散的激活能高等一系列优异的性能,使其成为当前制备铜扩散阻挡层的首选材料,为铜在集成电路中的应用提供了可靠的保障。

阻挡层金属

END 转载内容仅代表作者观点 不代表中国科学院半导体所立场

编辑:小帅 责编:六块钱的鱼 投稿邮箱:weixin@semi.ac.cn 往期推荐 1.半导体所在仿生覆盖式神经元模型及学习方法研究方面取得进展 2.半导体所在反型结构钙钛矿太阳能电池方面取得重要进展 3.芯片为什么用铜作为互联金属? 4.关于芯片的7nm到底是个啥 5.硅基集成光量子芯片技术 6.量子反常霍尔效应有多反常?或将带来下一次信息技术革命!

原文标题:集成电路工艺中的金属

文章出处:【微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

-

集成电路

+关注

关注

5430文章

12139浏览量

368966 -

芯片制造

+关注

关注

11文章

695浏览量

29815 -

金属

+关注

关注

1文章

615浏览量

24778

原文标题:集成电路工艺中的金属

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

中国集成电路大全 接口集成电路

概伦电子集成电路工艺与设计验证评估平台ME-Pro介绍

CMOS集成电路的基本制造工艺

集成电路设计中静态时序分析介绍

集成电路外延片详解:构成、工艺与应用的全方位剖析

集成电路工艺中的金属介绍

集成电路工艺中的金属介绍

评论