磨削和研磨等磨料处理是生产半导体芯片的必要方式,然而研磨会导致芯片表面的完整性变差。因此,抛光的一致性、均匀性和表面粗糙度对生产芯片来说是十分重要的。

近日,第九届国际第三代半导体论坛&第二十届中国国际半导体照明论坛于厦门召开。期间,“碳化硅衬底、外延生长及其相关设备技术”分会上,北京国瑞升科技集团股份有限公司 高级工程师 苑亚斐 做了“碳化硅衬底粗研磨和精研磨工艺及耗材技术”的主题报告并就公司研发的碳化硅衬底研磨抛光新工艺、新产品进行探讨交流。

第三代半导体材料,以碳化硅和氮化镓为代表,针对这两种材料的研磨和抛光,国瑞升可提供全套的产品和整体的解决方案,可向衬底客户提供化合物半导体粗磨液、精磨液、粗抛液和CMP抛光液;可向后道外延芯片背面减薄客户提供减薄耗材产品,以及匹配的粗抛垫和精抛垫。

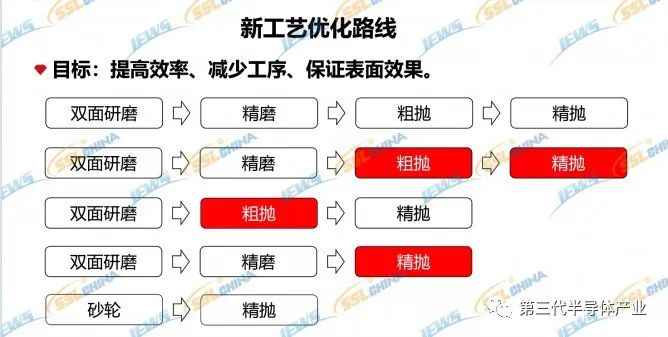

报告指出,新工艺优化路线主要是提高效率、减少工序、保证表面效果。碳化硅衬底粗抛和精抛涉有的主要产品有:粗抛涉及氧化铝抛光液、金刚石抛光液、纳米金刚石抛光液,精抛涉及双组份抛光液、高效抛光液。SiC研磨抛光用相关耗材,涉及双面研磨用悬浮液,金刚石研磨液(单晶、类多晶、多晶),氧化铝粗抛液(酸性、碱性),双面研磨用悬浮剂,双组份精抛液,高效精抛液,CMP抛光液,固态蜡等。

审核编辑:刘清

-

CMP

+关注

关注

6文章

157浏览量

26871 -

碳化硅

+关注

关注

25文章

3095浏览量

50747 -

半导体芯片

+关注

关注

61文章

936浏览量

71552

原文标题:国瑞升苑亚斐:碳化硅衬底材料研磨抛光耗材和工艺技术

文章出处:【微信号:第三代半导体产业,微信公众号:第三代半导体产业】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【新启航】如何解决碳化硅衬底 TTV 厚度测量中的各向异性干扰问题

自动对刀技术对碳化硅衬底切割起始位置精度的提升及厚度均匀性优化

碳化硅衬底切割进给量与磨粒磨损状态的协同调控模型

基于进给量梯度调节的碳化硅衬底切割厚度均匀性提升技术

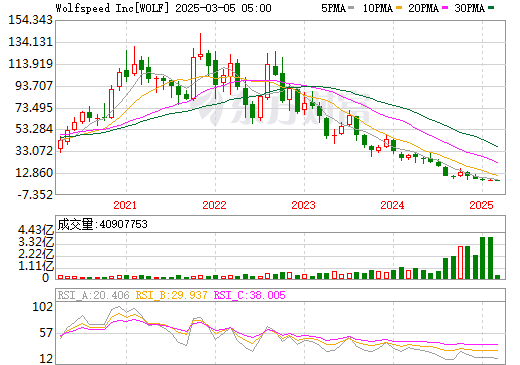

CREE(Wolfspeed)的垄断与衰落及国产碳化硅衬底崛起的发展启示

碳化硅衬底的生产过程

碳化硅衬底的特氟龙夹具相比其他吸附方案,对于测量碳化硅衬底 BOW/WARP 的影响

不同的碳化硅衬底的吸附方案,对测量碳化硅衬底 BOW/WARP 的影响

碳化硅衬底的环吸方案相比其他吸附方案,对于测量碳化硅衬底 BOW/WARP 的影响

碳化硅衬底,进化到12英寸!

碳化硅衬底材料研磨抛光耗材和工艺技术

碳化硅衬底材料研磨抛光耗材和工艺技术

评论