Vivado? Design Suite 2015.3基于 Vivado HLS C /C++ 的 IP 生成与验证不仅可显著减少开发工作与时间,同时还可最大化代码复用。使用 IP 集成器和自动 AXI 互联可轻松将 HLS IP 与赛灵思即插即用 IP 及 IP 子系统进行集成。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1797浏览量

132586 -

C++

+关注

关注

22文章

2119浏览量

75733 -

design

+关注

关注

0文章

162浏览量

46772

发布评论请先 登录

相关推荐

热点推荐

Vivado无法选中开发板的常见原因及解决方法

在使用 AMD Vivado Design Suite 对开发板(Evaluation Board)进行 FPGA 开发时,我们通常希望在创建工程时直接选择开发板,这样 Vivado

AMD Vivado Design Suite 2025.1现已推出

AMD Vivado Design Suite 2025.1 现已推出,支持 AMD Spartan UltraScale+ 和新一代 Versal 器件。这一最新版本还新增了多项功能

如何使用One Spin检查AMD Vivado Design Suite Synth的结果

本文讲述了如何使用 One Spin 检查 AMD Vivado Design Suite Synth 的结果(以 Vivado 2024.2 为例)。

AMD Versal自适应SoC器件Advanced Flow概览(下)

在 AMD Vivado Design Suite 2024.2 版本中,Advanced Flow 自动为所有 AMD Versal 自适应 SoC 器件启用。请注意,Advanced Flow

Vivado Design Suite用户指南: 设计分析与收敛技巧

电子发烧友网站提供《Vivado Design Suite用户指南: 设计分析与收敛技巧.pdf》资料免费下载

发表于 01-15 15:28

?0次下载

Vivado Design Suite用户指南:逻辑仿真

电子发烧友网站提供《Vivado Design Suite用户指南:逻辑仿真.pdf》资料免费下载

发表于 01-15 15:25

?0次下载

Vivado之实现布局布线流程介绍

一、前言 本文将介绍Vivado进行综合,以及布局布线的内部流程,熟悉该流程后结合Settings中对应的配置选项,对于时序收敛调试将更具有针对性。 二、Implementation(实现) 实现

AMD Vivado Design Suite 2024.2全新推出

AMD Vivado Design Suite 2024.2 全新推出,使用 AMD Versal Adaptive SoC 进行设计的重大改进。此版本为 AMD Versal 自适应 SoC

U50的AMD Vivado Design Tool flow设置

AMD Alveo 加速卡使用有两种流程,AMD Vitis Software Platform flow 和 AMD Vivado Design Tool flow。比较常见的是 Vitis

每次Vivado编译的结果都一样吗

tool inputs? 对大多数情况来说,Vivado编译的结果是一样的,但要保证下面的输入是一样的: Design sources Constraints Tcl scripts and command

AMBA AXI4接口协议概述

AMBA AXI4(高级可扩展接口 4)是 ARM 推出的第四代 AMBA 接口规范。AMD Vivado Design Suite 2014 和 ISE Design

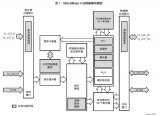

MicroBlaze V软核处理器的功能特性

本指南提供了有关 AMD Vivado Design Suite 中包含的 32 位和 64 位 MicroBlaze V 软核处理器的信息。该文档旨在用作为处理器硬件架构的指南,随附《RISC-V 指令集手册》第一卷和第二卷。

AMD Vivado Design Suite 2024.1全新推出

AMD Vivado Design Suite 2024.1 可立即下载。最新版本支持全新 AMD MicroBlaze V 软核处理器,并针对 QoR 和 Dynamic Function

Vivado Design Suite 2015.3的新功能介绍

Vivado Design Suite 2015.3的新功能介绍

评论