AMD Alveo 加速卡使用有两种流程,AMD Vitis Software Platform flow 和 AMD Vivado Design Tool flow。比较常见的是 Vitis flow,运行在固定的 Platform(官方提供的平台)上面,优点是比较方便使用开发,不用考虑底层的硬件情况。与之对应的即是 Vivado flow,对于 RTL 的设计者来说,这种流程更加熟悉。但是对于定制化的板卡,它的接口和管脚已经固定,相关的电气参数也是固定的。例如 U50 主要的物理接口有:“PCI Express Gen3 x16, 2 x Gen4 x8, CCIX”、“ Network Interfaces 1x QSFP28 (100GbE) ”等。

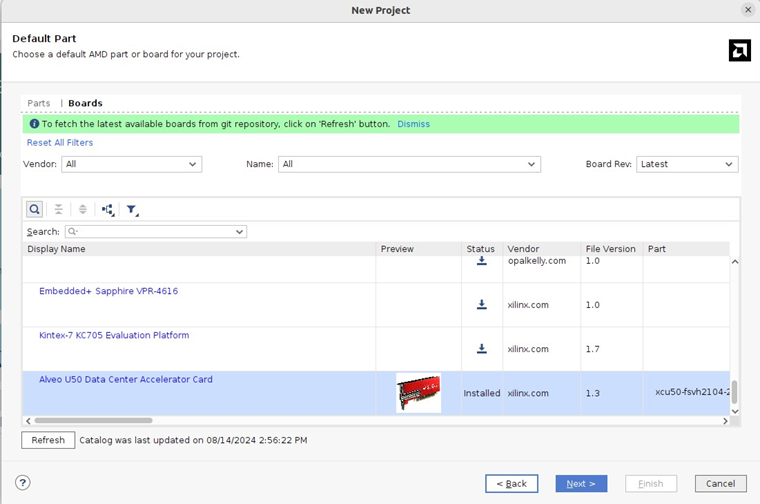

如果使用 Vivado flow,现在的 Vivado 自带的 Board 并不包含 Alveo 板卡的 Board file,也不能在 Vivado 中从 Gihub 上下载 Board files。所以首先需要在下面链接中单独下载 U50 的 XDC 文件和 “Boad file Alveo U50 Data Center Accelerator Card”。然后把 U50 的 Board file 解压并放到

Boad file Alveo U50 Data Center Accelerator Card:

https://www.amd.com/en/products/accelerators/alveo/u50/a-u50-p00g-pq-g.html#tabs-c767fb116b-item-e9279ab834-tab

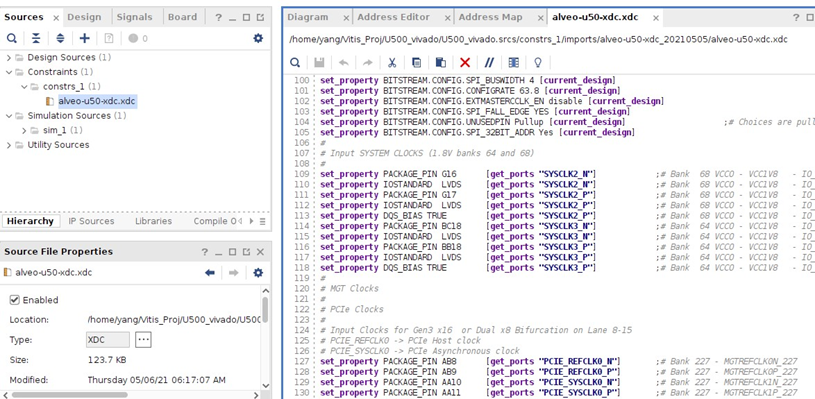

Alveo 有多种的时钟用于 PCIe,QSFP 等,U50 的 XDC 文件已经帮用户定义好了相应的时钟管脚和电平参数,当然还有一些其他接口,如 I2C 等具体可参考 “Introduction ? Alveo U50 Data Center Accelerator Card User Guide (UG1371) ? Reader ? AMD Technical Information Portal”:

https://docs.amd.com/r/en-US/ug1371-u50-reconfig-accel

所以有必要在 Vivado 的 Add Sources 添加该 XDC 文件。

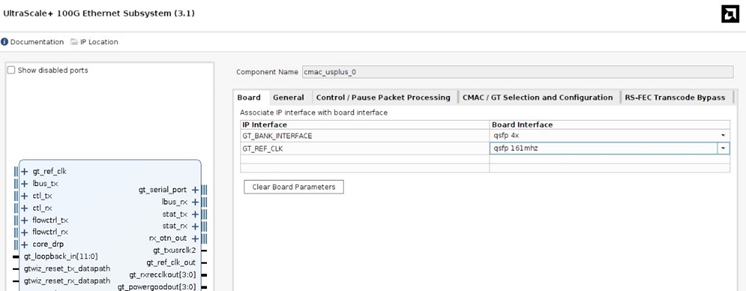

当这些都设置好后,便可以进行设计。创建 Block Design,添加例如 100G Ethernet IP,配置 IP 的时候就可以看到 Board 下有 GT_BANK_INTERFACE 和 GT_REF_CLK 的配置,可以选择对应的 qsfp 4x 和 qsfp 161mhz。

随后就可以在此基础上进行自己所需的设计,当然如果不需要 PCIe 等功能也可以不用添加该 IP。Vivado flow 相对于 Vitis flow,灵活性大大提高。

-

amd

+关注

关注

25文章

5594浏览量

136574 -

接口

+关注

关注

33文章

9032浏览量

153974 -

加速卡

+关注

关注

1文章

64浏览量

11198 -

Vivado

+关注

关注

19文章

835浏览量

68970

原文标题:开发者分享|U50 的 AMD Vivado? Design Tool flow 设置

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何使用One Spin检查AMD Vivado Design Suite Synth的结果

【AMD】Physical Design Engineer

AMD热招 Physical Design Engineer

【AMD】Physical Design Engineer

【AMD】Design Verification Engineer

如何在AMD Vivado? Design Tool中用工程模式使用DFX流程?

AMD Vivado Design Suite 2024.1全新推出

AMD Vivado Design Suite 2024.2全新推出

AMD Versal自适应SoC器件Advanced Flow概览(上)

AMD Versal自适应SoC器件Advanced Flow概览(下)

U50的AMD Vivado Design Tool flow设置

U50的AMD Vivado Design Tool flow设置

评论