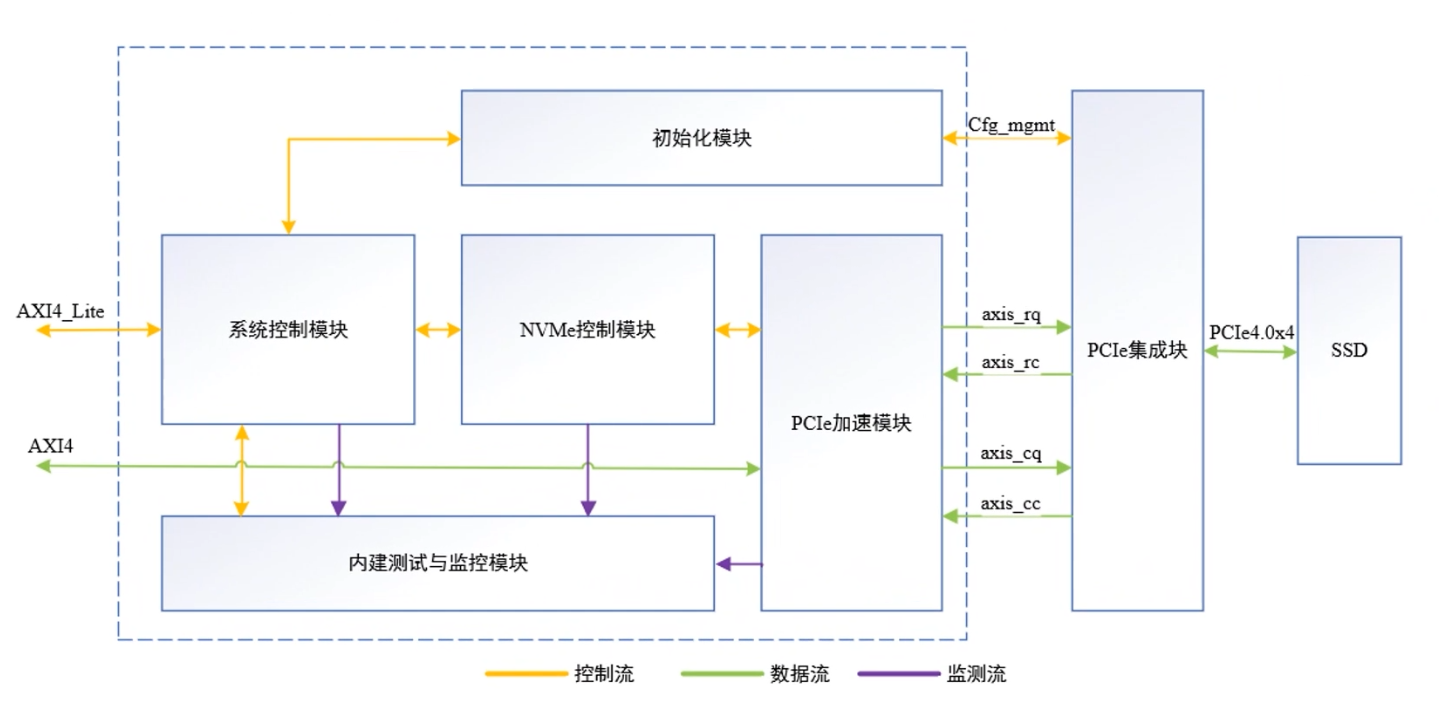

NVMe over PCIe采用 AXI4-Lite 接口、AXI4 接口和 PCIe3.0X4 接口,其中AXI4-Lite 和 AXI4 总线接口均可抽象为总线事务,而 PCIe 接口信号可被抽象为 PCIeTLP 事务,因此为了方便的在事务层构建复杂的测试用例,项目基于 UVM 搭建验证平台进行功能验证。

图1 验证平台架构图

在验证平台中将 PCIE 集成块从待测试设计(Design Under Test,DUT)中剥离,以 PCIE 集成块接口作为 DUT 接口执行仿真。一方面,因为 PCIe 接口采用 PCIE 集成块作为物理层和数据链路层驱动,而 PCIe 物理层和数据链路层的仿真十分复杂,需要使用成熟的验证知识产权(Verification IP,VIP)保证仿真的准确性和效率,这一类的 VIP 通常十分昂贵并且复杂;另一方面,PCIE 集成块是 Xilinx 提供的过了充分验证的硬核 IP,因此在验证过程中可以只使用其接口进行模拟,这将极大减小验证平台复杂度和构建难度,同时对验证的完备性影响较小.

验证平台由 UVM 验证包、DUT、AXI BRAM IP 和 NVMe 子系统模型组成。UVM验证包用于构建测试用例、提供激励、监测接口、对比分析统计测试结果;DUT 为待测试对象即 NoP 逻辑加速引擎;AXI BRAM IP 用于模拟外部存储,对接 DUT 的AXI4 数据总线;NVMe 子系统模型(NVMe Subsystem Model)是自主设计的用于模拟 PCIe 链路设备和 NVMe 设备的功能模型。

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望

-

PCIe

+关注

关注

16文章

1368浏览量

85874 -

FGPA

+关注

关注

1文章

27浏览量

16292 -

高速存储

+关注

关注

0文章

14浏览量

6032 -

nvme

+关注

关注

0文章

272浏览量

23340

发布评论请先 登录

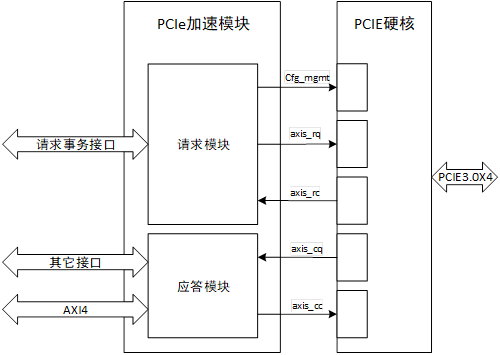

NVMe高速传输之摆脱XDMA设计20: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计20: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计17:PCIe加速模块设计

NVMe高速传输之摆脱XDMA设计14: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计14: PCIe应答模块设计

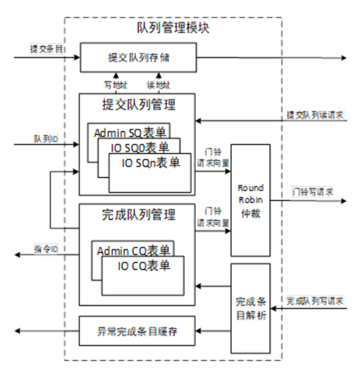

NVMe IP高速传输却不依赖XDMA设计之九:队列管理模块(上)

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

NVMe高速传输之摆脱XDMA设计九:队列管理模块设计(上)

NVMe IP高速传输却不依赖XDMA设计之八:系统初始化

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

评论