在电子电路系统设计中,工程师处理ESD有时候总觉得没有头绪,主要原因是ESD测试难以量化,每次测试的结果也会存在差异,所以凭感觉处理起来很‘玄学’。 简单说起来就是ESD对系统内部存在干扰,但处理起来常常就是一团乱麻,监测不到ESD泄放路径。单从电路增加ESD防护设计维度有时候是无法达到目的,所以PCB设计是解决ESD防护问题中非常重要的一环,但必要时还是要配合ESD器件共同达到抑制的目的。

无论是普通电路系统还是高速电路系统,对于EMC的处理都很有必要,今天就分享几个PCB Layout几个原则,可以大大减小EMC出现问题的概率。PCB布局的ESD防护思路是:敏感的信号或者电路远离静电放电测试点,信号环路面积最小化噪声耦合,降低参考地平面电位差保持信号参考电平稳定。

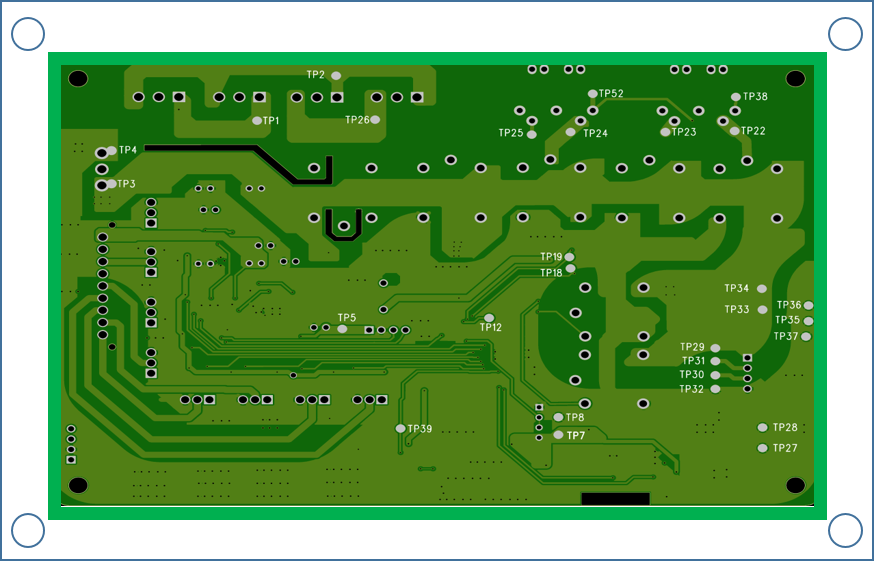

图1.PCB Layout示意图

如图1所示,PCB Layout设计建议参考

1. 单层PCB设计时,设置良好的接地平面和电源平面,信号线尽可能紧靠电源平面层或接地平面,保证信号回流时的通路以最短,信号环路最小的原则。

2. 多层PCB层叠设计必须保证比较完整的GND平面,所有的 ESD泄放路径直接通过过孔连接到这个完整的GND平面,其他层尽可能多的铺 GND。

3. 在PCB四周增加地保护环路,关键信号(RESET/Clock等)与板边距离不小于 5mm,同时必须与布线层的板边GND铜皮距离不小于 10mils。

4. 在电源和接地之间设计高频旁路电容,要求等效串联电感值(ESL)和等效串联电阻(ESR)越小越好

5. 对于部分ESD 整改难度较大的IO,可将IO GND独立出来,与电源GND用磁珠连接,以防止ESD能量进入GND。

另外,在PCB布局时做好敏感器件的保护、隔离,一些敏感模块如射频、音频、存储器可以添加屏蔽罩。但屏蔽罩的整体成本太高,ESD保护器件具有更好的性价比,但如何选用合适的ESD器件才是关键,配合PCB的线路设计达到防护目的。

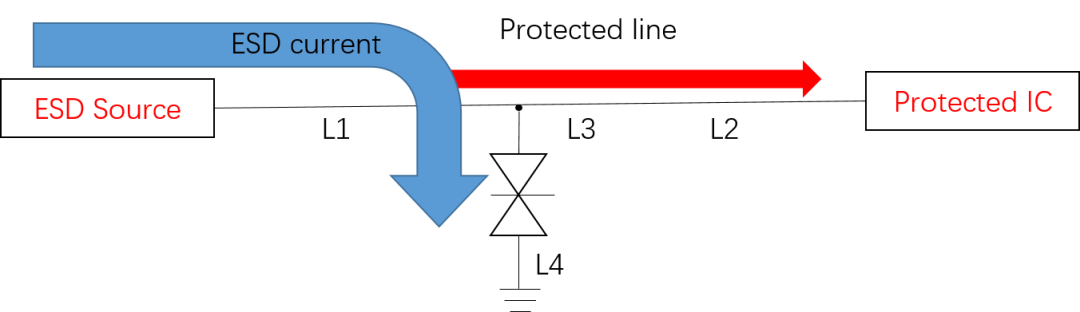

图2.ESD泄放路径避免能量进入保护电路

放电事件通常通过接口(如连接线)或人工端口(如USB、音频)迫使电流 IESD (图2)迅速进入系统。使用ESD二极管保护系统免受ESD影响,取决于ESD二极管能否将 IESD 分流到地,在选用ESD器件时需要注意如下参数:

1.工作电压 (VRWM)

VRWM工作电压是指建议器件工作电压范围,应用电路最高电压超过该值时会导致漏电流增大,从而损坏器件和影响系统运行。建议电路应用电压≤ ESD 器件的工作电压VRWM。

2.结电容(Cj)

ESD器件与信号并联使用,而ESD半导体设计时的寄生电容,对于高速信号应最大限度地减小结电容Cj以保持信号完整性。

3. IEC 61000-4-2等级(Contact discharge/ Air discharge)

IEC61000-4-2等级体现器件在接触放电和空气放电的稳健性。接触放电是指用静电枪向ESD器件放电时该器件可承受的最大电压。空气放电是指使用静电枪空气间隙向ESD器件放电时该器件可承受的最大电压。

4.ESD器件通道数

ESD器件有单通道和多通道不同封装类型。多通道是内部集成多个单通道器件,根据应用需求,多通道器件可实现更小尺寸方案并节省PCB空间,当然,单通道器件可提供更高的设计灵活性。

5.单向与双向

双向ESD器件可同时具有正负工作电压的电路中(±3.3V等),因此,双向ESD器件可支持数据信号在正负电压之间切换的接口(如模拟信号/RS233等)。单向ESD只有工作在正电压范围,但具有更好的负钳位。

6. 钳制电压(Vc)

钳制电压表示瞬态脉冲下作用于ESD器件时2端的压降,钳制电压越低意味能更好的保护后级的电子元件。瞬态测试包含静电和浪涌,不同测试条件下钳制电压不同,选型前确认具体测试需求和后级极限损坏电压,保证器件选型的合理性

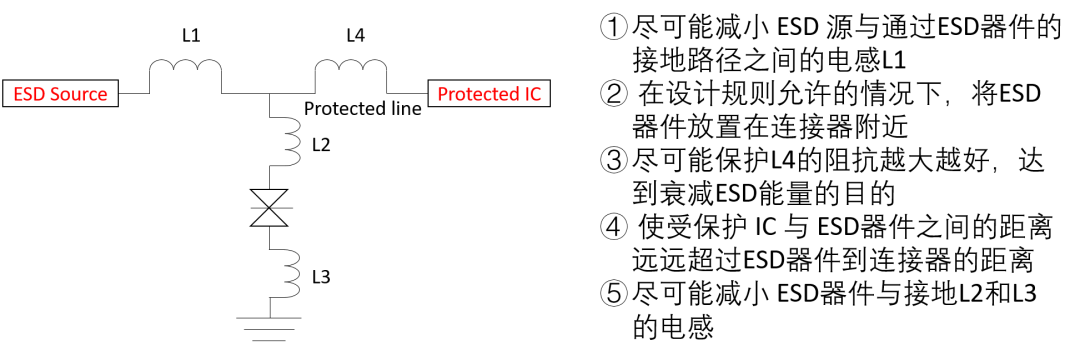

综上,要想从PCB布局+ESD二极管实现最好的静电防护,很大程度上需要从整机系统上优化设计。因为设计人员无法控制 IESD,所以降低对地阻抗是将钳制电压最小化的主要方法。设计建议如下(图3)。

图3.ESD二极管PCB优化建议

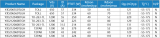

产品推荐

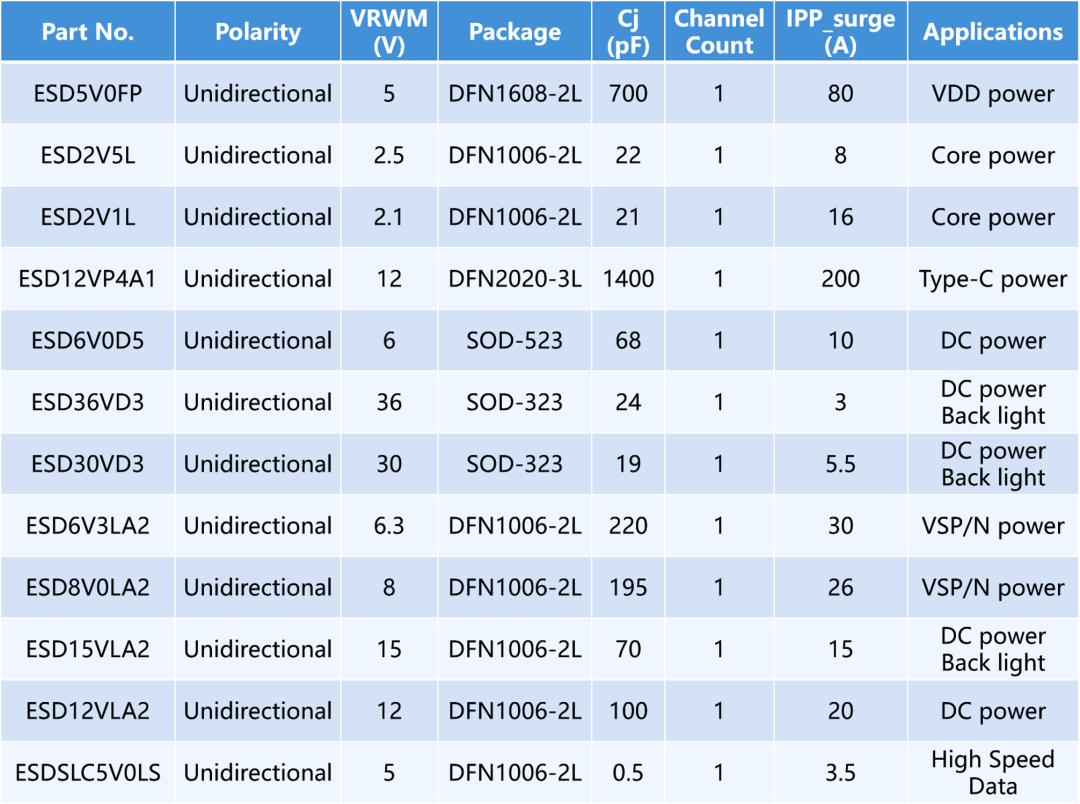

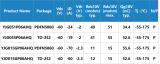

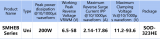

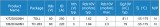

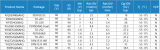

扬杰科技推出应用于电源和信号单向TVS方案,在瞬态脉冲负压情况下,单向ESD器件约-0.7V会Forward导通,而双向结构ESD器件无论在正压还是负压条件下,2个方向均要击穿才会导通;如果电源或主芯片为高阶制程,电源或I/O防护电路变得十分脆弱,在负压条件下会导致主芯片内部的衬底二极管率先导通而烧毁,从而导致主芯片损坏。表1是我司新开发的单向结构ESD和具体应用,以应对在负压瞬态脉冲下敏感问题 。

-

ESD

+关注

关注

50文章

2314浏览量

176351 -

PCB设计

+关注

关注

396文章

4842浏览量

91435 -

硬件电路

+关注

关注

39文章

261浏览量

29878 -

Pcb layout

+关注

关注

6文章

100浏览量

29662 -

扬杰科技

+关注

关注

1文章

128浏览量

11389

原文标题:干货分享 | 如何通过硬件电路优化降低ESD干扰

文章出处:【微信号:yangjie-300373,微信公众号:扬杰科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

扬杰科技推出用于汽车电子的P60V MOSFET产品

提升AR眼镜防护能力,扬杰科技TVS技术革新

扬杰科技推出SOD-323HE封装TVS新品

扬杰科技推出用于清洁能源的N60V MOSFET产品

扬杰科技拜访维扬经济开发区管委会

博世集团莅临扬杰科技参观交流

扬杰科技亮相PCIM Europe 2025 以硬核技术驱动能源变革

如何布线才能降低MDDESD风险?PCB布局的抗干扰设计技巧

扬杰科技N60V SGT MOSFET产品介绍

扬杰科技全资子公司MCC(越南)工厂正式通线

扬杰科技推出全新SiC MOSFET产品

扬杰科技分享如何通过硬件电路优化降低ESD干扰

扬杰科技分享如何通过硬件电路优化降低ESD干扰

评论