介绍

电容-电压 (C-V) 测量广泛用于半导体材料和器件表征,可提取氧化物电荷、界面陷阱、掺杂分布、平带电压等关键参数。传统基于 SMU 施加电压并测量电流的准静态方法适用于硅 MOS,但在SiC MOS 器件上因电容更大易导致结果不稳定。为解决这一问题,Keithley 4200A-SCS 引入Force-I QSCV 技术,通过施加电流并测量电压与时间来推导电容,获得更稳定可靠的数据。

在SiC功率MOS器件上使用Force-I QSCV技术的一些优点包括:

仅需要一个带前置放大器的SMU(其他方法需要两个)。

施加电流比施加电压方法更快。

向被测器件(DUT)施加恒定直流电流可实现稳态条件,这与可能导致测量设备动态变化的电压步进不同。

测量电压:避免了使用低输出阻抗模式的仪器推导电容时的不稳定性问题。

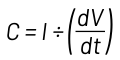

根据以下公式计算电容:

执行开路校准。

校准泄漏。

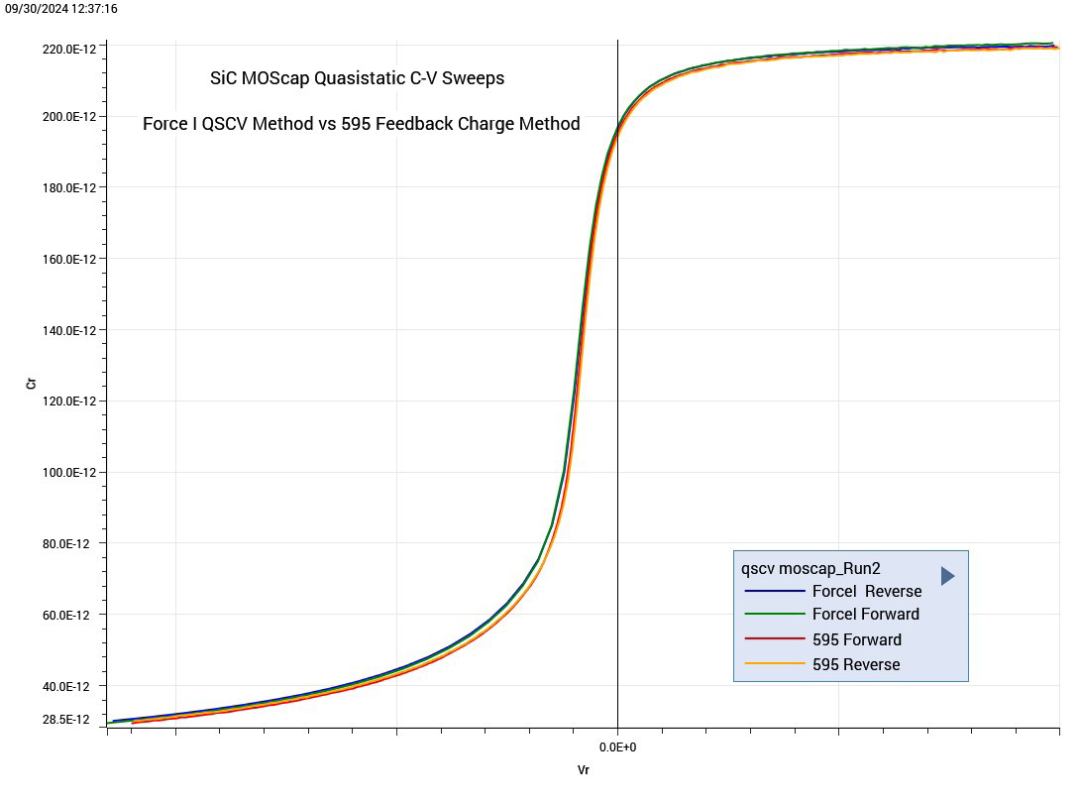

提供与使用吉时利595准静态C-V表进行C-V测量相似的结果。

研究是否可以使用正向和反向曲线提取DIT。

该技术适用于大于20pF的较大电容。

从Clarius V1.14软件版本开始,执行Force-I QSCV技术的测试已包含在吉时利4200A-SCS附带的Clarius软件中。这些测试是4200A-SCS Clarius软件套件提供的很多测试库中的一部分。运行Clarius中的Force-I QSCV测试需要一个带前置放大器的 SMU。

本应用文档介绍了Force-I QSCV技术, 解释了如何在Clarius软件中使用这些测试,将该技术与其他方法进行了比较,并从正向和反向C-V扫描中推导了SiC MOSFET内部电荷的计算方法。

使用三步法的Force-I QSCV技术

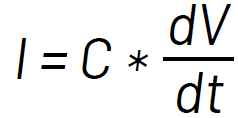

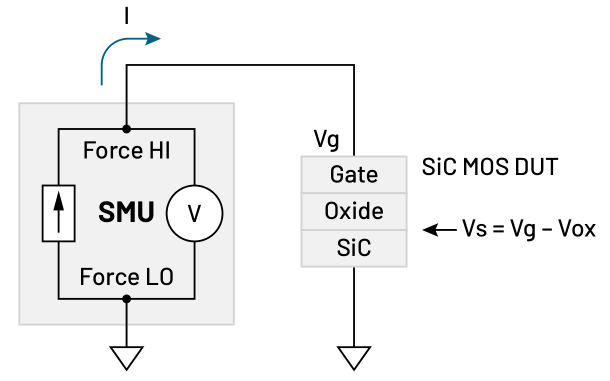

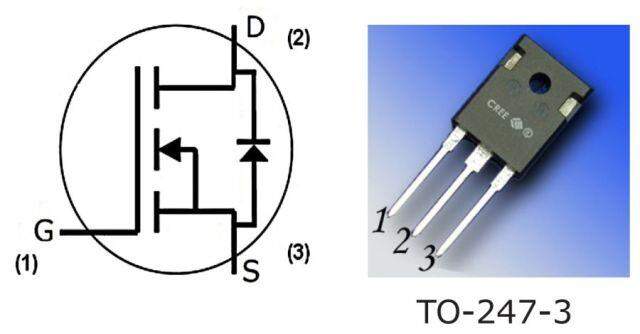

Force-I QSCV技术使用一个带前置放大器的SMU来推导SiC MOSFET或MOS电容的准静态C-V特性。SMU是一种能够施加和测量电流和电压的仪器。如图1所示,SMU的Force HI端子连接到功率MOSFET的栅极,SMU的Force LO端子连接到短接在一起的漏极和源极端子。

图1. 功率MOSFET在SMU的HI和LO端子之间的连接图

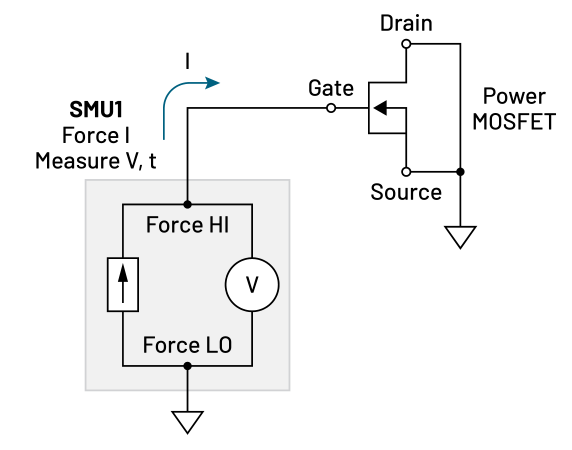

施加电流准静态C-V方法通过施加正负电流并测量电压随时间的变化,使用三步法推导正向和反向C-V曲线。恒定电流可精确控制提供给器件的总电荷(Q= ∑ I×dt)。与可能导致测量设备动态变化的电压步进不同,使用恒定电流可使仪器达到稳态条件。三步法的电压和电流时序图如图2所示。

图2. Force-I QSCV测试的电流和电压时序图

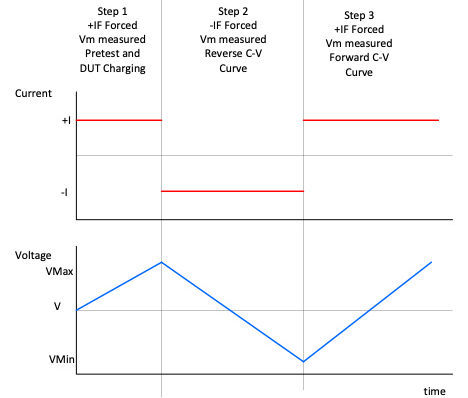

由于施加了正负电流,因此可以提取正向和反向C-V曲线。推导出的被测器件电容 (C) 计算如下:

因此,

其中:I = 施加电流 (A),V = 测量电压 (V),t = 时间 (s),C = 推导出的电容 (F)。

使用Clarius软件进行Force-I QSCV测试

使用Force-I QSCV方法的测试位于测试库和项目库中,可以在 “选择” 视图中通过搜索 “force-I QSCV” 或“qscv”找到。 在测试库中找到测试后,可以选择它们并将其添加到项目树中。测试库包括适用于 SiCMOSFET(sic-mosfet-force-i-qscv)和SiC MOS电容 (sic-moscap-force-i-qscv) 的测试。这些特定测试可以用于其他器件,也可以通过向项目树添加自定义测试(UTM)并使用QSCVulib用户库中的force_current_CV用户模块来创建新测试。

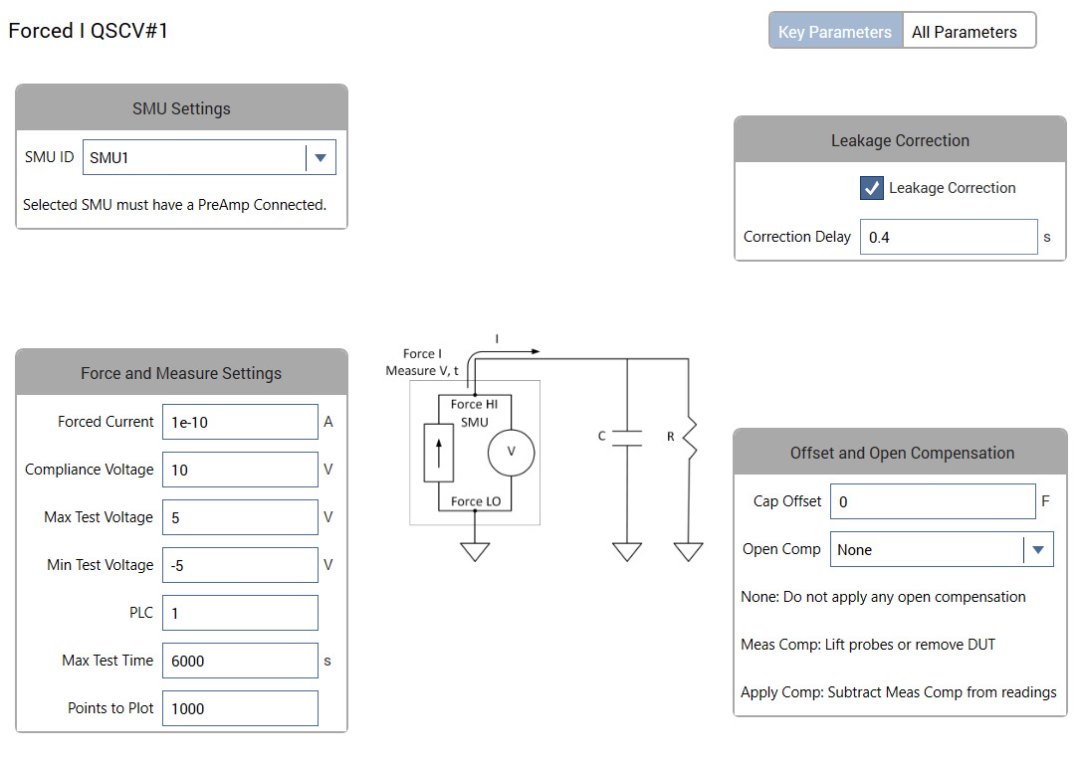

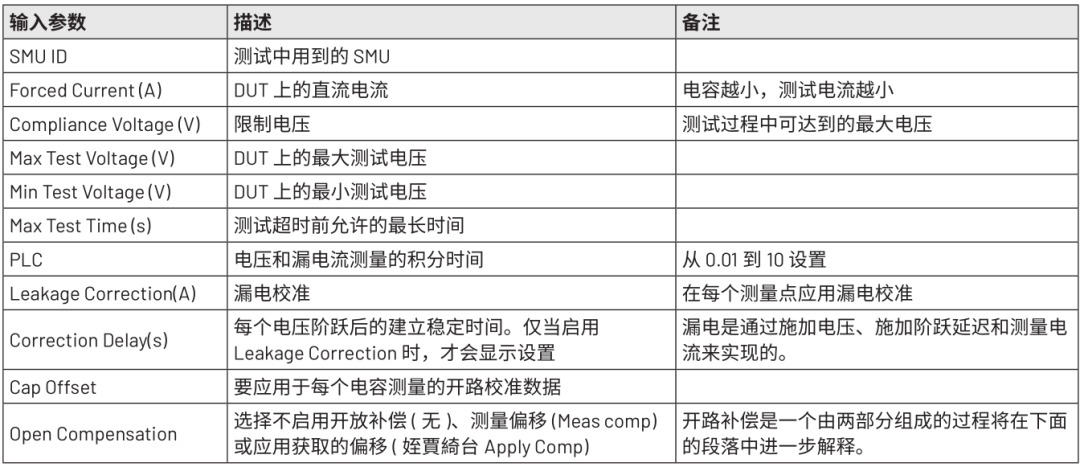

表1列出了所有输入参数及其描述和注释。

以下描述了Force-I QSCV测试的输入参数、输出参数以及结果分析。

输入参数

Force-I QSCV测试的输入参数显示在Clarius的“配置”视图中,如图3所示。用户设置最大和最小测试电压、输出电流和时序参数。开路补偿和泄漏校准为可选功能,也可以在 “配置” 视图中应用。

图3. 在Clarius中配置Force-I QSCV测试的视图

表1 施加电流的QSCV测试的输入参数

关于部分输入参数的进一步信息

■施加电流:选择合适的施加电流可能需要进行一些试验,也可能出现一些错误。对于SiC MOSFET,施加电流通常在数百皮安到纳安范围内。测试电流的大小应约为要测量的最大电容大小的三分之一。例如,如果最大电容为2.4×10-9F,则测试电流应约为800×10-12A。测试电流过低或过高都可能导致错误结果。

测试电流过低可能会导致器件充电时间过长,测量时间也会更长。电流过高会导致测试在几个测量点后达到限制电压,并在分析视图的表格中返回错误。

开路补偿的施加电流应在皮安或更小范围内。电流过高会导致SMU进入电压限制状态,且无法收集到足够数量的测量值。电流过低会导致测量非常缓慢。

■PLC:PLC时序设置调整测量的积分时间,可在0.01到10的范围内设置。然而,最好使用1到6之间的PLC值。

此设置会影响测量时间以及电压步长,电压步长是读数之间的电压差。理想情况下,步长应在50mV到100mV之间。电压步长可以使用公式编辑器中的DELTA函数计算。增加PLC延长了测量时间,但会改善噪声读数。

■漏电校准和校准延迟:默认情况下,漏电校准处于禁用状态。如果启用,将在每个电压点测量并校准漏电。漏电校准分三步完成:

1. 使用恒定电流推导C-V正向和反向扫描。

2. 在第一步返回的每个电压点测量正向和反向泄漏电

流。

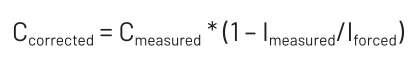

3. 最后,使用测量的校准漏电返回电容值 (CrCorr和CfCorr)。漏电在固定电流范围内测量,并可以实时绘制。漏电校准使用以下校准电容公式:

校准后的反向电容CrCorr与Vr相对绘制,校准后的正向电容CfCorr与Vf相对绘制。如果校准后的电容看起来有噪声,增加施加电流并重复测试。

电流 ( 位移电流 ) 必须高于泄漏电流,否则无法校准泄漏电流。位移电流定义为:I = C*(dV/dt).

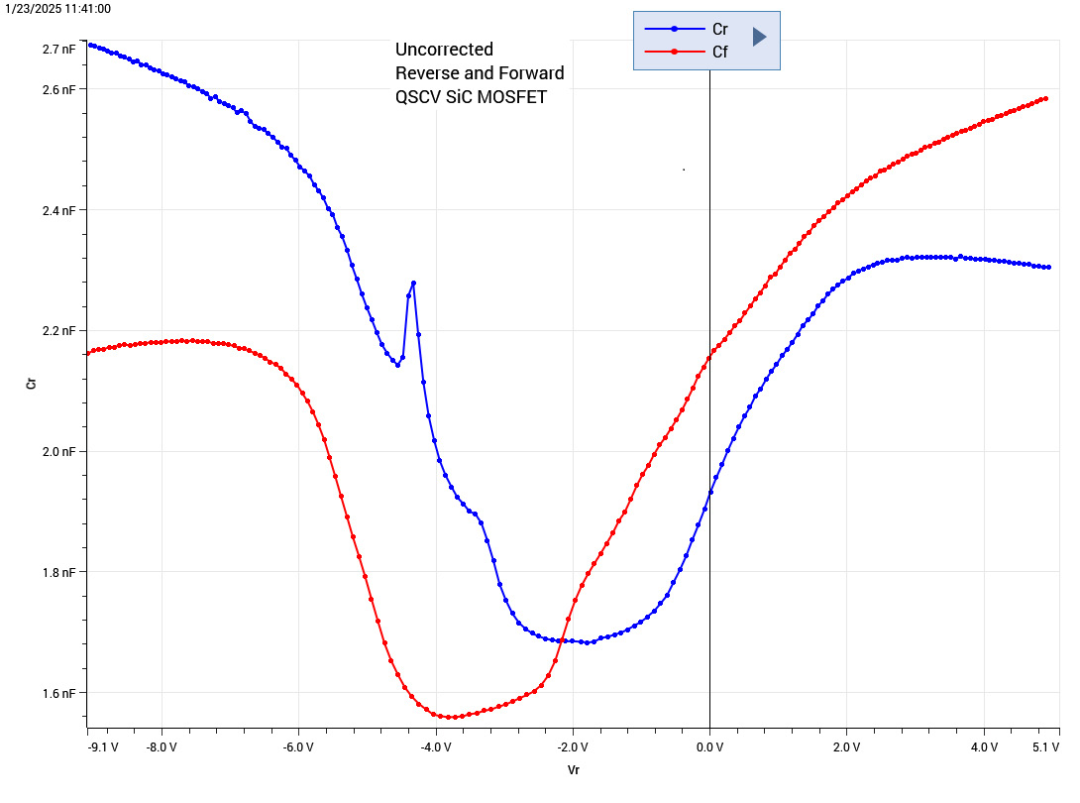

图4和图5显示了有和没有漏电校准的QSCV曲线示例。测试运行了一次,生成了未校准和校准后的数据。图4显示了一个有泄漏的SiC功率MOSFET的正向 (Cf) 和反向 (Cr) C-V曲线。

图4. 漏电碳化硅MOSFET的正向和反向准静态C-V曲线

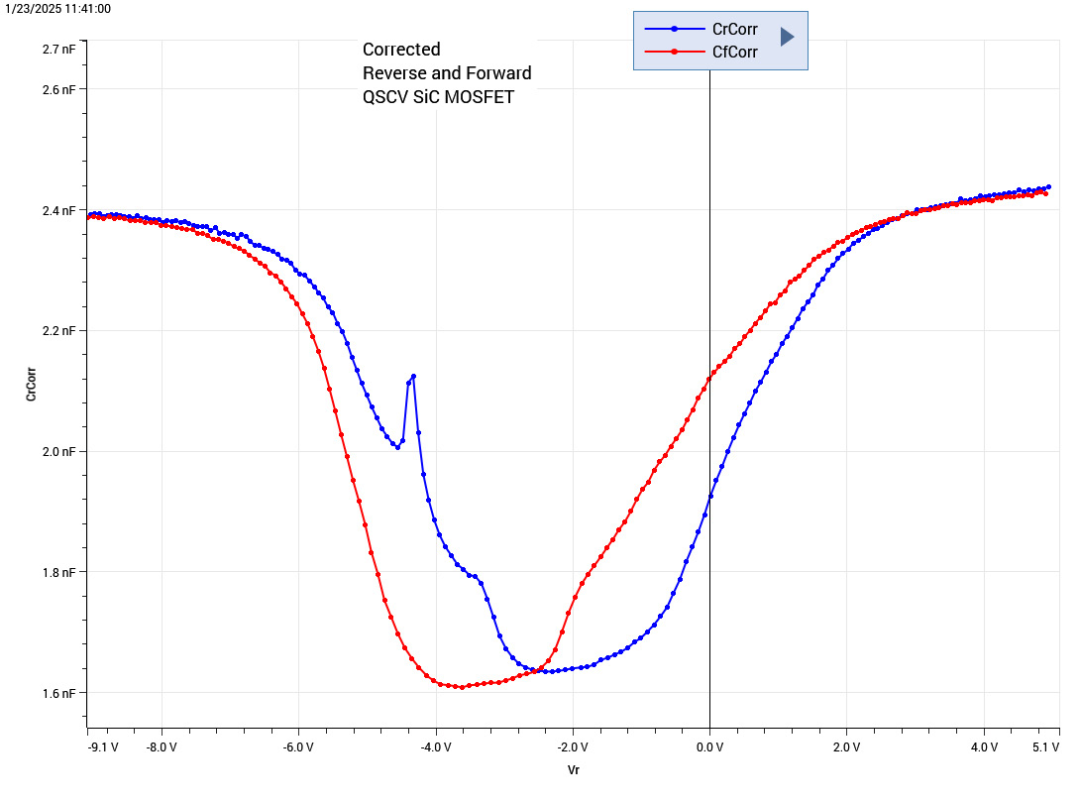

图5显示了有漏电器件的校准后正向(CfCorr)和反向(CrCorr)C-V曲线的结果。

图5. 碳化硅MOSFET的校准前向和反向C-V曲线

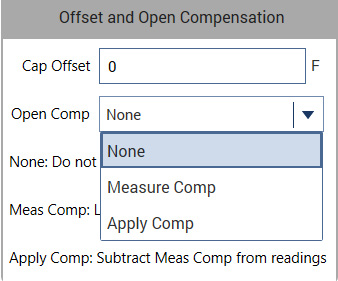

■电容偏移和开路补偿:电容偏移和开路补偿均用于校准测试电路中的电容 ( 如电缆、测试夹具或探头 ) 引起的偏移。这两个选项显示在测试的 “配置” 视图中,如图6所示。

图6. 偏置校准和打开补偿窗口

默认情况下,电容偏移设置为0F,但用户可以输入一个电容值,该值将从正向和反向电容读数中减去。

开路补偿可以设置为“无”、“测量补偿”或“应用补偿”。

如果选择 “无”,则不会将任何开路补偿测量写入文件或应用。

如果启用 “测量补偿”,则在开路情况下(器件从测试夹具中移除或探针抬起)运行测试。至少约有3-5pF的最小电容能被校准,否则会发生错误 (-35),这意味着SMU处于限制状态。通常,开路的施加电流将在1×10-13A或更小范围内,以避免测试进入电压限制状态。由于测试电流非常小,测试将需要几分钟才能执行完成并获取偏移电容。获取的开路数据的平均值存储在文件中,并将在使用 “应用补偿数据” 时从读数中减去。减去的电容值在工作表中显示为Copen。

一旦使用 “测量补偿” 运行测试,将被测器件连接到测试电路中,并再次运行测试,启用 “应用补偿”。确保将施加电流调整到适合器件的水平。当第二次执行测试时,从 “测量补偿” 获取的平均电容 (Copen) 将从后续读数中减去。

分析结果

使用适当的输入设置配置测试后,可以通过选择“运行”来执行测试。运行测试时,将向被测器件施加恒定电流,如步骤1、2和3所述,对器件进行充电并生成反向和正向C-V曲线。

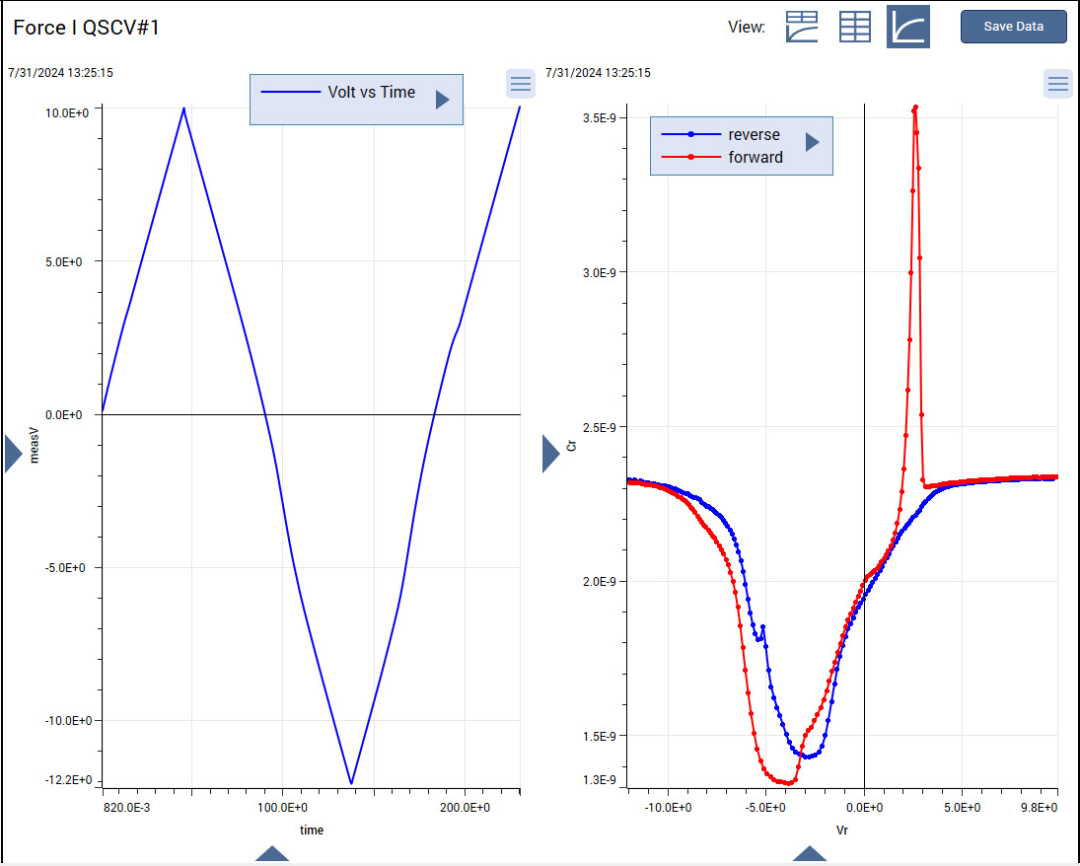

“分析” 视图图形将显示测量结果。电压随时间的测量值将实时显示在左侧图形中,电压测量完成后,正向

和反向C-V扫描将显示在右侧图形中。

数据被拆分为反向和正向C-V扫描,以准确表示测量结果。对于反向扫描,输出反向电压 (Vr)、反向扫描时间(timeR) 和反向电容 (Cr)。在正向扫描中,输出反向电压(Vf)、正向扫描时间 (timeF) 和电容 (Cf)。

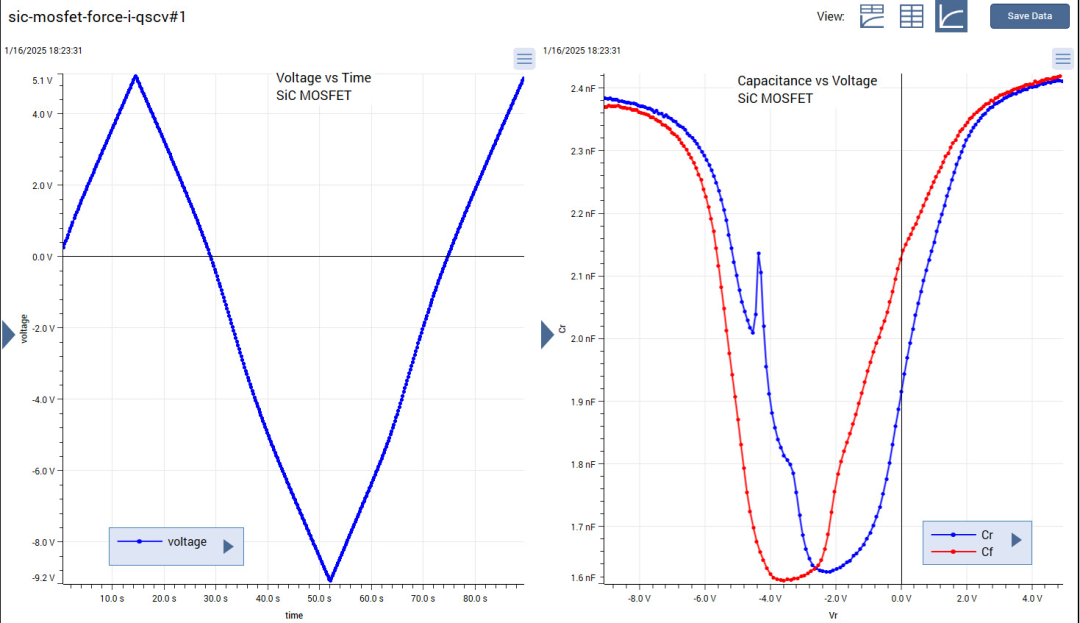

图7显示了使用sic-mosfet-force-i-qscv库测试对市面上可买到的某个SiC功率MOSFET进行测试的 Clarius图形视图结果。对于此测试,使用8×10-10A 的测试电流和4的PLC作为测试设置。使用4的PLC 时,电压步长接近80mV。请注意,在正向和反向扫描中,曲线存在电压偏移和峰值。在曲线右侧的正向扫描和左侧的反向扫描中观察到峰值。这些偏移通常因为内部器件电荷的移动。

图7. 碳化硅MOSFET的电压与时间(左)和反向与正向C-V曲线(右)

图8. SiC MOSFET上的正向和反向准静态C-V扫描。

图8显示了另一个市售SiC MOSFET的准静态C-V曲线。在这种情况下,正向 ( 红色 ) 曲线具有反向扫描中未出现的类似“可动离子” 的峰值。对于此测试,输入参数设置如下:测试电流5×10-10A,8PLC,最大电压10V,最小电压-12V,限压20V。

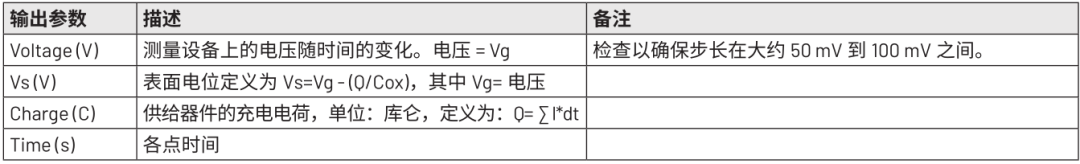

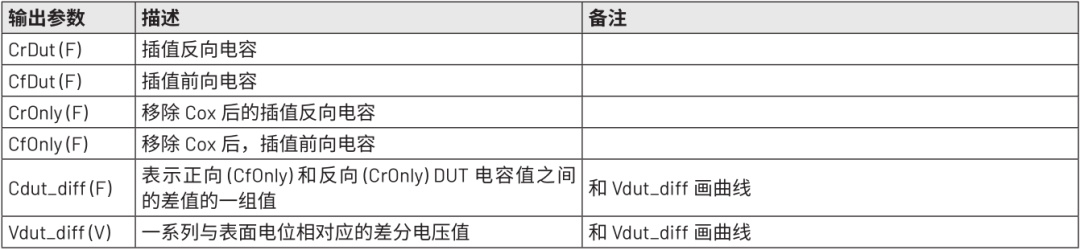

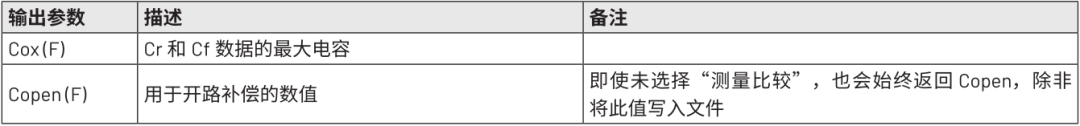

除了在图形工具中查看数据外,多个参数还会返回到分析视图的表格中。以下表格列出了这些输出参数,并按表格中显示的顺序分为以下类别:主要输出参数、反向输出参数、正向输出参数、用于DIT提取的参数和杂项参数。

表2 主要的输出参数

表3 反向输出参数

表4 正向输出参数

表5 DIT提取用到的参数

表6 其他输出参数

优化Force-I QSCV方法

■最小电容:可以测量的最小电容在 10-20pF 之间。此方法推荐电容通常在 nF 范围内的 SiC 器件。

■对器件进行静电屏蔽:由于此方法可测试非常小的电荷,因此对被测器件进行静电屏蔽以避免噪声非常重要。

■电压步长:为获得最佳结果,电压步长应在 50-100mV之间。可以通过更改 PLC 来调整电压步长。电压步长可以用测量的 “电压” 通过公式编辑器中的 DELTA 函数来测量。

■施加电流:选择合适的电流可能需要进行一些试验。电流过低会导致测试时间长。电流过高会导致测试达到限压状态。

■开路补偿:在大多数测量SiC器件QSCV的情况下,开路补偿可能不需要,因为电缆和测试夹具电容(数十皮法)通常比被测器件电容(纳法)小得多。

图10显示了在封装的SiC MOSFET上使用两种方法获取的图形。注意,Force-I QSCV曲线比595数据的噪声更小,但总体而言,曲线相关性很好。

Force-I QSCV与高频C-V的比较

使用Force-I QSCV方法和高频交流测量(使用4215-CVU电容电压单元)获取的C-V曲线进行比较。结果如图11所示。CVU数据(绿色曲线)包含了来自595和Force-I QSCV方法的正向和反向准静态曲线。高频CVU数据在曲线中未显示任何 “峰值”。

图11. 封装的碳化硅MOSFET的高频和准静态C-V扫描

SiC MOS器件上的C-V测量和界面陷阱密度

撰写本文时(2025年3月),我们正在验证使用Force-I QSCV方法对SiC MOSFET和MOS电容进行界面陷阱密度 (DIT) 计算是否与其他已知技术(如结合低频和高频电容测量的比较)相关。以下段落讨论这些推导。

SiC MOSFET

传统上,硅MOS电容的界面陷阱电荷是从低频(准静态)C-Vg曲线和高频 (AC) C-Vg 曲线的电容差中提取的。要观察 SiC MOSFET的内部电荷,可以使用正向和反向准静态C-Vg扫描来提取该电荷。

由于SiC MOSFET比传统硅器件具有更多的内部电荷,因此测量的电容需要相对于表面电势 (Vs) 而不是栅极电压 (Vg) 绘制,以计算陷阱电荷。由于测量了电荷,因此可以计算界面电势。这使得能够将电容表征为界面电势的函数。在标准技术中,提取界面电势很困难,因为在高频下难以或不可能测量氧化物电荷。因此,通常用栅极电压的函数进行,而不是界面电势的函数来进行对比。

推导此界面陷阱电容的技术可以概括为五个步骤:

1. 使用Force-I QSCV方法在SiC MOSFET上生成正向 (Cf) 和反向 (Cr) 准静态电容与栅极电压 (Vg) 曲线。

2. 推导正向和反向扫描的表面电势 (Vs)。

3. 在每个表面电势点对正向电容 (CfDut) 和反向电容 (CrDut) 进行插值。

4. 从正向 (CfDut) 和反向 (CrDut) 测量值中减去氧化物电容(Cox)。

5. 根据正向和反向曲线的差异,作为表面电势的函数,计算由于陷阱电荷引起的电容 (CIT) 和界面陷阱密度 (DIT)。

以下段落将进一步解释这五个步骤:

■ 第1步:生成正向和反向准静态C-V曲线

使用Force-I QSCV方法在SiC MOSFET上生成正向 (Cf)和反向 (Cr) 准静态电容与栅极电压 (Vg) 曲线。

从正向和反向C-V扫描中,两条曲线之间存在电压偏移以及 “峰值” 和较小的曲线特征(见图4和图5)。我们认为电压偏移和 “峰值” 都是内部器件电荷(如陷阱电荷或可动离子电荷)或与器件结构相关的电荷的结果。有趣的是,当生成高频C-V扫描时,不会观察到电压偏移和峰值。

■ 第2步:推导正向和反向扫描的表面电势 (Vs)

MOS器件的正向和反向电压扫描的电容通常在相同的栅极电压 (Vg) 下进行比较。由于SiC MOSFET具有显著的内部电荷,我们改为将正向和反向准静态曲线作为表面电势 (Vs) 的函数进行比较。使用 Vs 校准了正向和反向曲线之间在栅极电压中看到的 “偏移”,并允许对曲线进行比较。精确测量的电荷使我们能够校准栅极氧化物上的电压,以提取Vs。

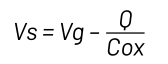

图12显示了SMU向SiC MOS被测器件施加恒定电流以及电压Vg和Vs。器件栅极端子的电压为Vg。SiC/SiO2界面的电压是表面电势 (Vs),由以下公式表示:

Vs = Vg – Vox, 其中 Vox = Q/Cox

图12. 带有电路电势的SIC MOS DUT和SMU连接

首先,分析反向和正向电容阵列 (Cr和Cf),以找到任一阵列的最大值。最大电容定义为Cox,即氧化物电容。

然后,根据每个栅极电压 (Vg),使用氧化物电容 (Cox)和计算出的电荷 (Q) 来计算表面电位Vs:

最后,表面电位被分为两个单独的阵列,用于两次扫描。输出参数VsR表示反向扫描表面电位,VsF表示正向扫描表面电位。

■第3步:在每个表面电位点插值正向电容 (CfDut) 和反向电容 (CrDut)

正向和反向数据集是在不同的栅极电压下收集的,但它们需要在相同的表面电位下进行比较。为此,使用线性插值算法。线性插值过程如下:

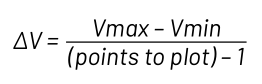

a. 使用以下公式确定电压阶跃点的数量:

b. 对线性插值运行两次,一次用于反向扫描,另一次用于正向扫描,以提取插值电容点。正向和反向插值电容阵列分别为CrDut和CfDut。

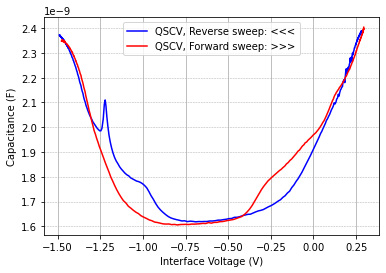

图13显示了正向和反向电容曲线,CfDut和CrDut,以界面电压而不是栅极电压为函数绘制。

图13. 正向和反向电容曲线随Vs的变化

■第4步:从正向 (CfDut) 和反向 (CrDut) 测量值中减去氧化物电容。

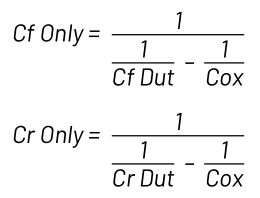

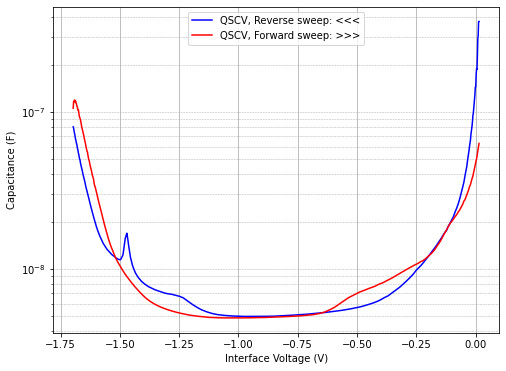

从所有CrDut和CfDut值中减去最大电容(Cox)。为此,使用反向和正向电压表面电位值VsR和VsF运行线性插值算法。计算正向和反向插值电容,在每个函数中,使用以下两个方程在每一点移除Cox值:

在图14中,除去Cox后,只有Cr和只有Cf作为界面电压的函数绘制出来,现在采用对数标度。

图14. 去除Cox后,Vs与Cf和Cr曲线的关系图

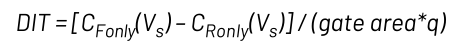

■ 第5步:计算界面陷阱电容(CIT)和密度(DIT)。

根据表面电位,计算由校正后的正向和反向曲线差异引起的陷阱电荷电容(CIT)。

界面陷阱密度 (DIT) 也通过以下公式推导:

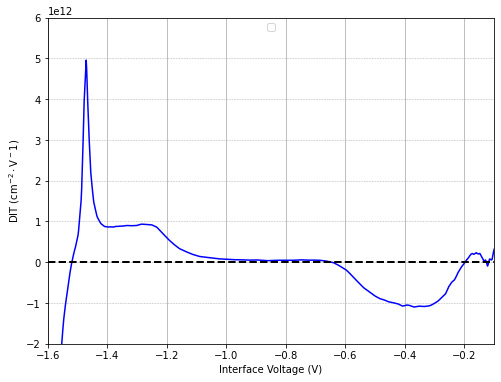

图15显示了界面陷阱密度 (DIT) 随表面电位 (Vs) 的变化曲线图

图15 显示了界面陷阱密度 (DIT) 随表面电位 (Vs) 的变化曲线图

碳化硅MOScap

在MOScap上进行界面陷阱密度 (DIT) 测量时,会结合使用高频和低频测量。生成高频和准静态C-V曲线时,请确保电压步长远小于两条曲线之间的电压差。通过减小PLC值可以减小电压步长。

我们仍在研究使用Force-I QSCV技术提取碳化硅MOScap和MOSFET的DIT。

结论

Force-I QSCV技术能够在碳化硅MOS设备上实现准静态C-V测量。该方法通过正向和反向扫描获取两组数据,以及通过施加正负电流获得的电压――时间数据。已知总电荷后,此方法可以提取半导体界面处的电容和电荷。正向和反向扫描的差分分析能够直接提取界面陷阱密度 (DIT)。

-

放大器

+关注

关注

145文章

14162浏览量

218355 -

MOSFET

+关注

关注

150文章

8791浏览量

222189 -

半导体

+关注

关注

335文章

29221浏览量

243360 -

SiC

+关注

关注

32文章

3273浏览量

66023

原文标题:Force-I QSCV 技术:助力 SiC MOSFET 界面陷阱密度精准表征的新方法

文章出处:【微信号:泰克科技,微信公众号:泰克科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

麦科信光隔离探头在碳化硅(SiC)MOSFET动态测试中的应用

SiC-MOSFET的应用实例

SiC-MOSFET与Si-MOSFET的区别

SiC-MOSFET的可靠性

沟槽结构SiC-MOSFET与实际产品

SiC-MOSFET有什么优点

SiC功率器件SiC-MOSFET的特点

浅析SiC-MOSFET

测量SiC MOSFET栅-源电压时的注意事项

SiC-MOSFET器件结构和特征

SiC MOSFET的器件演变与技术优势

如何有效地测量SiC MOSFET

Force-I QSCV技术在SiC MOSFET界面陷阱测量中的应用

Force-I QSCV技术在SiC MOSFET界面陷阱测量中的应用

评论