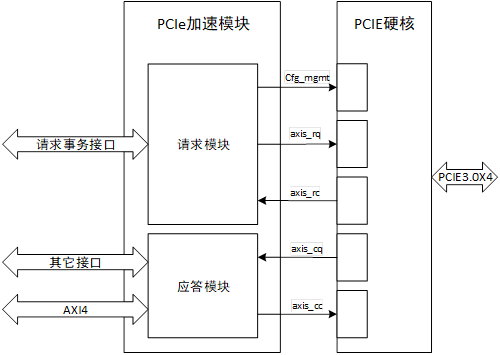

PCIe加速模块负责实现PCIe传输层任务的处理,同时与NVMe层进行任务交互。如图1所示,PCIe加速模块按照请求发起方分为请求模块和应答模块。请求模块负责将内部请求事务转化为配置管理接口信号或axis请求方请求接口信号(axis_rq),以及解析axis请求方完成接口信号(axis_rc);应答模块负责接收axis完成方请求接口信号(axis_cq),将请求内容转化为AXI4接口信号或其它内部信号做进一步处理,如果需要应答,将应答事务通过axis完成方完成接口(axis_cc)发送给PCIE硬核。

图1 PCIe加速模块系统框图

PCIe加速模块在系统中作为NVMe层到PCIe数据链路层的桥接,不仅承担了TLP与其它接口信号的转换功能,也是降低传输延时、增加吞吐量的核心部件。接下来分别对请求模块和应答模块的结构设计进行分析与叙述。

-

模块

+关注

关注

7文章

2796浏览量

50962 -

PCIe

+关注

关注

16文章

1365浏览量

85758 -

接口信号

+关注

关注

0文章

10浏览量

9115 -

nvme

+关注

关注

0文章

271浏览量

23329

发布评论请先 登录

NVMe高速传输之摆脱XDMA设计20: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计18:PCIe请求模块设计(上)

NVMe高速传输之摆脱XDMA设计14: PCIe应答模块设计

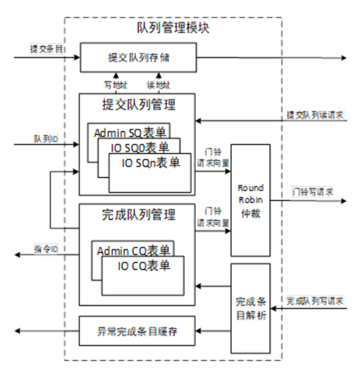

NVMe IP高速传输却不依赖XDMA设计之九:队列管理模块(上)

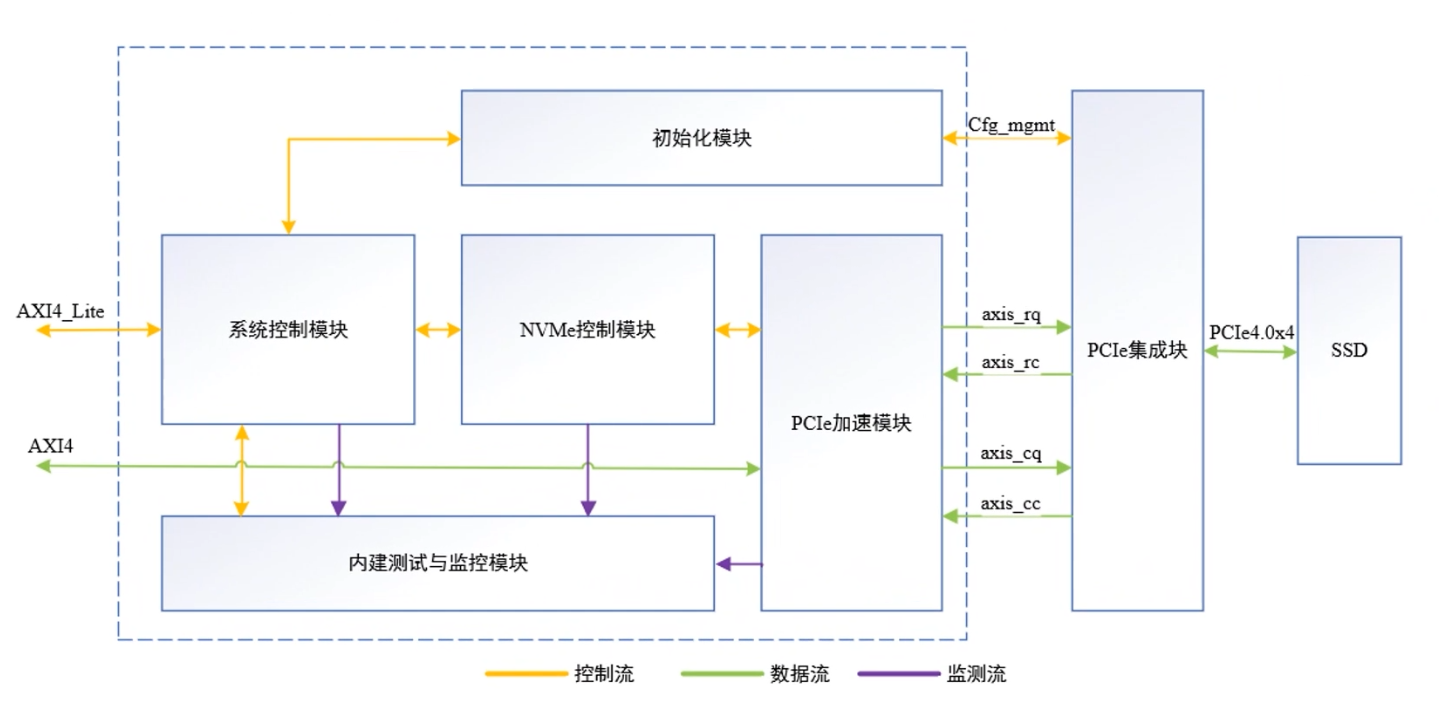

NVMe高速传输之摆脱XDMA设计17:PCIe加速模块设计

NVMe高速传输之摆脱XDMA设计17:PCIe加速模块设计

评论