文章来源:学习那些事

原文作者:小陈婆婆

本文介绍了三维集成电路设计中TSV(硅通孔)技术的设计优化。

在三维集成电路设计中,TSV(硅通孔)技术通过垂直互连显著提升了系统集成密度与性能,但其物理尺寸效应与寄生参数对互连特性的影响已成为设计优化的核心挑战,本文分述如下:

RLC延时模型

信号反射

多目标协同优化算法

RLC延时模型

在寄生效应分析方面,TSV的RC特性对互连延时与功耗的影响尤为关键。三维集成技术通过压缩全局互连线长,使最大互连延时较二维系统降低40%~50%,但TSV RC效应在中小规模电路中逐渐凸显。当门电路规模降至1mm?时,包含TSV的三维系统延时达0.45ns,接近二维系统的0.5ns。

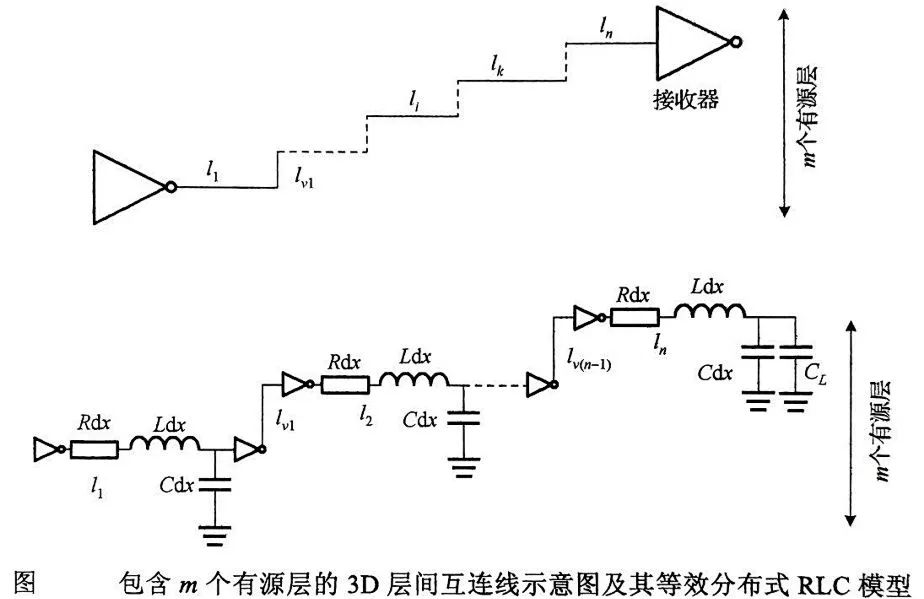

为应对高频信号下的电感效应,提出了分布式RLC互连延时模型,将互连线等效为均匀的RLC传输线。该模型表明,随着系统时钟频率增大与信号上升时间缩短,互连电感效应成为不可忽视的因素,尤其在采用宽厚金属线的全局信号线和时钟线中,电感导致的延时增大、电压过冲和感性串扰问题更为显著。

通过合理布局TSV并优化各层互连线段长,可有效降低全局互连延时。近期研究突破包括“智能TSV屏蔽”技术,通过动态关闭空闲TSV,将中小规模电路的TSV功耗降低30%;“分布式缓冲器-TSV协同设计”方法,使缓冲器数目减少25%的同时保持延时性能不变。此外,TSV热-电耦合分析模块,可实时预测不同布局方案下的功耗-延时乘积,设计效率提升40%。

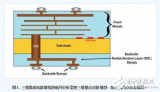

在材料与工艺创新方面,玻璃通孔(GTV)技术,通过低介电常数玻璃基板替代传统硅基,将TSV寄生电容降低40%,为高频应用开辟了新路径;石墨烯包覆TSV结构,成功将TSV电阻降低至铜互连的1/10,显著缓解了TSV RC效应。这些进展表明,精确量化TSV效应并开发跨层优化技术,已成为释放三维集成潜力的关键。

信号反射

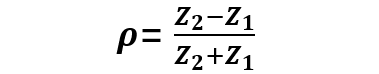

在三维集成电路设计中,信号完整性已成为制约高速互连性能的核心挑战,其中反射效应因TSV阻抗突变而尤为显著。当信号沿分布式RLC传输线传播时,瞬态阻抗的变化会导致部分信号反射,引发振铃、过冲等失真问题,这一问题在大规模集成系统中因信号上升时间缩短而进一步加剧。反射系数ρ作为衡量阻抗不连续性的关键指标,定义为反射电压与入射电压的比值,其表达式为:

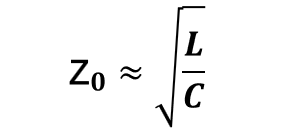

式中,Z?与Z?分别为信号传播路径中相邻区域的特征阻抗。在高频条件下,互连电阻R与电导G的影响可忽略,特征阻抗可简化为:

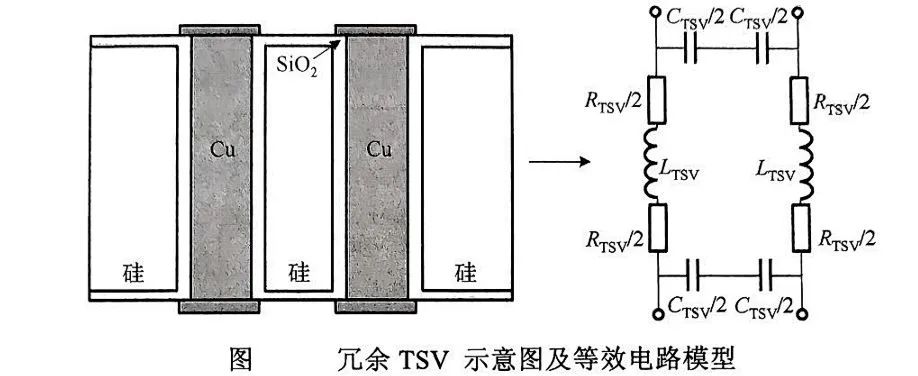

其中,L与C为互连线单位长度的分布电感与电容。对于垂直TSV而言,其等效电感LTSV与电容CTSV与物理尺寸(半径rTSV、高度hTSV)强相关,因此优化TSV几何参数成为减小反射系数的直接手段。

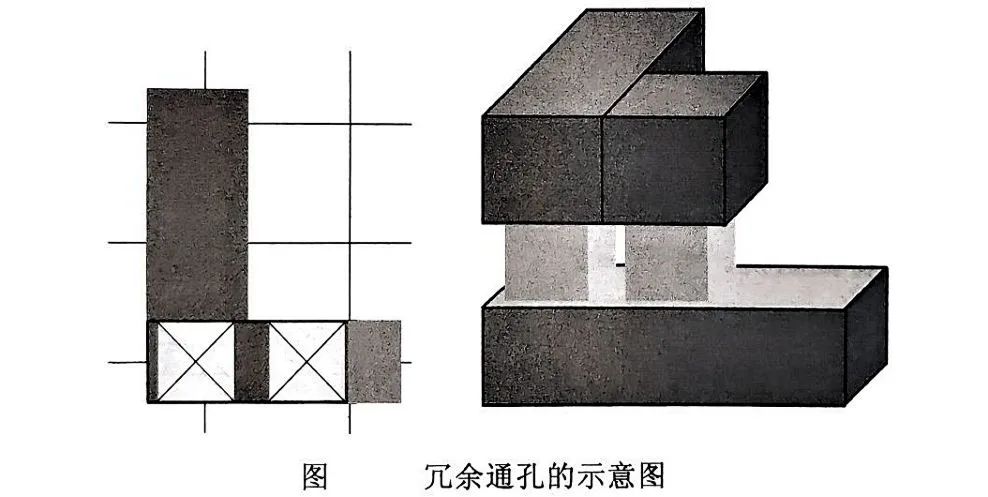

然而,实际工艺中TSV尺寸受设计规则严格限制,冗余通孔技术通过并行插入多个通孔,在提升制造良率的同时,等效调整了TSV的电学特性,实现与单个大尺寸TSV相近的阻抗匹配效果。

近期行业进展为信号完整性优化提供了新思路。例如,3nm 3D IC工艺中引入“自适应阻抗匹配”技术,通过动态调节缓冲器输出阻抗,使Z?与Z?实时匹配,将反射系数降低至0.1以下;“分布式TSV阵列”设计,利用多个小尺寸TSV并行连接,在保持垂直互连密度的同时,将特征阻抗波动控制在5%以内。此外,TSV反射分析模块,可精准预测不同布局方案下的信号失真程度,设计周期缩短40%。在材料创新方面,碳纳米管(CNT)TSV技术,通过低电阻率材料将TSV等效电感降低30%,显著缓解了阻抗突变问题。

这些技术突破表明,精确量化TSV电学特性并开发跨层优化技术,已成为保障3D IC信号完整性的关键。未来,随着晶圆级异构集成技术的演进,TSV尺寸效应与寄生效应的协同优化将持续深化,为高频、高速三维集成系统提供性能保障。

多目标协同优化算法

在三维集成电路设计中,信号传输延迟与反射畸变控制是互连优化领域的核心挑战。基于传输线理论分析可知,三维互连系统的时延特性不仅与分段连线长度及硅通孔(TSV)物理尺寸相关,更受到信号反射系数的显著影响。为同时实现低时延、高传输速率与长距离信号完整性,需建立多目标协同优化框架,对TSV插入位置、冗余通孔数目及分段线长进行联合设计。

具体而言,硅通孔高度受限于衬底减薄工艺水平,在特定技术节点下可视为定值,因此优化问题可转化为最小化互连总时延与反射系数的组合目标。

算法执行流程遵循闭环优化策略:首先初始化冗余通孔配置,基于传输线模型计算初始反射系数;继而通过布局优化算法确定最佳分段线长及对应时延;再通过尺寸优化调整冗余通孔数目,获得改进后的反射系数与次优时延;若次优时延未达收敛阈值,则循环执行布局-尺寸优化步骤,直至获得全局最优解,同步确定最佳分段线长配置及冗余通孔分布。

值得关注的是,随着先进封装技术向5nm及以下节点演进,多物理场耦合效应对TSV优化的影响日益显著。近期研究显示,基于机器学习的代理模型可有效提升多目标优化效率,例如采用深度强化学习实现时延与反射的快速权衡。此外,2024年IEEE国际固态电路会议(ISSCC)报道的混合键合技术,通过亚微米级对准精度显著降低了TSV间距需求,为三维互连优化提供了新的设计自由度。这些技术进展表明,多目标协同优化算法正朝着与工艺技术深度融合的方向发展,未来将更注重设计-制造协同(DTCO)框架的构建。

-

集成电路

+关注

关注

5433文章

12197浏览量

369523 -

TSV

+关注

关注

4文章

132浏览量

82050 -

硅通孔

+关注

关注

2文章

27浏览量

12015

原文标题:?三维集成电路的TSV布局设计

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

世界级专家为你解读:晶圆级三维系统集成技术

有偿,用matlab仿真三维电路互连线尺寸调整对延时功耗带宽影响

三维集成电路系统的电网分析

三维集成电路(IC)设计中的温度控制

Integrity 3D-IC早期三维布图综合功能

10.9.6 三维集成电路测试∈《集成电路产业全书》

10.5.2 基于TSV的三维集成电路∈《集成电路产业全书》

?三维集成电路的TSV布局设计

?三维集成电路的TSV布局设计

评论