博客作者:Dario Fresu

欢迎来到 “掌握 PCB 设计中的 EMI 控制” 系列的第六篇文章。本文将探讨串扰如何影响信号完整性和 EMI,并讨论在设计中解决这一问题的具体措施。

图 1:Altium Designer 中的 PCB 设计示例

串扰是现代印刷电路板(PCB)设计中最常见的问题之一。随着 PCB 密度不断增加,这一现象愈发普遍。在越来越小的板载区域集成更多高速接口的趋势加剧了这一挑战 —— 紧凑的布局导致走线间距缩小,显著增加串扰风险。

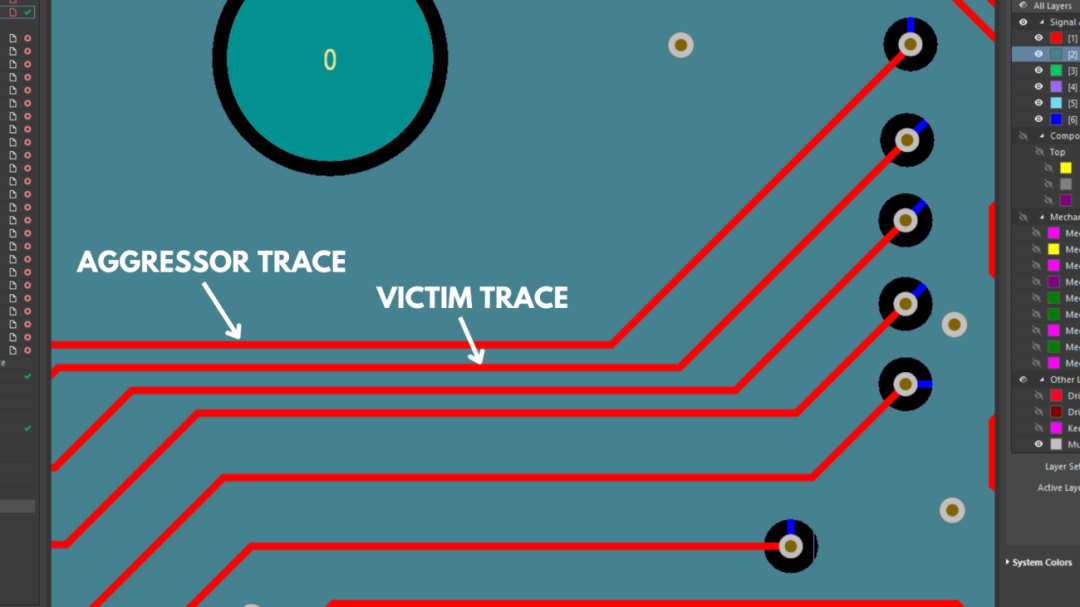

本质上,信号串扰是指电信号从一个网络(或走线)无意耦合到另一个网络的现象。当一条走线上传输的信号产生的电磁场与相邻走线相互作用时,串扰即会发生。其中,携带原始信号的走线称为 “干扰线”,接收干扰信号的走线称为 “受害线”。

图 2:电路中串扰的表现示例

在电磁干扰(EMI)领域,串扰的影响尤为关键 —— 它不仅可能成为系统内部干扰的源头,还可能成为干扰其他设备的电磁辐射源。需要注意的是,串扰不仅发生在传输信号电流的信号走线之间,也会出现在返回参考导体(返回电流流回源端的路径)中,例如 “地弹” 现象,即是返回参考导体中发生的串扰。

理解串扰及其影响

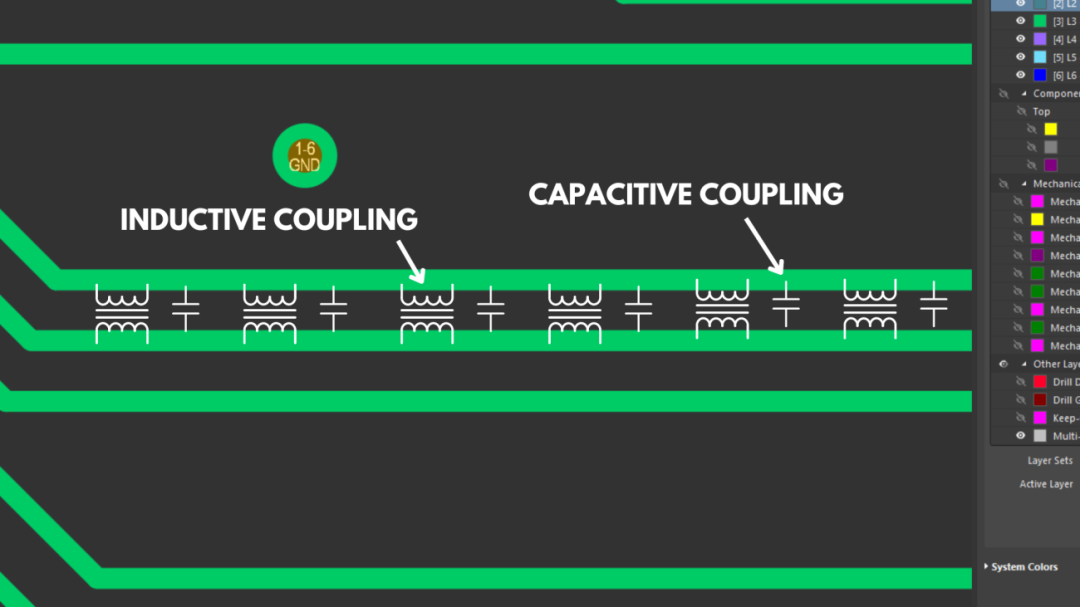

串扰现象主要由导体间的容性耦合和感性耦合引起。当两条或多条走线排布过近,且信号电压和电流随时间变化时,干扰线边缘的边缘场(电场和磁场)会耦合到附近的受害线,导致受害线上产生不必要的噪声。

PCB 设计师在减少串扰和有效抑制 EMI 方面的核心任务,是最小化这些边缘场对其他导体的影响,避免噪声从一条走线传播到另一条走线。

图3:信号走线间的感性耦合与容性耦合示例

从 EMI 角度看,当噪声通过 PCB 走线、连接走线的导线或导体产生辐射时,串扰就会成为问题。

串扰的类型

处理串扰问题时,区分两种类型尤为重要:近端串扰(NEXT)和远端串扰(FEXT)。

近端串扰(NEXT):发生在信号传输端同一侧的串扰,即干扰信号在电路的发送端耦合到相邻导体。

远端串扰(FEXT):发生在信号传输端对侧的串扰,即干扰信号在电路的接收端耦合到相邻导体。两者的核心区别在于:NEXT 出现在源端附近,沿信号传播反方向(反向)耦合;FEXT 出现在目的端附近,沿信号传播方向(正向)耦合。

Altium Designer 中的实用布局策略

尽管信号串扰的复杂性足以独立成篇,但仍有多种方法可降低其影响,且大部分技术依赖 PCB 布局设计 —— 几何结构设计至关重要。以下是减少串扰最有效的布局策略:

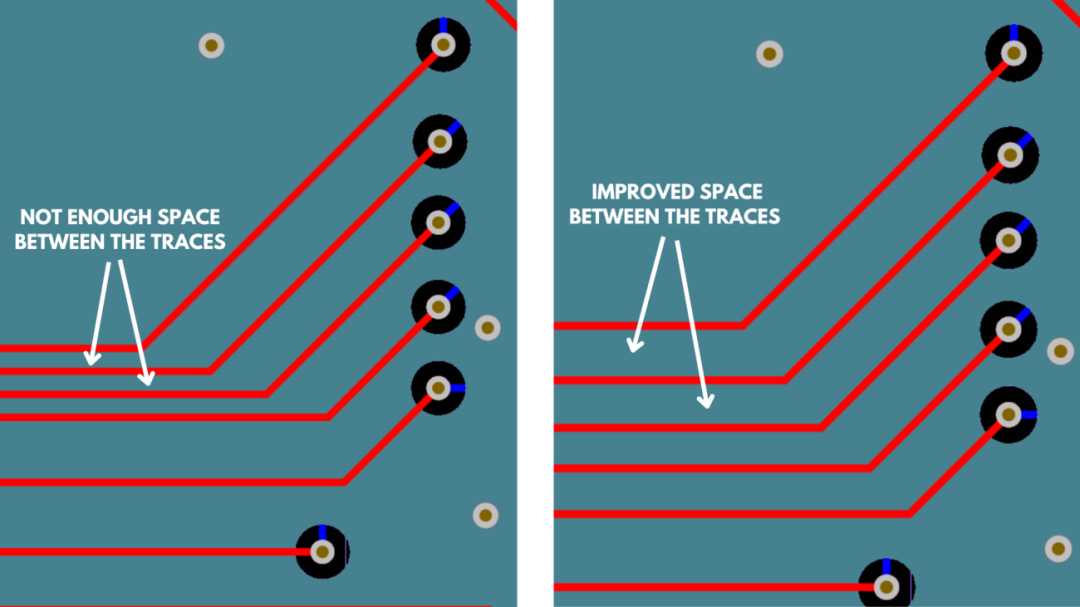

增大导体间距:增加走线间距离,使电场和磁场无法相互耦合。

图 4:信号走线间距优化前后示例

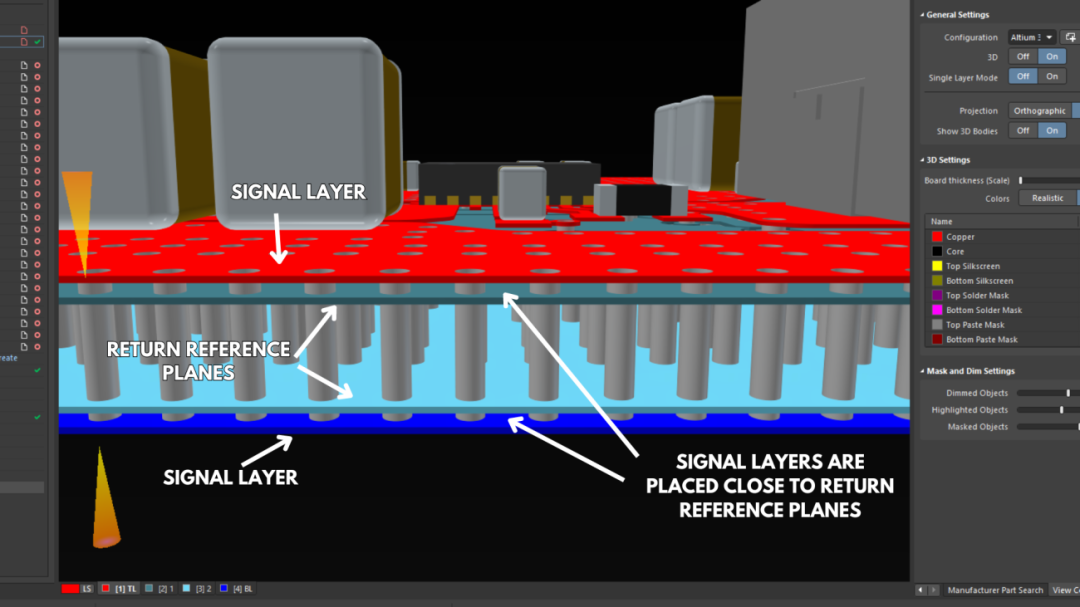

我们可以采用的另一种技术是缩小信号走线与返回参考平面之间的间距。这将使信号场与其返回参考平面紧密耦合,减少这些场向其他导体的扩散。

此外,缩短信号导体和返回参考导体这两者的长度,将减少不同网络之间的耦合量。这也很直观,因为导体暴露得越少,噪声耦合到其他导体的可能性就越小。

图 5:Altium Designer 中信号与返回参考平面紧密耦合的 3D 视图

另一种减少串扰的常用方法是为不同信号的返回路径提供多个导体,这一方法可有效应用于 IC、连接器和 PCB 走线。

例如,这意味着在使用带状电缆或其他连接器时,为不同信号网络设置独立的返回路径,而非多个信号网络共用单一返回导体。

Altium Designer 中的仿真策略

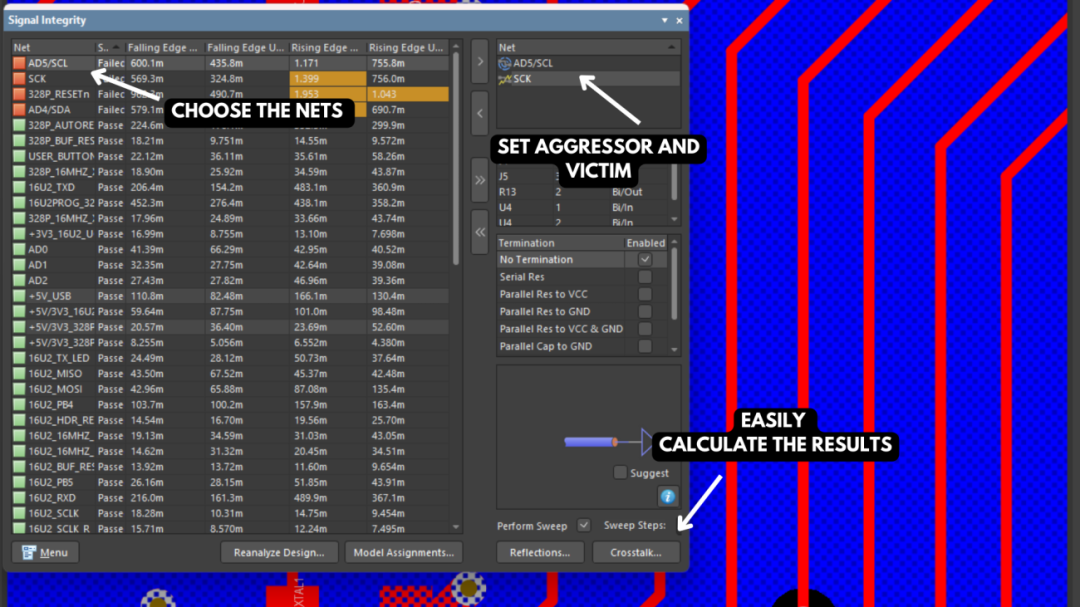

相较于凭经验猜测电路布局中的串扰情况,使用先进工具进行精确计算更为重要。

Altium Designer 内置的信号完整性(Signal Integrity)工具是实现这一目标的强大功能,可对 PCB 走线上的串扰进行仿真和分析,精确预测串扰水平并深入理解其影响。通过该工具,可更精准地优化设计。

图 6:使用 Altium Designer 进行串扰仿真的示例

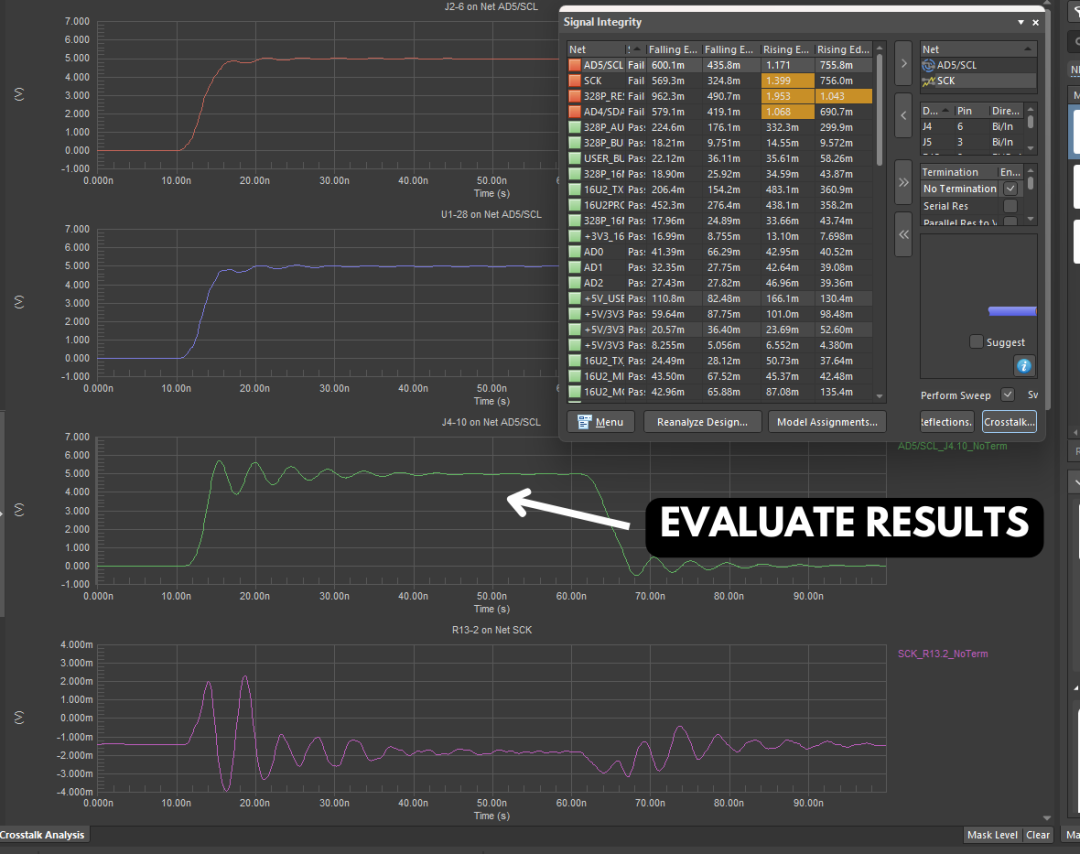

信号完整性工具提供详细仿真结果,帮助评估各种设计权衡 —— 理解这些权衡是最小化干扰并实现高性能的关键。该工具提供的洞见远比单纯猜测可靠。

图 7:Altium Designer 中使用信号完整性工具进行串扰评估的示例

借助这一先进工具,可在性能需求与布局约束之间做出明智决策,提升电路可靠性和功能性,改善信号完整性和 EMI 性能,同时提高整体设计效率。

总结

综上所述,若要有效减少信号串扰并提升 PCB 的 EMI 性能,可采用多种策略。Altium Designer 内置的信号完整性工具对于精确预测和抑制 PCB 布局中的串扰不可或缺 —— 它使我们能够基于数据做出决策,确保设计满足规格要求并在各种条件下可靠运行。

如果您希望提升 PCB 设计项目水平,并充分利用可显著简化和优化设计流程的先进工具,我们强烈建议您开启Altium Designer 和 Altium 365 的免费试用。

这些前沿工具提供一系列强大功能,旨在提升设计工作流程的效率和效能,助您更轻松地在 PCB 项目中实现高质量成果。

关于Altium

Altium有限公司隶属于瑞萨集团,总部位于美国加利福尼亚州圣迭戈,是一家致力于加速电子创新的全球软件公司。Altium提供数字解决方案,以最大限度提高电子设计的生产力,连接整个设计过程中的所有利益相关者,提供对元器件资源和信息的无缝访问,并管理整个电子产品生命周期。Altium生态系统加速了各行业及各规模企业的电子产品实现进程。

-

emi

+关注

关注

53文章

3809浏览量

132024 -

altium

+关注

关注

48文章

988浏览量

120726 -

PCB设计

+关注

关注

396文章

4841浏览量

91431 -

串扰

+关注

关注

4文章

190浏览量

27531

原文标题:【技术博客】掌握 PCB 设计中的 EMI 控制之抑制串扰以优化 EMI

文章出处:【微信号:AltiumChina,微信公众号:Altium】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

常见信号完整性的问题之PCB设计串扰的原因与Altium Designer中的串扰消除技术

高频晶振的信号完整性挑战:如何抑制EMI与串扰

串扰如何影响信号完整性和EMI

串扰如何影响信号完整性和EMI

评论