文章来源:学习那些事

原文作者:小陈婆婆

本文介绍了电力电子器件在功率混合电路小型化需求下的封装技术。

电力电子器件作为现代能源转换与功率控制的核心载体,正经历着从传统硅基器件向SiC等宽禁带半导体器件的迭代升级,功率二极管、IGBT、MOSFET等器件的集成化与高性能化发展,推动着封装技术向高密度集成、高可靠性与高效散热方向突破。

在功率混合电路小型化需求驱动下,封装工艺已成为决定器件功率密度、热稳定性及寿命的关键技术瓶颈,其创新突破直接支撑着新能源、轨道交通等领域的能效提升与系统革新,本文分述如下:

商用功率封装

功率封装设计原则

商用功率封装

商用功率封装作为功率器件与系统级应用的关键接口,其技术演进始终围绕着功率密度提升、热管理优化及可靠性增强三大核心维度展开。

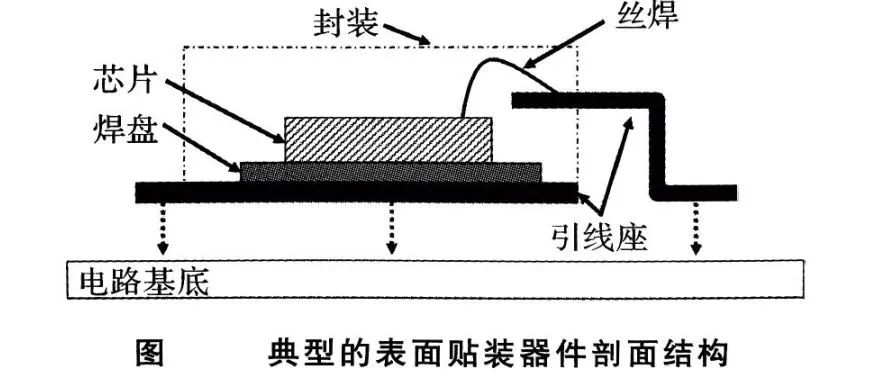

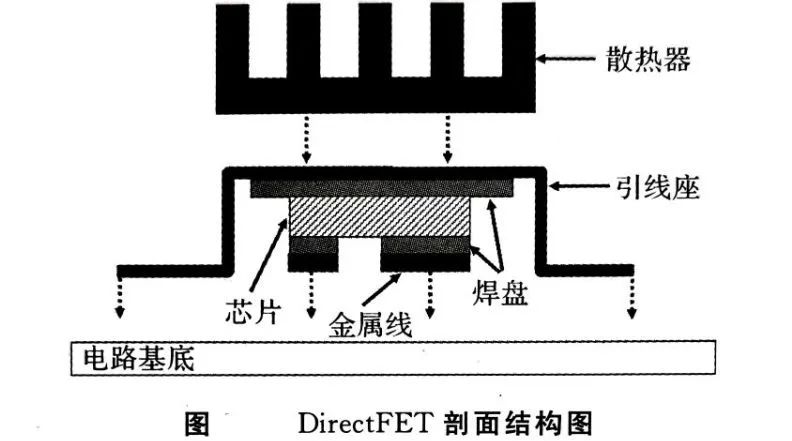

在分立器件封装领域,工业界已形成覆盖小功率到高功率的完整解决方案体系,封装选型需综合考量芯片尺寸、热耗散需求及终端应用场景特性。传统通孔插装技术凭借其直接散热片安装能力,在高压大电流场景中仍占据重要地位,TO-220与TO-247等封装通过优化引脚布局与散热面积配比,实现了封装体积与功率密度的有效平衡;而表面贴装技术则通过载体金属化工艺创新,如采用铜基底或DBC衬底,显著提升了热传导效率,DirectFET等倒装焊技术更通过消除键合线实现全接触面散热,为紧凑型系统设计提供了可能。

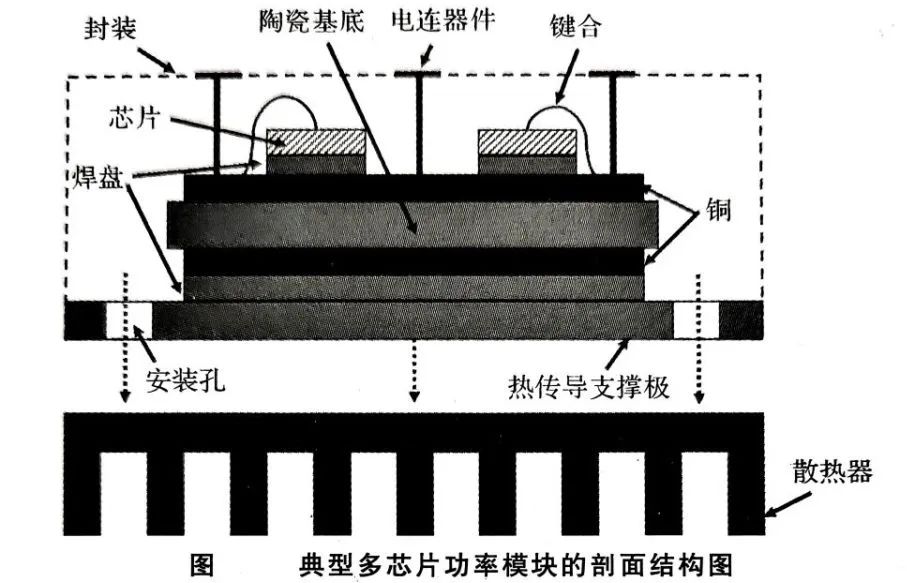

当前分立器件封装正朝着高集成度与高热性能方向突破,第三代半导体器件的普及推动封装材料向更高热导率方向发展,氮化铝(AlN)与碳化硅(SiC)基复合衬底的应用显著降低了热阻。多芯片功率模块作为集成化封装的典型代表,通过DBC陶瓷衬底与金属基复合材料(MMC)散热器的协同设计,构建了从芯片到系统的立体热传导通道,其中DBC的双面金属化工艺不仅提升了电气互连密度,更通过陶瓷层与金属层的热应力匹配设计,有效延长了模块工作寿命。

值得关注的是,近期行业在模块封装领域取得两项重要进展:一是采用纳米银烧结技术的芯片互连工艺,大幅提升了高温工作可靠性;二是石墨烯增强型MMC材料的研发,其热导率突破400W/(m·K)的同时,实现了与SiC器件CTE的完美匹配,为千瓦级功率模块的小型化提供了材料支撑。这些技术创新正推动着电力电子系统向更高效率、更小体积的下一代产品演进。

功率封装设计原则

功率封装设计作为电力电子系统开发的核心环节,其技术决策需贯穿从器件选型到工艺实现的完整价值链。在系统设计层面,半导体器件的遴选需构建多维评估矩阵:工作电压/电流参数决定器件的耐压与通流能力,开关频率与损耗特性直接影响系统能效,而热负载分布则与封装热路设计形成强耦合关系。当前行业趋势显示,基于氮化镓(GaN)与碳化硅(SiC)的宽禁带器件正推动设计范式转变,其超高频工作特性要求封装寄生参数需控制在纳秒级响应范围内,促使传统二维布局向三维立体封装演进。

在基底材料选择上,热导率与热膨胀系数(CTE)的匹配成为关键矛盾点。氮化铝(AlN)基底凭借300W/(m·K)以上的热导率,在高压模块中逐步取代氧化铝(Al?O?),而金刚石增强型复合基板的出现更将热导率推高至500W/(m·K)量级。值得注意的是,纳米陶瓷基板通过晶界重构技术,在保持AlN高导热特性的同时,将CTE误差控制在±1ppm/℃以内,显著提升了高温工作可靠性。

散热结构创新方面,金属基复合材料(MMC)与相变散热技术形成组合优势。石墨烯-铜复合散热器其热导率较纯铜提升300%,同时通过微观孔隙结构实现热应力缓冲,有效解决硅与金属间的CTE失配问题。在焊接工艺领域,纳米银烧结技术正取代传统锡焊,其250℃以上的工作温度与高可靠性的金属间化合物(IMC)形成机制,为SiC器件的高温封装提供了解决方案。

键合技术同样呈现突破性进展,铜线键合工艺在直径50μm线径下即可实现10A级电流承载,较传统金线方案提升3倍载流能力。镀钯铜线通过表面钝化处理将键合失效率降低至0.1ppm以下。值得关注的是,3D封装技术开始渗透功率领域,PowerStack技术通过垂直互连实现多层功率器件堆叠,在10mm?体积内集成完整桥式电路,功率密度突破500W/cm?,为电动汽车逆变器的小型化开辟了新路径。

当前行业正加速探索人工智能辅助设计(AID)在封装优化中的应用,基于有限元分析(FEA)与机器学习的协同仿真平台,可自动生成热-机械-电气多物理场耦合的最优解,将设计周期从传统数周缩短至72小时以内。这种技术范式转变,正推动功率封装从经验驱动向数据驱动的跨越式发展。

射频芯片封装

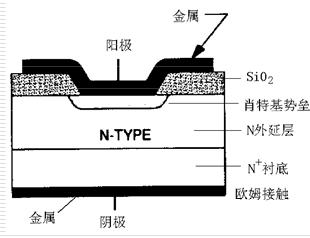

射频芯片封装作为无线通信系统的核心技术支点,其设计哲学与功率器件存在本质差异,核心挑战源于高频信号对材料特性与寄生参数的极端敏感度。在半导体材料选择上,III-V族化合物(GaAs、InP、GaN)凭借半绝缘衬底特性与超高频载流子迁移率,成为毫米波器件的主流载体,其能带结构可支撑MESFET、HEMT等异质结器件在Ka波段以上实现亚纳秒级响应速度。值得注意的是,8英寸GaN-on-SiC晶圆通过缓冲层优化将晶格失配度降低至0.1%,使X波段功率密度突破10W/mm,为5G基站射频前端的小型化提供了材料级解决方案。

在互连架构层面,射频芯片突破传统导线键合模式,转向微带线、共面波导等平面传输结构。这些基于薄膜金属(Ti/Au/Pt)的传输线,其特征阻抗需精确控制在50Ω±5%范围内,对基板介电常数与损耗角正切(tanδ)提出严苛要求。传统FR-4基板因tanδ在10GHz以上骤增至0.02,已难以满足毫米波应用需求,促使行业转向低温共烧陶瓷(LTCC)与高电阻率硅(HRS)基板。LTCC-SiC复合基板通过将碳化硅的高热导率(490W/m·K)与LTCC的低损耗特性结合,在W波段实现tanδ<0.001的同时,将热阻降低至2℃/W,有效解决了高频器件的"热-电"协同优化难题。

封装损耗控制作为射频设计的核心命题,涉及电介质损耗与导体损耗的双重博弈。在电介质层面,氧化铝(Al?O?)基板虽在X波段表现稳定,但进入毫米波频段后,其表面粗糙度引发的散射损耗成为主要瓶颈。RT/duroid 5880基板通过微晶玻璃填充技术将表面粗糙度降至0.5μm以下,使Ka波段插入损耗降低30%。在导体损耗方面,集肤效应导致的电流分布不均问题尤为突出,传统钛/铬粘附层在高频下可能成为电流瓶颈。梯度金属化工艺通过原子层沉积(ALD)技术实现粘附层-导电层-抗腐蚀层的纳米级渐变过渡,使30GHz下的导体损耗降低至0.05dB/cm。

当前行业正加速探索异质集成封装技术,将射频前端模块(RFEM)集成至单一封装体内。

-

半导体

+关注

关注

335文章

29219浏览量

243342 -

芯片封装

+关注

关注

12文章

585浏览量

31632 -

射频芯片

+关注

关注

989文章

448浏览量

81323

原文标题:电力电子芯片封装技术及射频芯片封装

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

详解电力电子器件的芯片封装技术

详解电力电子器件的芯片封装技术

评论