在高速光通信系统中,LVPECL(低压正射极耦合逻辑)、PECL(正射极耦合逻辑)与 LVDS(低压差分信号)是常用的高速接口电平标准。LVPECL/PECL 以高速度、低噪声特性广泛应用于光模块等高速器件,而 LVDS 凭借低功耗、高集成度优势在协议转换 IC 等中端设备中普及。两者的互连设计直接影响信号完整性与系统可靠性,本文从直流耦合、交流耦合两个维度展开技术解析。

一、LVPECL 与 LVDS 的互连设计

1.1 直流耦合:直接电平转换与阻抗匹配

直流耦合通过电阻网络实现电平直接转换,无需隔直电容,适用于对延迟敏感的高速场景。设计核心是同时满足阻抗匹配(减少反射)、电平兼容(信号落在接收端有效范围)与功耗平衡(避免过流)。

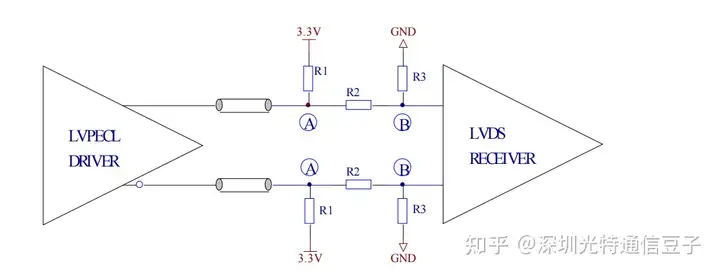

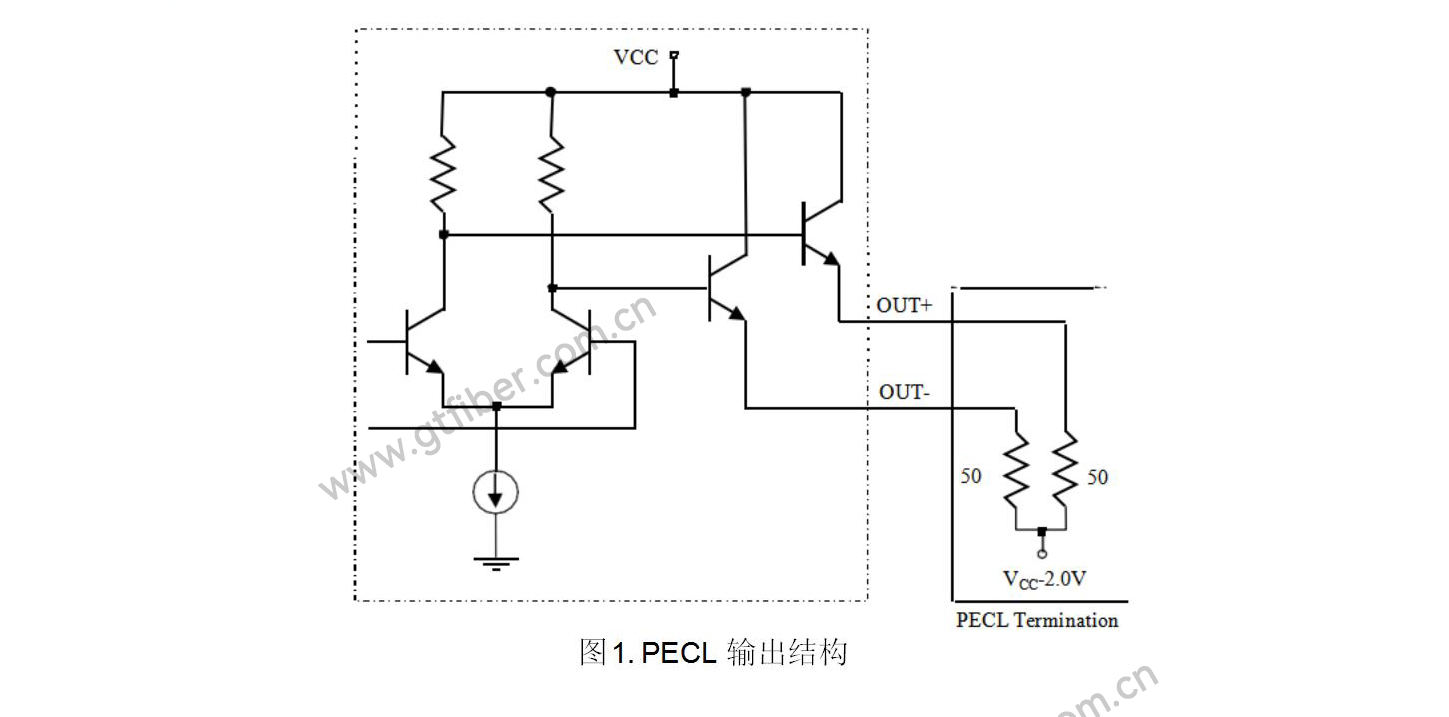

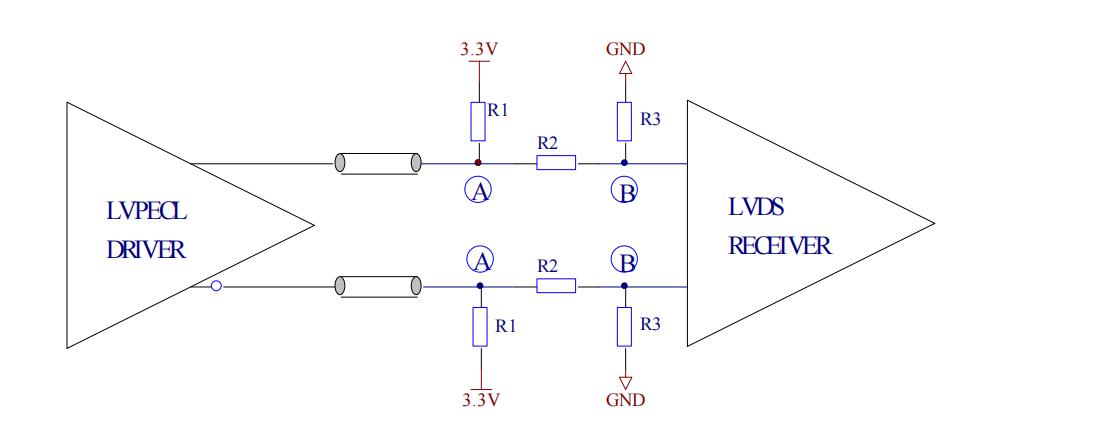

(1)LVPECL 到 LVDS 的直流耦合

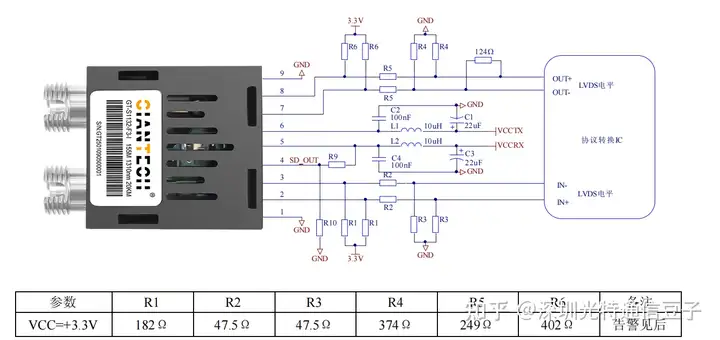

LVPECL 输出为射极跟随器结构,最优负载为 50Ω 且端接至 VCC-2V(3.3V 供电时为 1.3V),可保证最大输出摆幅与线性度;而 LVDS 输入为差分结构,差分阻抗 100Ω(单端 50Ω 至虚拟地),且无直流通路(交流阻抗≠直流阻抗)。因此需设计电阻网络实现两者匹配(如图 1 所示)。

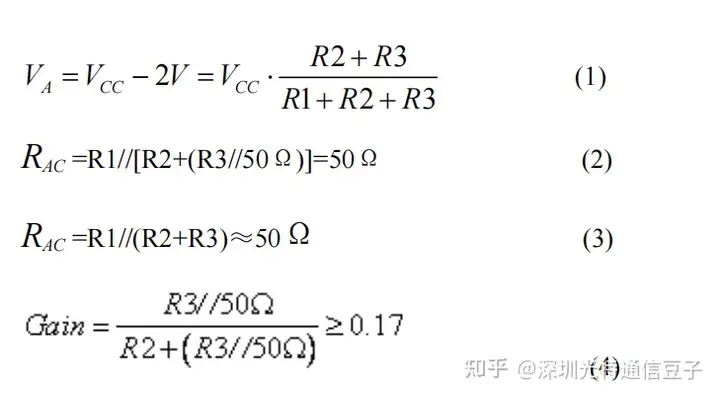

设计方程与参数计算(3.3V 供电时):

需满足 “等效最优负载” 与 “衰减后信号兼容 LVDS 输入”,解得:

电阻值:R1=182Ω,R2=47.5Ω,R3=47.5Ω

阻抗特性:交流阻抗 RAC=51.5Ω(接近 50Ω 匹配),直流阻抗 RDC=62.4Ω

信号衰减:增益 = 0.337(衰减约 3 倍)

实测验证:

共模电压:VA=2.1V(LVDS 共模范围为 0.2V~2.0V,接近上限,需结合器件容限确认),VB=1.06V

信号摆幅:LVPECL 最小差分输出 930mV 时,LVDS 输入端为 313mV(满足 LVDS≥200mV 的灵敏度要求);最大输出 1.9V 时,LVDS 输入 640mV(低于 LVDS 最大输入限制)

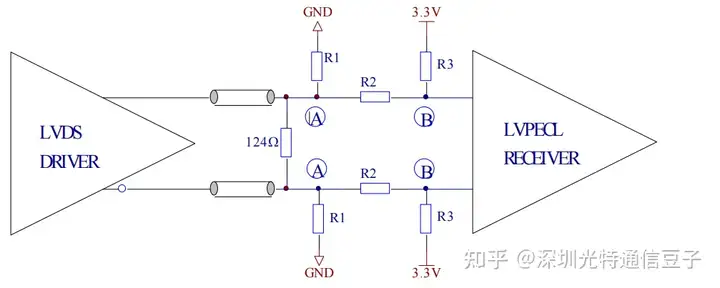

(2)LVDS 到 LVPECL 的直流耦合

LVDS 输出共模电压约 1.2V(以地为参考),而 LVPECL 输入共模电压需为 VCC-1.3V(3.3V 供电时为 2.0V,以 VCC 为参考),电阻网络需完成电平转换并抑制电源波动影响(如图 2 所示)。

设计要点:

电平转换:将 1.2V(LVDS 共模)转换至 2.0V(LVPECL 共模),避免电源波动导致共模偏移

速度与功耗折中:电阻过小(如 100Ω 级)可减小 RC 时间常数(提升速度),但会增加电流(功耗上升);电阻过大会降低速度,需根据速率需求选择

阻抗匹配:保证输入阻抗与传输线匹配(典型 50Ω)

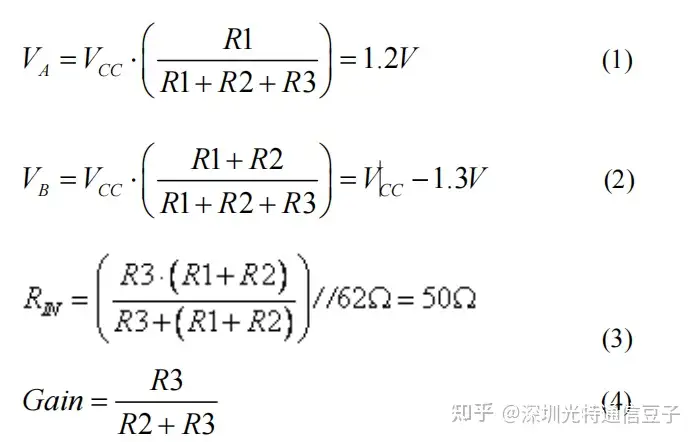

参数计算(3.3V 供电时):

解得 R1=374Ω,R2=249Ω,R3=402Ω,输入阻抗 RIN=49Ω(接近 50Ω),增益 = 0.62。

信号验证:LVDS 最小输出 500mVp-p 时,LVPECL 输入端为 310mVp-p(略低于 LVPECL 标准,实际需结合器件手册调整电阻值)

(3)应用案例:光模块与协议转换 IC 的直流耦合

在光模块(LVPECL 接口)与协议转换 IC(LVDS 接口)的互连中,直流耦合可减少延迟,适用于 10Gbps 以下速率场景。

典型布局需注意:

电阻网络靠近接收端(LVDS 或 LVPECL 芯片),缩短 stub 线(≤5mm)

差分线阻抗控制为 100Ω,长度匹配误差≤5%(减少时序偏移)

1.2 交流耦合:隔直与偏置设计

交流耦合通过串联电容隔断直流,适用于共模电压差异大或需隔离电源噪声的场景(如跨板互连)。设计核心是偏置电阻设置(建立直流工作点)与阻抗匹配(避免信号反射)。

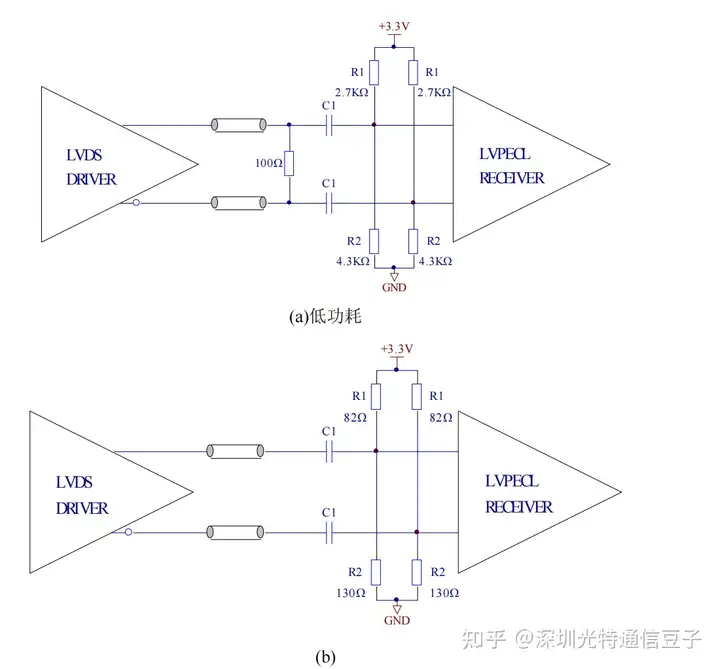

(1)LVPECL 到 LVDS 的交流耦合

需满足:

LVPECL 输出端:加 142Ω~200Ω 直流偏置电阻(接 VCC-2V),维持输出管工作点

信号通道:串联 50Ω 电阻(与传输线匹配,抑制反射)

LVDS 输入端:加 5.0kΩ 偏置电阻(接共模电压 1.2V),建立输入直流工作点

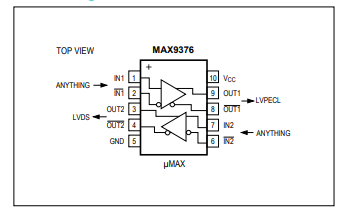

(2)LVDS 到 LVPECL 的交流耦合

结构如图 5 所示,设计简化:

若 LVPECL 芯片内部集成输入偏置电路,可省去外部 R1(上拉)、R2(下拉)电阻

信号通道仍需串联 50Ω 匹配电阻,保证阻抗连续

二、PECL 与 LVDS 的互连设计

PECL 为 5V 供电的射极耦合逻辑(与 3.3V LVPECL 兼容,仅共模电压不同),其与 LVDS 的互连设计类似 LVPECL,但需注意供电电压差异导致的参数调整。

2.1 交流耦合设计(主流方案)

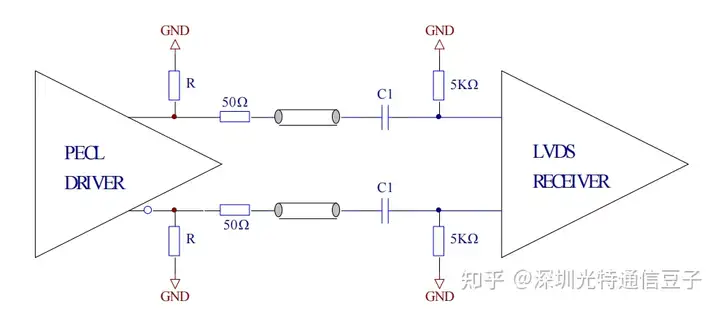

(1)PECL 到 LVDS 的交流耦合

结构如图 6 所示,参数适配 5V 供电:

PECL 输出偏置电阻:270Ω~350Ω(接 VCC-2V,5V 时为 3V)

信号通道:串联 50Ω 匹配电阻

LVDS 输入偏置:5.0kΩ 电阻(接 1.2V 共模)

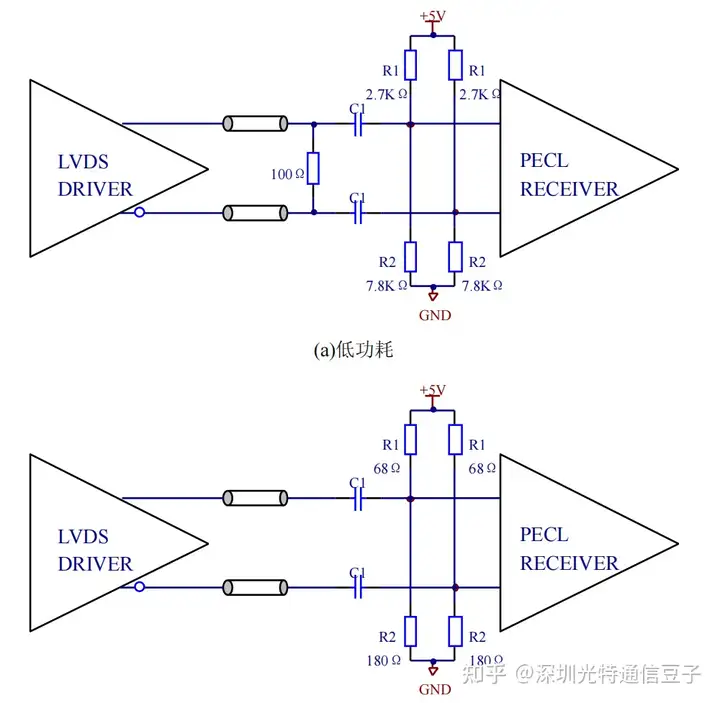

(2)LVDS 到 PECL 的交流耦合

结构如图 7 所示,分两种接法:

普通接法:需外部 R1(上拉至 VCC)、R2(下拉至地)提供偏置

简化接法:若 PECL 芯片内部集成偏置,可省去 R1、R2

2.2 匹配电路参数表(光模块应用场景)

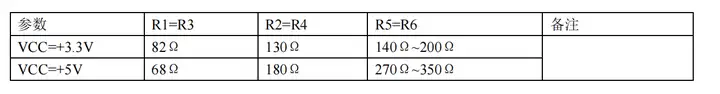

| 供电电压 | R1=R3(偏置电阻) | R2=R4(偏置电阻) | R5=R6(串联匹配电阻) | 备注 |

|---|---|---|---|---|

| +3.3V | 2.7kΩ | 4.7kΩ | 140Ω~200Ω | 接 100Ω 电阻可降功耗 |

| +5V | 2.7kΩ | 7.8kΩ | 270Ω~350Ω | - |

表 1:PECL/LVPECL 与 LVDS 交流耦合的匹配电阻参数

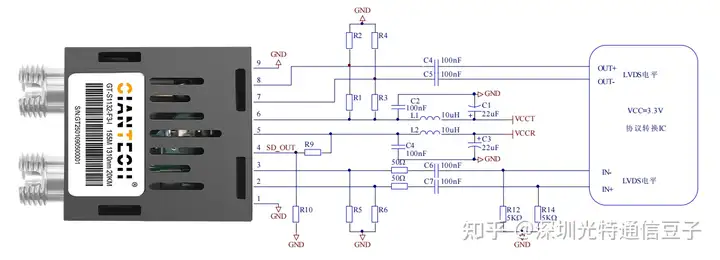

应用案例:光模块与协议转换 IC 的交流耦合

如图 8 所示,跨板互连时优先选择交流耦合:

电容值选择:根据信号速率,取 100nF(低速,≤1Gbps)或 10nF(高速,10Gbps 级),保证低频信号无衰减

布局要求:电容靠近接收端,与偏置电阻组成 “偏置网络”,减少寄生参数影响

三、设计总结与注意事项

耦合方式选择:

直流耦合:适用于同板、低噪声环境,速率≥10Gbps 时优先(无电容延迟)

交流耦合:适用于跨板、电源隔离场景,需注意电容值与偏置电阻匹配

阻抗匹配核心:

传输线阻抗控制为 100Ω(差分),串联电阻与接收端输入阻抗之和需接近 100Ω,避免反射导致的信号抖动。

电平兼容性验证:

实际应用中需结合具体器件手册(如 LVPECL 输出摆幅、LVDS 输入共模范围)调整电阻值,不可直接套用理论参数。

光模块场景优化:

光模块输出端(LVPECL/PECL)需优先保证低噪声,电阻网络应选用高精度(1%)、低温度系数(≤100ppm/℃)的贴片电阻,减少温漂对信号的影响。

光特通信作为专业光模块研发制造商,可根据客户需求提供 LVPECL/LVDS/PECL 互连的定制化方案,从阻抗匹配、信号完整性仿真到量产测试全程保障,支持 OEM/ODM 定制服务。

审核编辑 黄宇

-

lvds

+关注

关注

2文章

1131浏览量

67795 -

LVPECL

+关注

关注

2文章

46浏览量

18395 -

PECL

+关注

关注

0文章

327浏览量

14503 -

光模块

+关注

关注

80文章

1451浏览量

60557

发布评论请先 登录

LVDS、PECL和CML输出/入结构介绍

MAX9374/MAX9374A差分LVPECL至LVDS变换器技术手册

MAX9376 LVDS/任意逻辑至LVPECL/LVDS、双路电平转换器技术手册

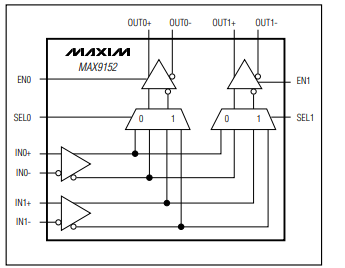

MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉点开关技术手册

差分晶振-LVPECL到LVDS的连接

LVPECL 与 LVDS 及 PECL 与 LVDS 的互连技术解析

LVPECL 与 LVDS 及 PECL 与 LVDS 的互连技术解析

评论