随着通讯速度的提升,出现了很多差分传输接口,以提升性能,降低电源功耗和成本。早期的技术,诸如emitter-coupled logic(ECL),使用不变的负电源供电,在当时用以提升噪声抑制。随着正电压供电技术发展,诸如TTL和CMOS技术,原先的技术优点开始消失,因为他们需要一些-5.2V或-4.5V的电平。

在这种背景下,ECL转变为positive/pseduo emitter-coupled logic (PECL),简化了板级布线,摒弃了负电平供电。PECL要求提供800mV的电压摆幅,并且使用5V对地的电压。LVPECL类似于PECL也就是3.3V供电,其在电源功耗上有着优点。

当越来越多的设计采用以CMOS为基础的技术,新的高速驱动电路开始不断涌现,诸如current mode logic(CML),votage mode logic(VML),low-voltage differential signaling(LVDS)。这些不同的接口要求不同的电压摆幅,在一个系统中他们之间的连接也需要不同的电路。

· 转换原因?

1、?电平特性差异?

a)LVPECL电平的差分摆幅较大(典型值约800mV),共模电压较高(约1.3V-1.9V),需外部端接电阻匹配;而LVDS差分摆幅较小(350mV),共模电压较低(约1.2V),且LVDS接收端内置端接电阻?。

b)直接连接可能导致LVDS接收端共模电压超出范围或信号幅度不足?。

2、?应用场景需求?

a)LVPECL常用于高速时钟或数据传输场景(如FPGA输出),而LVDS因低功耗特性更适合长距离或低功耗设计??。

b)不同器件间接口不兼容时需电平转换(如FPGA输出LVPECL,但接收端仅支持LVDS)?

· 转换方式

1、直流耦合

LVPECL到LVDS 的直流耦合结构需要一个电阻网络,如图1.1中所示,设计该网络时有这样几点必须考虑:首先,我们知道当负载是50Ω接到Vcc-2V 时,LVPECL 的输出性能是最优的,因此我们考虑该电阻网络应该与最优负载等效;然后我们还要考虑该电阻网络引入的衰减不应太大,LVPECL 输出信号经衰减后仍能落在LVDS 的有效输入范围内。注意LVDS 的输入差分阻抗为100Ω,或者每个单端到虚拟地为50Ω,该阻抗不提供直流通路,这里意味着LVDS输入交流阻抗与直流阻抗不等.经计算,电阻值为:R1=182Ω,R2=48Ω,R3=48Ω。电阻靠近接收侧放置。

(a)等效电路 (b)LVPECL到LVDS的连接

图1.LVPECL到LVDS的直流耦合结构

2、交流耦合

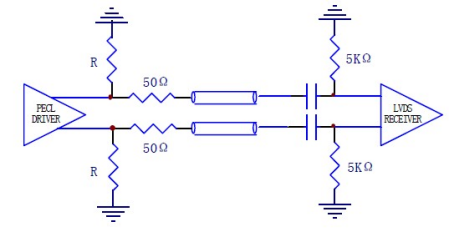

LVPECL 到LVDS 的交流耦合结构如图2 所示,LVPECL 的输出端到地需加直流偏置电阻(142Ω到200Ω),同时信号通道上一定要串接50Ω电阻,以提供一定衰减。LVDS 的输入端到地需加5KΩ电阻,以提供近似0.86V 的共模电压。

图2.LVPECL到LVDS的交流耦合结构

在信号转换方面,LVPECL到LVDS的转换则需要考虑衰减电阻和交流耦合电容的放置,以及LVDS接收器的重新偏置。相反,LVDS到LVPECL的转换也需要适当的电路设计和元件选择。

LVDS和LVPECL各有其特点和应用场景。LVDS适用于板内信号传输和高速变化信号的传输,而LVPECL则适用于背板传输和长线缆传输等需要强驱动能力和高传输速度的应用。不过,虽然LVPECL到LVDS的转换可以通过电路的设计可以实现,这边建议客户尽量选用相同类型波形的差分传输接口,毕竟电路转换会有很多其他不确定的影响。

-

晶振

+关注

关注

35文章

3280浏览量

70516 -

lvds

+关注

关注

2文章

1128浏览量

67649 -

LVPECL

+关注

关注

2文章

45浏览量

18371 -

扬兴科技

+关注

关注

1文章

164浏览量

3263 -

差分晶振

+关注

关注

0文章

147浏览量

867

发布评论请先 登录

浅谈LVDS、CML、LVPECL三种差分逻辑电平之间的互连

SiTime差分晶振的LVDS、LVPECL、HCSL、CML模式相互转换过程介绍

从SerDes到SoC,全场景适配的FCom差分晶振设计全解

从SFP到OSFP:FCom差分晶振覆盖全类型光模块的时钟设计方案

差分晶振-LVPECL到LVDS的连接

差分晶振-LVPECL到LVDS的连接

评论