01引言

在图像与视频处理领域,灵活、高效、低延迟的解决方案一直是行业追求的目标。西安智多晶微电子有限公司推出的AXI视频通讯DEMO方案,基于智多晶SA5Z-30-D1-8U213C FPGA器件,通过FPGA逻辑与内嵌CM3硬核的协同工作,结合DDR2高速存储,实现了从图像采集、处理到显示的全流程优化。本文将带您深入了解这一方案的亮点与操作流程。

02DEMO方案介绍

方案系统框架

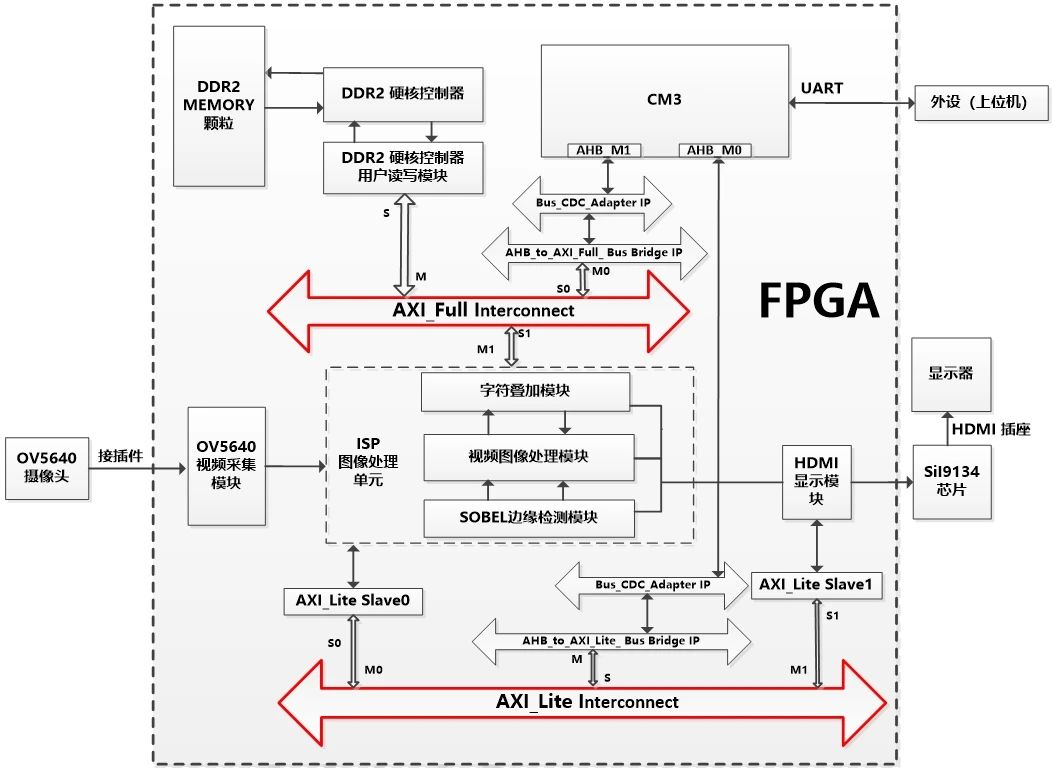

图1 AXI 视频通讯DEMO系统框图

方案亮点

强大的硬件配置

FPGA+CM3硬核协同:SA5Z-30-D1-8U213 FPGA内嵌Cortex-M3硬核,通过AHB总线与FPGA逻辑交互,实现高效数据处理。

高速存储支持:FPGA器件内嵌128Mbit DDR2颗粒,速率可达800Mbps,满足高清视频(1280x720@60fps)的实时缓存需求。

多接口支持:支持OV5640 Sensor模组输入与SiI9134 HDMI输出,覆盖从采集到显示的完整链路。

灵活的软件控制

通过上位机发送指令,可动态配置图像处理模式,包括:

边缘检测:支持Sobel算法,阈值可调(0-255)。

字符叠加:支持中英文LOGO叠加或关闭。

显示切换:一键切换Sensor模组输入的视频或上位机发送的图片。

采用BUS_CDC模块解决FPGA与CM3的时钟域差异,确保数据可靠传输。

通过AHB-to-AXI桥接IP,实现CM3的AHB接口与FPGA侧AXI接口的无缝转换。

AXI_Full Interconnect、AXI_Lite Interconnect模块实现多个AXI MASTER与多个AXI SLAVE之间的总线互联。

设计规格

?OV5640 Sensor模组输入视频分辨率1280X720@60

?HDMI输出视频分辨率1280X720@60

?DDR2 速率800Mbps

?CM3 运行速率200Mhz

03DEMO方案软硬件环境及操作指南

AXI视频通讯DEMO整体的软硬件环境如图2所示,本DEMO是基于智多晶EVAL_SA5Z-30-D1- 8U213C V1.2 DEMO板开发,用户使用本DEMO时,需要按照图2所示将硬件环境搭建起来,首先是将OV5640 Sensor模组通过DEMO板上的P2接口与DEMO板相连,然后用HDMI线通过DEMO板上的HDMI接口将DEMO板与显示器相连,最后通过串口线将带有上位机调试软件的笔记本电脑与DEMO板相连,至此AXI视频通讯DEMO整体的软硬件环境搭建完成。

环境搭建

硬件连接:

OV5640摄像头接入DEMO板P2接口。

HDMI线连接显示器。

串口线连接PC与DEMO板。

软件配置:

使用上位机调试软件,设置串口通信发送模式。

功能演示

通过上位机软件发送控制命令给FPGA

边缘检测:

发送sobel-on开启,sobel-off关闭、sobel-threshold+阈值(如100)调整边缘检测强度。

LOGO叠加:

通过char-ch(中文)、char-eng(英文)或char-none(关闭)控制。

显示切换:

hdmi-video显示Sensor模组画面,hdmi-picture显示上位机传输图片。

图片上传:

发送send-picture指令后,选择图片文件传输至DDR2缓存。

应用场景

工业检测:实时边缘检测用于缺陷识别。

智能监控:动态叠加时间或标识信息。

医疗影像:高清视频流的低延迟处理与显示。

03结语

智多晶AXI视频通讯DEMO方案凭借其灵活的硬件架构和丰富的软件控制功能,为图像处理应用提供了灵活、高效、可靠的解决方案。无论是研发测试还是教学演示,这一方案都能显著提升开发者的效率。如需了解DEMO方案的具体实现过程,请访问西安智多晶微电子官网获取更多技术支持。

-

FPGA

+关注

关注

1646文章

22096浏览量

620599 -

视频

+关注

关注

6文章

1976浏览量

74115 -

存储

+关注

关注

13文章

4556浏览量

87723 -

DDR2

+关注

关注

1文章

105浏览量

42031

原文标题:“芯”技术分享 | FPGA+CM3硬核协同,打造高效图像处理方案

文章出处:【微信号:智多晶,微信公众号:智多晶】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

ZYNQ PS + PL异构多核案例开发手册之1axi_gpio_led_demo案例

AXI VIP当作master时如何使用

汽车后视镜应用方案Demo

国产智多晶FPGA介绍及应用

AXI4S接口视频协议在视频IP中的应用总结

AXI4Stream总线的FPGA视频系统的开发研究

AXI 总线和引脚的介绍

如何使用Xilinx AXI进行验证和调试

PCI Express解决方案的介绍

全面介绍ZYNQ-AXI互联IP

智多晶AXI视频通讯DEMO方案介绍

智多晶AXI视频通讯DEMO方案介绍

评论