µÚŇ»ĆÚ

ÖǶྦྷDDR Controller˝éÉÜ

±ľĆÚÖ÷ŇŞ˝éÉÜÖǶྦྷDDR ControllerµÄłŁĽűÓ¦ÓĂÁěÓňˇ˘ÄÚ˛ż˝áąąˇ˘¸÷ÄŁżéą¦Äܡ˘ĹäÖĂ˝çĂ桢ĹäÖòÎĘýµČÄÚČݡŁ

01ÖǶྦྷDDR ControllerÓ¦ÓĂÁěÓň

1.1ą¤żŘÁěÓň

ÔÚą¤ŇµżŘÖĆϵͳÖĐŁ¬É豸ĐčŇŞł¤Ę±ĽäÎȶ¨ÔËĐĐŁ¬Í¬Ę±¶ÔĘýľÝµÄʵʱĐÔşÍ׼ȷĐÔŇŞÇ󼫸ߡŁÖǶྦྷDDR ControllerµÄ¸ßżÉżżĐԺ;«×ĽĘ±ĐňżŘÖĆÄÜÁ¦Ł¬ĘąĆäłÉÎŞą¤żŘÁěÓňµÄŔíĎëѡÔńˇŁŔýČ磬ÔÚPLCŁ¨żÉ±ŕłĚÂ߼żŘÖĆĆ÷Ł©ÖĐŁ¬ËüÄÜą»żěËŮĎěÓ¦¸÷ÖÖ´«¸ĐĆ÷Đźţ¬ĘµĘ±´¦ŔíşÍ´ć´˘´óÁżµÄżŘÖĆĘýľÝŁ¬Č·±ŁÉú˛úÉ豸µÄľ«×ĽżŘÖƺ͸ßЧÔËĐСŁ´ËÍ⣬ÖǶྦྷµÄSEAL 5000µÄSA5Z-30ˇ˘SA5Z-50ˇ˘SA5Z-100µČFPGAĆ÷ĽţÄÚÖĂÁËARMşËşÍDDR ControllerŁ¬ŐâÖÖŇ»Ě廯µÄÉčĽĆ˛»˝öĚá¸ßÁËϵͳµÄĽŻłÉ¶ČŁ¬»ą˝µµÍÁËą¦şÄşÍłÉ±ľˇŁÔÚһЩ¸´ÔӵŤҵ×Ô¶Ż»Żłˇľ°ÖĐŁ¬Čç»úĆ÷ČËżŘÖơ˘ÖÇÄÜą¤ł§µÄÉú˛úµ÷¶ČϵͳµČŁ¬ŐâÖÖFPGAÄÚÖĂDDR ControllerµÄ·˝°¸ÄÜą»ĘµĎÖČíÓ˛ĽţĐͬÉčĽĆŁ¬˝«żŘÖĆÁ÷ÓëËă·¨Á÷·ÖżŞ´¦ŔíŁ¬´ó·ůĚáÉýÔËËăËٶȺÍϵͳĐÔÄÜŁ¬Í¬Ę±ĽćąËÁËĐÔÄܺͳɱľµÄĆ˝şâˇŁ

1.2ͨĐĹÁěÓň

Ëć×Ĺ5Gˇ˘6GµČ¸ßËŮͨĐĹĽĽĘőµÄ·˘ŐąŁ¬¶ÔĘýľÝ´«ĘäËŮÂʺʹřżíµÄŇŞÇóÔ˝Ŕ´Ô˝¸ßˇŁÖǶྦྷDDR ControllerÖ§łÖ¶ŕÖÖ¸ßËٽӿں͸ßĐÔÄÜDDR´ć´˘Ł¬ÄÜą»Âú×ăͨĐĹÉ豸¶Ô´óĘýľÝÁżżěËŮ´ć´˘şÍ¶ÁȡµÄĐčÇóˇŁÔÚ»ůŐľÉ豸ÖĐŁ¬ËüÄÜą»¸ßЧ´¦Ŕí´óÁżµÄĐĹşĹĘýľÝŁ¬Ö§łÖ¸ßËٵÄĘýľÝ»ş´ćşÍ´«Ę䣬ȷ±ŁĐźŵÄʵʱ´¦ŔíşÍ·˘Ë͡ŁÍ¬Ę±Ł¬ÔÚÍřÂç˝»»»»úˇ˘Â·ÓÉĆ÷µČÉ豸ÖĐŁ¬ÖǶྦྷDDR ControllerÄÜą»żěËٵ÷¶ČşÍת·˘ĘýľÝ°üŁ¬Ěá¸ßÍřÂçµÄÍĚÍÂÁżşÍĎěÓ¦Ëٶȣ¬ÎŞÓĂ»§Ěáą©¸üÁ÷ł©µÄͨĐĹĚĺŃ顣

1.3Ďű·Ńµç×ÓÁěÓň

ÔÚĘÖłÖÉ豸µČĎű·Ńµç×Ó˛úĆ·ÖĐŁ¬ÓĂ»§¶ÔÉ豸µÄĐÔÄܺ͹¦şÄ¶Ľ·ÇłŁąŘעˇŁÖǶྦྷDDR ControllerµÄ¸ßЧĘýľÝ´«ĘäÄÜÁ¦şÍµÍą¦şÄÉčĽĆŁ¬ĘąĆäÄÜą»ÎŞŐâĐ©É豸Ěáą©Çżľ˘µÄĐÔÄÜÖ§łÖˇŁŔýČ磬ÔÚĘÖłÖÉ豸ÖĐŁ¬ËüÄÜą»żěËٶÁȡşÍ´ć´˘Ó¦ÓĂłĚĐňĘýľÝˇ˘¸ßÇĺͼƬşÍĘÓƵµČŁ¬ĚáÉýÉ豸µÄÔËĐĐËٶȺÍĎěÓ¦ÄÜÁ¦ˇŁÍ¬Ę±Ł¬Í¨ąýÓĹ»ŻµÄʱĐňżŘÖƺ͵çÔ´ąÜŔíŁ¬ÓĐЧ˝µµÍÁËÄÚ´ć·ĂÎĘąýłĚÖеŦşÄŁ¬ŃÓł¤ÁËÉ豸µÄĐřş˝Ę±ĽäŁ¬ČĂÓĂ»§ÄÜą»¸üł¤Ę±ĽäµŘĎíĘܸ÷ÖÖą¦ÄܡŁ

1.4Ćűłµµç×ÓÁěÓň

Ëć×ĹĆűłµÖÇÄÜ»ŻµÄ·˘ŐąŁ¬Ćűłµµç×ÓϵͳĐčŇŞ´¦ŔíÔ˝Ŕ´Ô˝¶ŕµÄĘýľÝŁ¬Čç×Ô¶ŻĽÝĘ»¸¨ÖúϵͳÖеÄÍĽĎńʶ±đˇ˘´«¸ĐĆ÷ĘýľÝČںϵȡŁÖǶྦྷDDR ControllerµÄ¸ßżÉżżĐÔşÍʵʱĐÔŁ¬ÄÜą»Âú×ăĆűłµµç×Óϵͳ¶ÔĘýľÝ´¦ŔíµÄŃϸńŇŞÇóˇŁÔÚ×Ô¶ŻĽÝĘ»¸¨ÖúϵͳÖĐŁ¬ËüÄÜą»żěËŮ´¦ŔíŔ´×ÔÉăĎńÍ·ˇ˘Ŕ×´ďµČ´«¸ĐĆ÷µÄ´óÁżĘýľÝŁ¬ĘµĘ±ÉúłÉ׼ȷµÄ»·ľł¸ĐÖŞĐĹϢŁ¬ÎŞłµÁľµÄ×Ô¶ŻĽÝĘ»ľö˛ßĚáą©ÓĐÁ¦Ö§łÖˇŁ

02ÖǶྦྷDDR Controller˝éÉÜ

ÖǶྦྷµÄSeal 5000ϵÁĐFPGAоƬŁ¬ÄÚÖĂDDR ControllerÓ˛şËˇŁĆäÖĐSA5Z-30ϵÁĐÖеÄD1_U213ÄÚǶÁË128MbµÄDDR2żĹÁŁˇ˘D2_U256ÄÚǶÁË512MbµÄDDR2żĹÁŁˇ˘D3_U256ÄÚǶÁË1GbµÄDDR3żĹÁŁŁ»Őâ¶ÔÓĂ»§Ŕ´ËµŁ¬˛»µ«˝µµÍÁËÉčĽĆµÄÄѶȣ¬Ň˛ÓĐÖúÓÚ˝µµÍϵͳą¦şÄŁ¬ÓĐŔűÓÚĚáÉý˛úĆ·ľşŐůÁ¦ˇŁSA5Z-30ϵÁĐŁ¨D0_U324Ł©ˇ˘SA5Z-50ϵÁС˘SA5T-100ϵÁС˘SA5T-366ϵÁĐŁ¬żÉŇÔÍâąŇDDR3żĹÁŁŁ¬ĆäÖĐSA5T-366ϵÁĐ»ąÖ§łÖÍâąŇDDR4żĹÁŁˇŁ

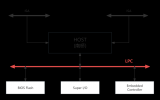

2.1 DDR Controller˝áąążňÍĽ

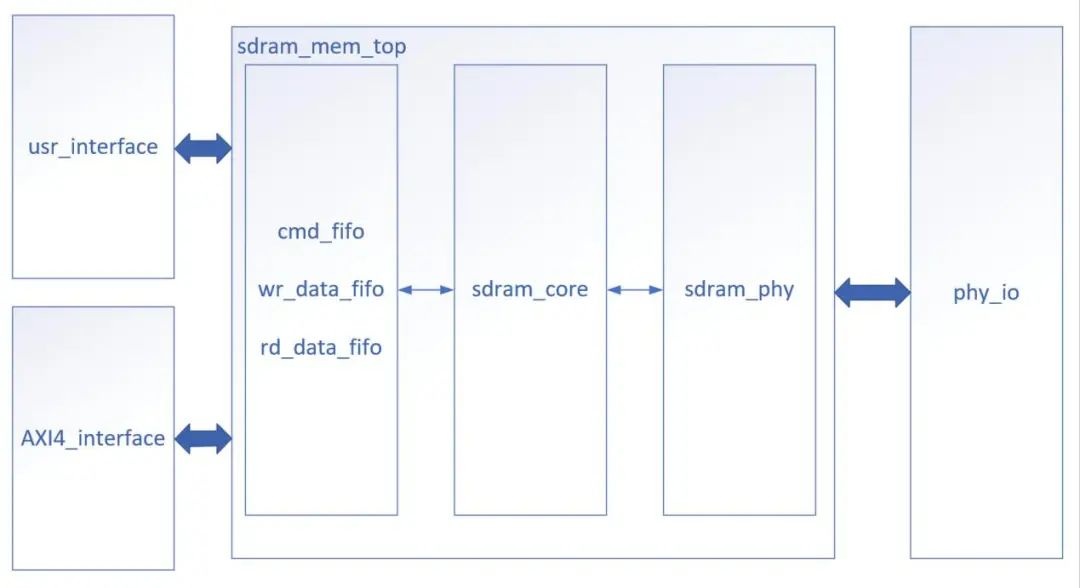

DDR Controller˝áąążňÍĽŁ¬ČçÍĽŇ»ËůĘľŁ¬ĆäÖĐuser_interfaceÄŁżéÎŞDDR2/3 ControllerµÄÓĂ»§˝ÓżÚ˛ż·ÖŁ¬ÓÉČíÂ߼ʵĎÖŁ»sdram_mem_topÄŁżéDDR2/3 ControllerµÄşËĐÄżŘÖƲż·ÖŁ¬ÓÉÓ˛şËʵĎÖŁ»phy_ioÄŁżéĘÇDDR2/3 ControllerµÄÄŁÄâµç·˛ż·ÖŁ¬ÓÉČíÂ߼şÍÔÓďʵĎÖˇŁ

ÍĽŇ» DDR Controller˝áąążňÍĽ

2.1.1¸÷ÄŁżéą¦ÄÜĽňĘö

user_interfaceÄŁżéŁ¬˛ÉÓĂŔŕËĆÓÚAXI-Stream×ÜĎߵķ˝Ę˝Ł¬Í¨ąýreadyˇ˘validşÍlastĐĹşĹÎŐĘÖ·˝Ę˝Ł¬ĘµĎÖĂüÁîşÍ¶ÁĐ´ĘýľÝµÄżŘÖơŁ

AXI4_interfaceÄŁżéŁ¨ÄżÇ°˝öÖ§łÖSA5T-100ϵÁĐŁ©Ł¬˛ÉÓñę׼µÄAXI4˝ÓżÚˇŁ

sdram_mem_topÄŁżé°üş¬Łşinterface_fifoÄŁżéˇ˘sdram_coreÄŁżéşÍsdram_phyÄŁżéˇŁsdram_phyÄŁżéÖĐ°üş¬Initialization Logicˇ˘Read Training LogicşÍWrite Leveling LogicµČ×ÓÄŁżéˇŁ

phy_ioÄŁżéŁ¬ÔÚSA5Z-30Ć÷ĽţDDR ControllerĘąÓĂODDRx2/IDDRx2Ł¬ĆäÓŕĆ÷ĽţDDR ControllerĘąÓĂODDRx4/IDDRx4ˇŁ

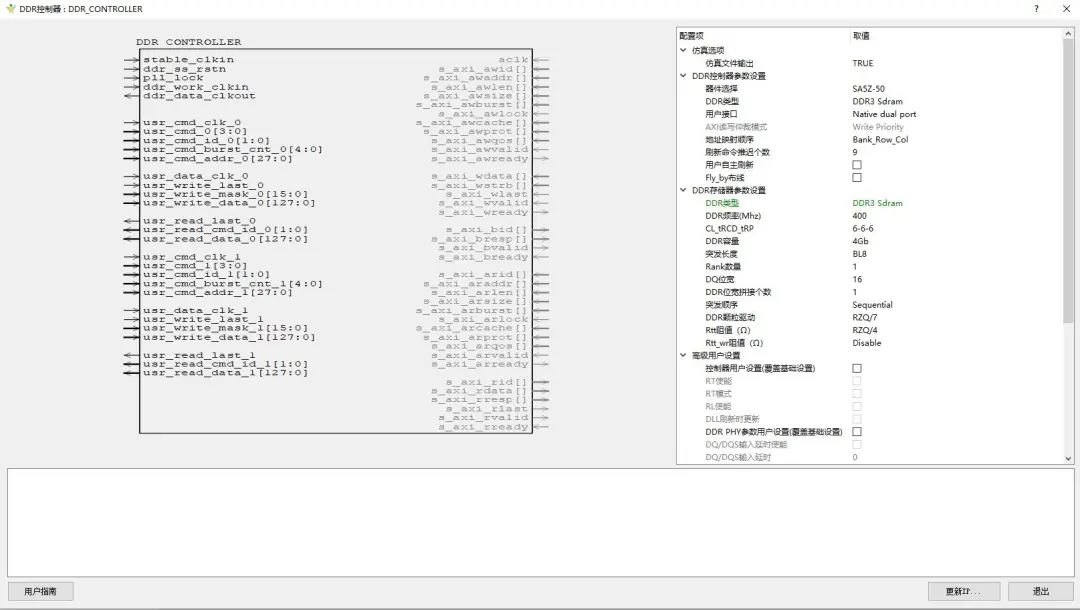

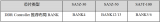

2.2 DDR ControllerĹäÖĂ˝çĂć

ÍĽ¶ţÎŞÖǶྦྷDDR ControllerµÄĹäÖĂ˝çĂ棬żÉŇÔż´µ˝°üş¬Ň»Đ©±ŘĐëµÄĹäÖòÎĘýŁ¬·˝±ăżÍ»§¸ůľÝ×ÔĽşµÄÓ˛ĽţÉčĽĆŁ¬Áé»îµŘĹäÖĂŁ»ĎÂĂć»á¶ÔĆäĹäÖòÎĘý×öĎęϸµÄ˝éÉܡŁ

ÍĽ¶ţ DDR ControllerĹäÖĂ˝çĂć

2.3 DDR ControllerĹäÖĂ˝çĂć˛ÎĘýş¬Ňĺ

2.3.1 Ć÷ĽţѡÔń

¸ůľÝÉčĽĆÖĐĘąÓõÄоƬŁ¬żÉŇÔѡÔńÎŞSA5Z-30ˇ˘SA5Z-50ˇ˘SA5T-100ˇ˘SA5T-336ˇŁ

2.3.2 DDR ŔŕĐÍ

DDR ŔŕĐÍŁ¬żÉŇÔѡÔńÎŞ DDR2 Sdram »ň DDR3 SdramˇŁSA5Z-30-D1-U213şÍ SA5Z-30-D2-U256ÎŞşĎ·âDDR2Ł¬SA5Z-30-D3-U256ÎŞşĎ·âDDR3Ł»ĆäÓŕоƬĐčŇŞÍâąŇDDRżĹÁŁˇŁ

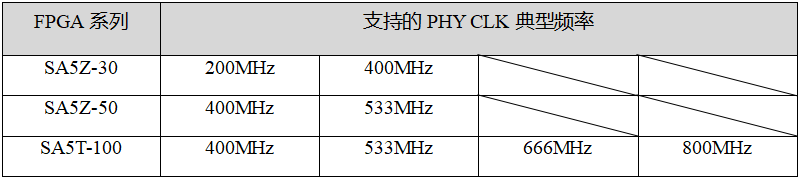

2.3.3 DDR ƵÂĘ

˛»Í¬ĐͺŵÄFPGAĆ÷ĽţŁ¬DDR ControllerÖ§łÖµÄƵÂĘ·¶Î§˛»Ň»ŃůˇŁÓĂ»§Ö»ÄÜÔÚĎ޶¨µÄƵÂĘ·¶Î§ÄÚѡÔńşĎĘʵÄƵÂĘÖµŁ¨±íÖĐδ°üş¬µÄ¸üµÍµÄƵÂĘŁ¬Ć÷ĽţҲżÉÖ§łÖŁ¬˛ÎĘýµÄѡÔńżÉŇÔ×ÉŃŻFAEŁ©ˇŁ

2.3.4CL-tRCD-tRP

DDR µÄµÚһʱĐň˛ÎĘýŁ¬»á¸ůľÝÓĂ»§ŃˇÔńµÄˇ°DDR ŔŕĐ͡±ŇÔĽ°ĘäČëµÄˇ°DDR ƵÂʡ±×Ô ¶ŻÉúłÉĎŕÓ¦µÄʱĐň˛ÎĘýą©ÓĂ»§ŃˇÔńˇŁµĄÎ»ÎŞŇ»¸öPHY CLKʱÖÓÖÜĆÚˇŁ

2.3.5DDR ČÝÁż

ÔÚѡÔń DDR ŔŕĐͺ󣬻á×Ô¶ŻÉúłÉżÉÖ§łÖµÄ DDR ČÝÁż´óСˇŁ˛»Í¬µÄ DDR ČÝÁżÓë DQ λżíĎŕąŘŁ¬»áÓ°Ďě BANKˇ˘ROWˇ˘COL µÄżí¶ČˇŁ

2.3.6 Í»·˘ł¤¶Č

ĘýľÝ´«ĘäµÄÍ»·˘ł¤¶Č·ÖÎŞ BL4şÍ BL8ˇŁÖ»ÓĐ SA5Z-30 ϵÁĐĆ÷ĽţÖ§łÖ BL4şÍ BL8 ѡĎĆäÓŕϵÁĐĆ÷ĽţÖ»Ö§łÖ BL8 ѡĎ

2.3.7 Rank ĘýÁż

ѡÔńĘąÓĂrankµÄĘýÁżŁ¬×î´óÖ§łÖ2¸örankŁ¨SA5Z-30 ˝öÖ§łÖµĄrankŁ©ˇŁ

2.3.8DQ λżí

ĘýľÝ´«ĘäͨµŔµÄżí¶ČŁ¬ÓëDDR λżíĆ´˝Ó¸öĘýą˛Í¬ľö¶¨µĄ¸öʱÖÓÖÜĆÚµÄĘýľÝ´«ĘäÁżˇŁÓĐ 8 ͨµŔĆ÷ĽţşÍ 16 ͨµŔĆ÷ĽţÁ˝¸öѡĎ˛»Í¬ DQ λżíÓë DDR ČÝÁżą˛Í¬Ó°Ďě ROWˇ˘BANKˇ˘COL µÄżí¶ČˇŁ

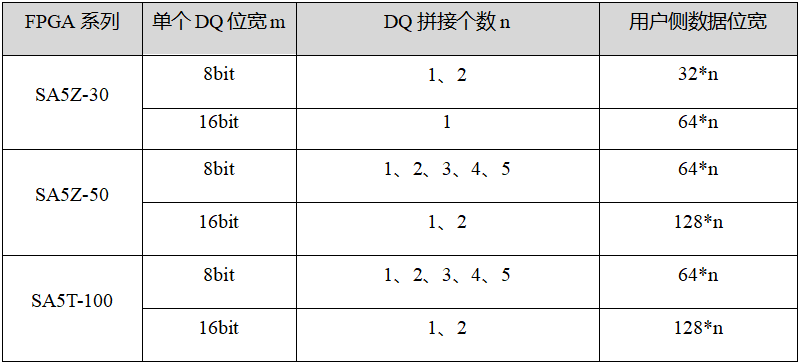

2.3.9DDR λżíĆ´˝Ó¸öĘý

¸ůľÝÓ˛Ľţ°ĺż¨ąŇÔصÄDDRżĹÁŁµÄ DQ λżíŁ¬ŃˇÔńşĎĘʵÄDDRλżíĆ´˝Ó¸öĘýˇŁ¶ÔÓÚ˛»Í¬µÄĆ÷ĽţżÉŇÔĆ´˝ÓµÄ¸öĘý˛»Í¬Ł¬Ď±íÁĐłöÁËżÉŇÔĆ´˝ÓµÄ¸öĘýşÍ¶ÔÓ¦µÄÓĂ»§˛ŕĘýľÝλżíˇŁ

עŁşDDR ControllerÖ§łÖ×î¶ŕ32bitµÄDQλżíŁ»Čçąű˛»ĘąÓĂDDR ControllerµÄÓ˛şËŁ¬ÓĂ»§żÉŇÔĘąÓĂČíÂ߼ŇÔÖ§łÖ¸üżíµÄλżíˇŁ

2.3.10Í»·˘ËłĐň

Ö§łÖ Sequential şÍ Interleaved Á˝ÖÖÍ»·˘ËłĐňˇŁSequential °´ŐŐÁ¬ĐřµŘÖ·ËłĐň·ĂÎĘ´ć´˘µĄ ÔŞˇŁInterleaved °´ŐŐĐŇéąć¶¨µÄ˝»´íģʽϷĂÎĘ´ć´˘µĄÔŞˇŁ

2.3.11DDR żĹÁŁÇý¶Ż

DDR żĹÁŁÇý¶ŻŃˇÔńˇŁDDR2 Sdram ÖĐżÉѡˇ°Full Strengthˇ±şÍˇ°Reduced Strengthˇ±ˇŁĎŕ ±ČÓë Full StrengthŁ¬Reduced Strength Çý¶ŻĐźŵÄÇż¶ČĽőČőˇŁDDR3 Sdram ÖĐżÉѡÔń RZQ/7 şÍ RZQ/6 Á˝ÖÖ×čÖµˇŁŃˇÔńşó»á×Ô¶ŻĐŢ¸Ä MR ĽÄ´ćĆ÷ÖеÄÉ趨ˇŁ

2.3.12Rtt ×čÖµ

ÓëWL ĎŕąŘODT µÄ×čżąÉčÖĂŁ¬RZQ/nŁ¬RZQ = 240¦¸ Ł¬n = 2ˇ˘4ˇ˘6ˇ˘8ˇ˘12ˇŁ

2.3.13Rtt_wr ×čÖµ

ÓëĐ´˛Ů×÷ĎŕąŘµÄ¶ŻĚ¬ ODT µÄ×čżąÉčÖáŁ

ĎÂŇ»ĆÚÎŇĂÇ˝«ĽĚĐř˝˛˝âÖǶྦྷDDR ControllerĘąÓĂʱµÄעŇâĘÂĎľ´ÇëąŘעˇŁ

-

´«¸ĐĆ÷

+ąŘע

ąŘע

2567ÎÄŐÂ

53145äŻŔŔÁż

768913 -

FPGA

+ąŘע

ąŘע

1646ÎÄŐÂ

22069äŻŔŔÁż

619729 -

DDR

+ąŘע

ąŘע

11ÎÄŐÂ

733äŻŔŔÁż

66989 -

˝»»»»ú

+ąŘע

ąŘע

22ÎÄŐÂ

2759äŻŔŔÁż

102074

ÔÎıęĚ⣺ˇ°Đľˇ±ĽĽĘő·ÖĎí | ÖǶྦྷDDR Controller˝éÉܵÚŇ»ĆÚ

ÎÄŐÂłö´¦ŁşˇľÎ˘ĐźţşÖǶྦྷŁ¬Î˘ĐĹą«ÖںţşÖǶྦྷˇż»¶ÓĚíĽÓąŘעŁˇÎÄŐÂתÔŘÇëעĂ÷łö´¦ˇŁ

·˘˛ĽĆŔÂŰÇëĎČ µÇÂĽ

ddr3 sdram controller with uniphy 17.1 ÎŢ·¨Ŕý»Ż

ÇóOMAPL138 DDR2/mDDR Controller ĎęϸµÄĽĽĘőĘÖ˛á

ąú˛úÖǶྦྷFPGA˝éÉÜĽ°Ó¦ÓĂ

ąú˛úFPGAÖǶྦྷµđ

Synthesizable 266 MBits/s DDR

TPS59116,pdf(Complete DDR, DDR

TPS51116,pdf(Complete DDR, DDR

¶ŕľ§ąčÉĎĘĐą«ËľÓĐÄÄĐ©_ąúÄڶྦྷąčÉĎĘĐą«ËľĹĹĂű

¶ŕľ§ąčÉú˛úÁ÷łĚĘÇʲô_µĄľ§ąčÓë¶ŕľ§ąčµÄÇř±đ

¶ŕľ§ąčĚ«ŃôÄÜ°ĺĆ·ĹĆ_¶ŕľ§ąčĚ«ŃôÄÜ°ĺĽŰ¸ń

ÖǶྦྷLPC_Controller IP˝éÉÜ

ÖǶྦྷDDR Controller˝éÉÜ

ÖǶྦྷDDR Controller˝éÉÜ

ĆŔÂŰ