前言

在半导体制造的前段制程中,晶圆需要具备足够的厚度,以确保其在流片过程中的结构稳定性。尽管芯片功能层的制备仅涉及晶圆表面几微米范围,但完整厚度的晶圆更有利于保障复杂工艺的顺利进行,直至芯片前制程完成后,晶圆才会进入封装环节进行减薄处理。

晶圆为什么要减薄

封装阶段对晶圆进行减薄主要基于多重考量。

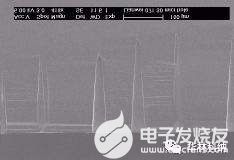

从划片工艺角度,较厚晶圆硬度较高,在传统机械切割时易出现划片不均、裂片等问题,显著提升不良率;而减薄后的晶圆硬度降低,能够实现更精准、高效的分离,大幅提升划片质量与效率。

随着电子设备向轻薄化方向发展,封装厚度已成为关键指标,尤其在芯片堆叠技术中,晶圆减薄能够有效降低整体封装厚度,满足可穿戴设备、移动终端等微型电子产品的需求。

同时,晶圆制造过程中背面形成的氧化层会影响芯片键合质量,减薄工艺可有效去除氧化层,为键合提供洁净、平整的表面,确保电气连接的可靠性。

此外,减薄能够缩短芯片工作时的热量传导路径,加速散热,避免因高温导致的性能衰退与寿命缩短,提升芯片长期运行的稳定性。

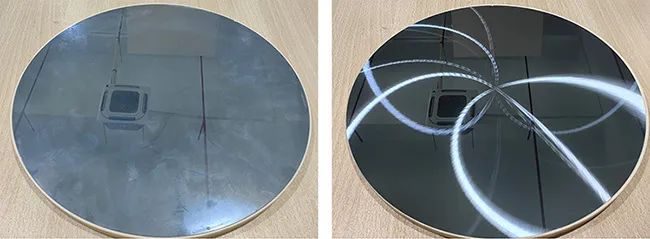

晶圆减薄前后对比

不同封装对减薄厚度的要求存在差异

引线键合(Wire Bond)封装,典型厚度为100-200微米;

传统封装(如QFP、DIP等)对厚度要求相对宽松,通常将晶圆减薄至约300微米;

BGA封装,减薄范围在100-200微米,这样的厚度可以适应球栅的布局和高度要求,同时也能保证芯片与基板之间的电气连接和机械稳定性;

CSP封装,晶圆减薄厚度一般要求在 50 - 100 微米之间。由于 CSP 封装直接将芯片与基板连接,较薄的晶圆可以减少芯片与基板之间的应力,提高封装的可靠性,同时也有助于降低信号传输延迟,满足小型化和高性能的要求。

先进的叠层封装中,芯片厚度甚至可薄至30微米以下,以满足高密度集成需求。

晶圆减薄工艺

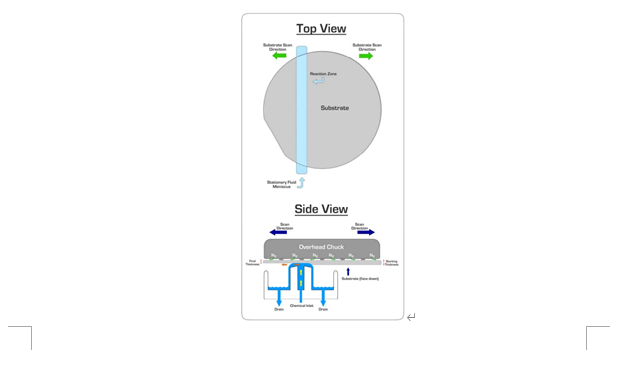

晶圆减薄工艺一般采用机械研磨、化学机械抛光(CMP)等方法。其具体流程涵盖前期准备、减薄操作(例如粗磨、精磨和抛光)以及后期处理(如清理残留物、测量平坦度和质量检测)。

减薄砂轮

在实际晶圆减薄生产中,多采用组合工艺来确保加工精度与效率。例如,若需将硅片从初始厚度减薄至120μm,可先通过高效的粗磨磨削工艺去除大部分材料,将硅片厚度削减至140μm左右。此时,硅片表面因磨削产生损伤层与残余应力,就需要根据后续产品性能要求,选择一种或多种工艺进行精细处理,实现晶圆减薄的高效化与高质量化,并确保后续划切工序的顺利进行。

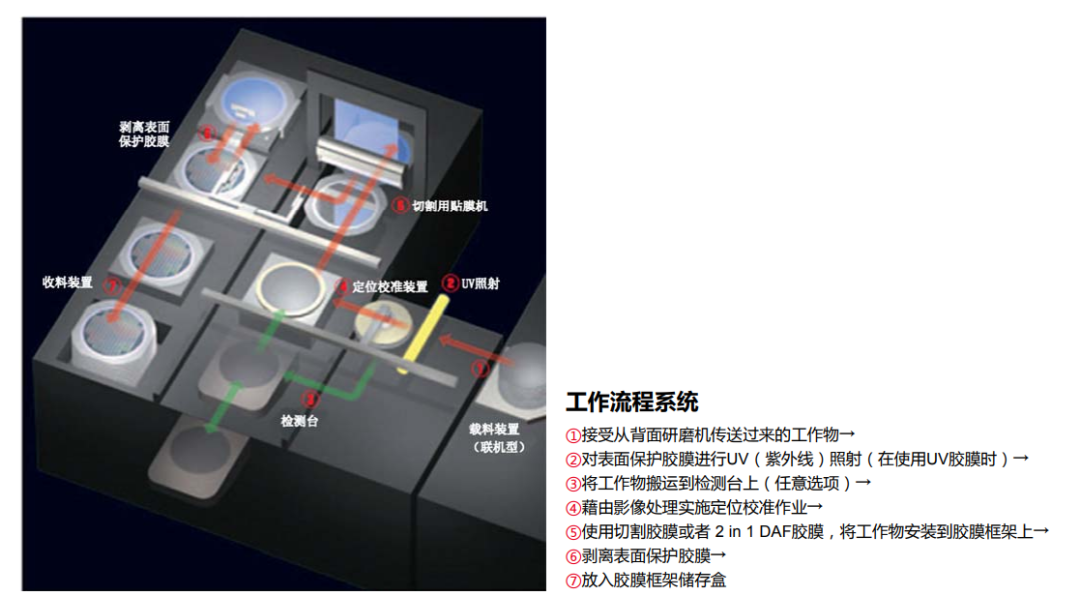

晶圆减薄与划片工艺的融合

在芯片切割环节,传统流程是先在晶圆背面粘贴蓝膜并固定于钢制框架(即晶圆黏片工艺),随后采用机械切割或激光切割进行分离。

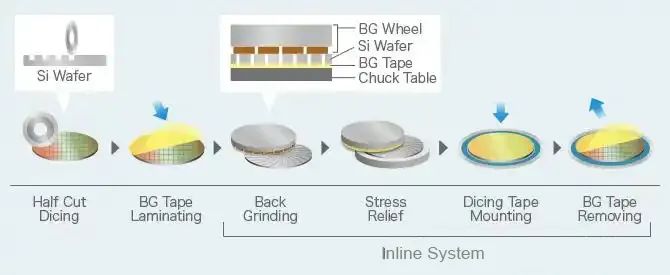

随着工艺创新,“先划片后减薄”(DBG)与“减薄划片”(DBT)技术应运而生。

DBG工艺先在晶圆正面切割出一定深度的切口,再进行背面磨削。

DBG工艺流程

DBT技术则是预先形成切割切口,通过磨削减薄后利用ADPE腐蚀去除剩余材料,实现裸芯片自动分离。这两种方法有效规避了传统工艺中减薄导致的硅片翘曲与划片造成的芯片边沿损伤问题。

其中,DBT技术凭借各向同性硅刻蚀剂,既能消除背面研磨损伤,又能修复芯片微裂与凹槽,大幅提升芯片抗碎裂性能。

关于粗磨/精磨减薄砂轮以及半切/全切金刚石刀片产品应用,欢迎咨询西斯特科技。

-

晶圆

+关注

关注

53文章

5181浏览量

130108 -

封装

+关注

关注

128文章

8741浏览量

145732 -

半导体制造

+关注

关注

8文章

450浏览量

24880

发布评论请先 登录

宜特晶圆:成功开发晶圆减薄达1.5mil(38um)技术

单面晶圆减薄和处理研究报告

用于高密度晶圆互连的微加工晶圆减薄方法

晶圆减薄工艺的主要步骤

减薄对后续晶圆划切的影响

减薄对后续晶圆划切的影响

评论