概述

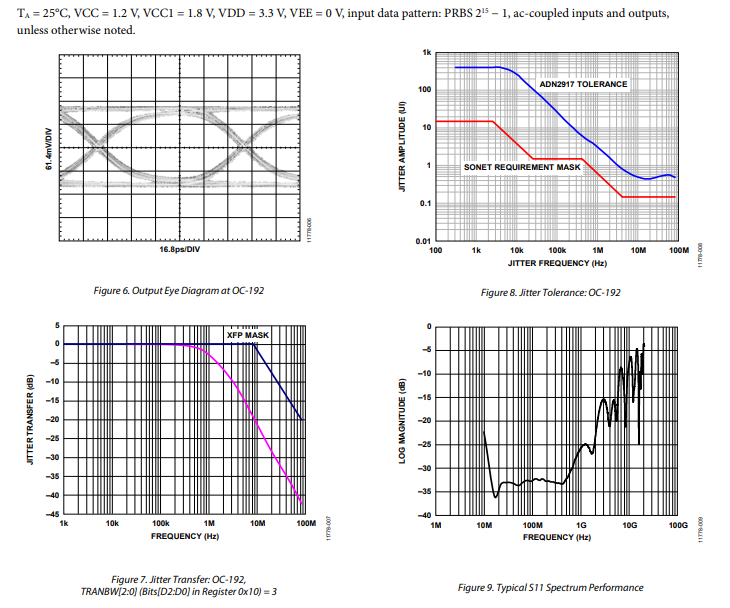

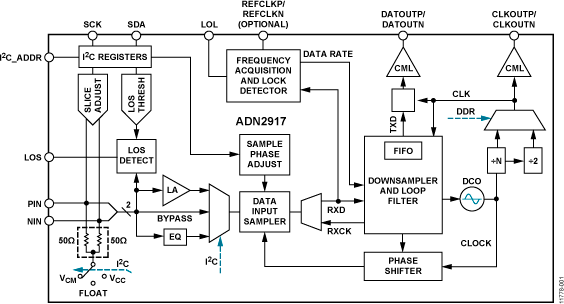

ADN2917可提供下列接收器功能:量化、信号电平检测、时钟和数据恢复,适用于从8.5 Gbps到11.3 Gbps的连续数据速率。它可自动锁定至所有数据速率,而无需外部参考时钟或编程。ADN2917抖动性能超越全部SONET/SDH抖动要求,包括抖动传递、抖动产生和抖动容差。

数据表:*附件:ADN2917连续速率8.5 Gbps至11.3 Gbps时钟和数据恢复IC,集成限幅放大器 均衡器技术手册.pdf

ADN2917提供手动或自动限幅调整和手动采样相位调整。此外,用户还可选择在输入端连接一个限幅放大器或均衡器。均衡器为自适应或可手动设置。

当输入信号电平降至用户可编程阈值以下时,接收器前端信号丢失(LOS)检测电路会予以提示。LOS检测电路具有迟滞特性,可防止LOS输出震颤。此外,可通过I2C寄存器读取输入信号强度。

ADN2917还支持伪随机二进制序列(PRBS)生成、位错误检测和输入数据速率回读功能。

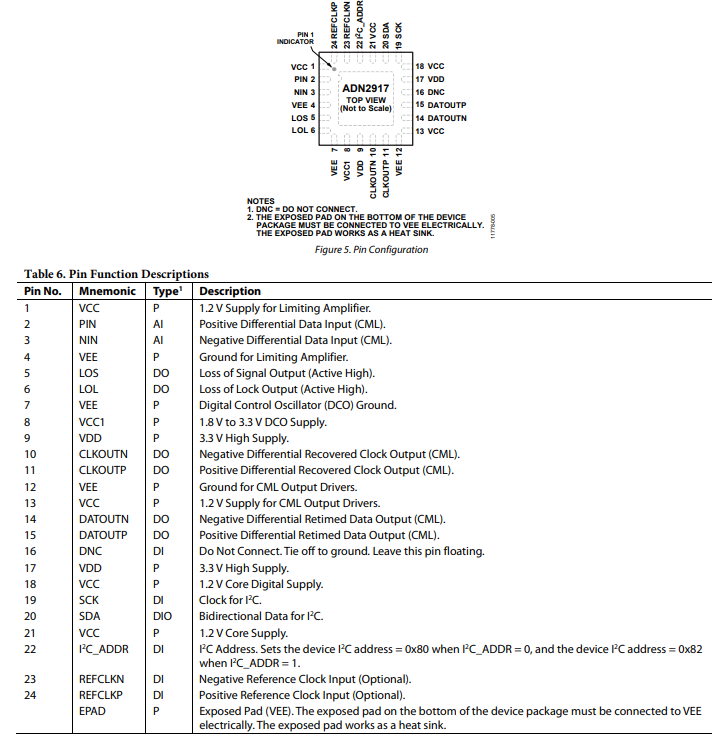

ADN2917采用紧凑型4 mm x 4 mm、24引脚架构芯片级(LFCSP)封装。除非另有说明,否则所有规格均相对于?40 ℃至+85 ℃环境温度而言。

应用

- SONET/SDH OC-192、10GFC、10GE及所有相关的FEC

- XFP、线路卡、时钟、路由器、中继器、仪器仪表

- 所有速率再生器/中继器

特性 - 串行数据输入:8.5 Gbps至11.3 Gbps

- 无需参考时钟

- 超过SONET/SDH抖动传递/产生/容差要求

- 量化器灵敏度:9.2 mV p-p(典型值,限幅放大器模式)

- 可选限幅放大器和均衡器输入

- 可编程抖动传递带宽,支持G.8251 OTN

- 可编程限幅电平

- 采样相位调整

- 输出极性反转

- 通过I2C可编程LOS阈值

- 通过I2C访问可选特性

- LOS报警(仅限幅放大器模式)

- LOL指示器

- PRBS发生器/检测器

- 应用敏感的功耗调整

- 352 mW(8.5 Gbps、均衡器模式、无时钟输出)

- 430 mW(11.3 Gbps、均衡器模式、无时钟输出)

- 电源:1.2 V、灵活的1.8 V至3.3 V范围及3.3 V

- 4 mm × 4 mm、24引脚LFCSP封装

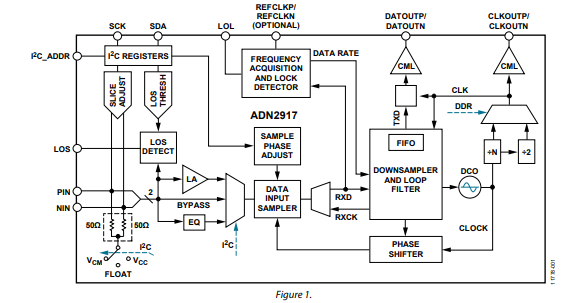

框图

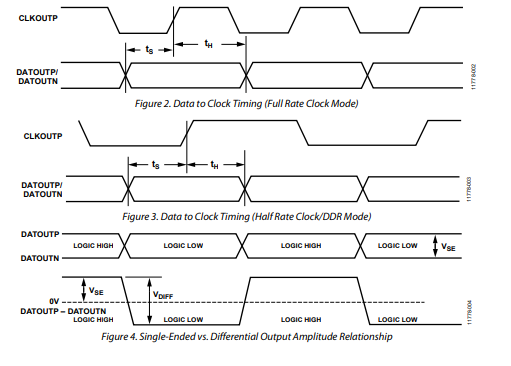

时序图

引脚配置描述

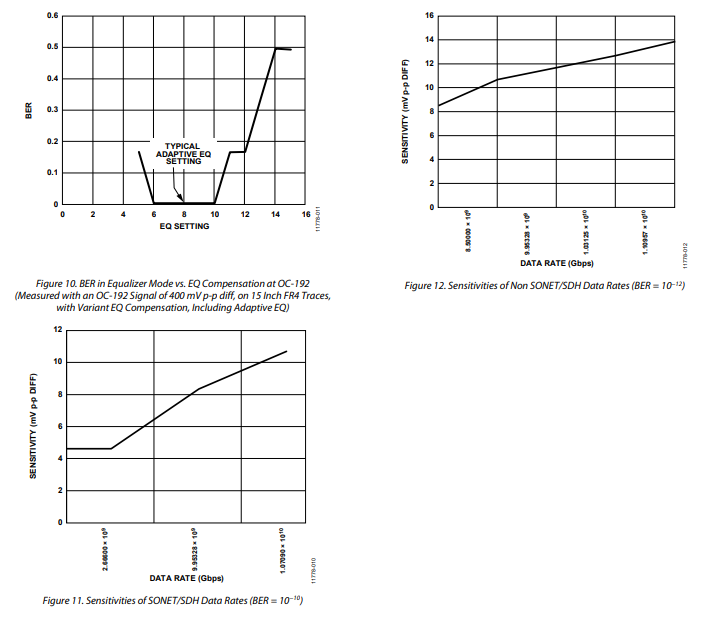

典型性能特征

ADN2917 实现了数据速率在 8.5 Gbps 至 11.3 Gbps 之间的时钟和数据恢复功能。前端可进行配置,既能放大非归零(NRZ)输入波形以实现全比例数字逻辑电平,也能对其进行处理。

为处理高速输入数据,用户可选择以下两种方式:一是具有高达 10 dB 增益灵敏度的高增益限幅放大器;二是在 5 GHz 时提升高达 10 dB、灵敏度为 600 mV 的高通无源均衡器。

片上的信号丢失(LOS)检测器与高灵敏度限幅放大器协同工作。LOS 的默认阈值为器件的灵敏度,最大阈值电平为 128 mV 峰峰值。限幅放大器还具备斜率阈值,可由用户通过 I^{2}C 设置,或根据最佳眼图张开度进行调整。

当输入信号因 FR - 4 或印刷电路板(PCB)走线中的其他损伤而受损时,可使用无源均衡器。均衡器的高频增益可通过 I^{2}C 寄存器进行配置,以替代出厂默认设置。此外,还具备用户可启用的自适应功能,该功能可自动调整以实现最宽的眼图张开度。均衡器可针对 8.5 Gbps 至 11.3 Gbps 之间的任何数据速率进行手动设置。

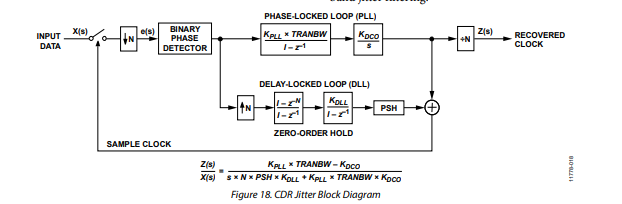

当有信号用于时钟和数据恢复(CDR)时,ADN2917 采用延迟锁定环和锁相环(PLL)电路进行时钟恢复和数据重定时,使其与来自 NRZ 编码数据的数据流同步。输入数据由高速时钟采样,数字下采样器可适应跨越三个数量级的数据速率。下采样数据被输入到二进制鉴相器中。

输入数据的相位由两条独立的反馈回路跟踪。一条高速延迟锁定环(DLL)路径通过数字控制振荡器(DCO)级联一个数字积分器,以跟踪抖动的高频分量。另一条独立的锁相环,由数字积分器和 DCO 组成,用于跟踪抖动的低频分量。DCO 的初始频率由第三环路设置,该环路将 DCO 频率与输入数据频率进行比较。此第三环路还确定数字下采样器的抽取率。

延迟锁定环(DLL)和锁相环(PLL)共同跟踪输入数据的相位。例如,当时钟滞后于输入数据时,鉴相器会将 DCO 驱动到更高频率,并通过移相器将时钟相位推进;这两种操作都能减小时钟与数据之间的相位误差。由于环路滤波器是一个积分器,静态相位误差会被驱动至零。

从另一个角度来看,该电路中的移相器实现了频率补偿的二阶锁相环所需的零值,且零值位于反馈路径中,因此在闭环传递函数中不会出现。由于该电路在闭环传递函数中没有零值,所以消除了抖动峰值。

延迟锁定环和锁相环同时提供宽带抖动适应和窄带抖动滤波功能。图 18 中的简化框图显示,Z(s)/X(s) 是一个二阶低通抖动传递函数,具有出色的滤波性能。低通频率极点是通过在 DLL 中对 PLL 的增益进行分频形成的,其增益在转换带宽内接近 N。请注意,该抖动传递函数没有零点,与普通的二阶锁相环不同。这意味着主 PLL 没有抖动峰值,这种无抖动峰值的特性为信号发生器应用提供了理想的性能,因为在级联发生器中,抖动峰值可能会导致危险的抖动累积。

误差传递函数 e(s)/X(s) 与带有二进制鉴相器的普通锁相环具有相同的高通形式,该传递函数可自由优化,以提供出色的宽带抖动适应功能,因为抖动传递函数 Z(s)/X(s) 提供了窄带抖动滤波功能。

-

均衡器

+关注

关注

9文章

225浏览量

31183 -

时钟

+关注

关注

11文章

1908浏览量

133456 -

数据恢复

+关注

关注

10文章

658浏览量

18259

发布评论请先 登录

请问ADN2917采样信号量化应该怎样使用

EVALZ-ADN2905/EVALZ-ADN2913/EVALZ-ADN2915/EVALZ-ADN2917用户指南

ADN2917 连续速率8.5 Gbps 至11.3 Gbps 时钟和数据恢复IC,集成限幅放大器/均衡器

ADN2917:连续速率8.5 Gbps 至11.3 Gbps 时钟和数据恢复IC,集成限幅放大器/均衡器

ADN2812:连续速率12.3 Mb/s至2.7 Gb/s时钟和数据恢复IC,带集成限幅放大器数据表

ADN2814:连续速率10 Mb/s至675 Mb/s时钟和数据恢复IC,带集成限幅放大器数据表

ADN2813:连续速率10 Mb/s至1.25 Gb/s时钟和数据恢复IC,带集成限幅放大器数据表

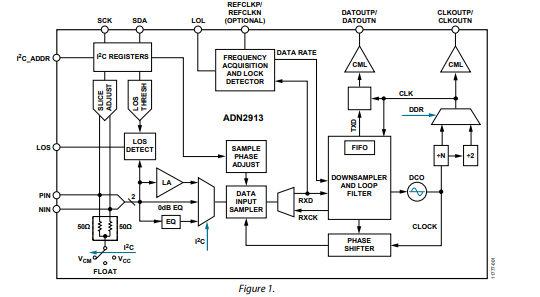

ADN2913:连续速率6.5 Mbps至8.5 Gbps时钟和数据恢复IC,集成限幅放大器/均衡器数据表

ADN2817/ADN2818:连续速率10 Mbps至2.7 Gbps时钟和数据恢复IC数据表

ADN2913连续速率6.5 Mbps至8.5 Gbps时钟和数据恢复IC,集成限幅放大器/均衡器技术手册

ADN2917连续速率8.5 Gbps至11.3 Gbps时钟和数据恢复IC,集成限幅放大器/均衡器技术手册

ADN2917连续速率8.5 Gbps至11.3 Gbps时钟和数据恢复IC,集成限幅放大器/均衡器技术手册

评论