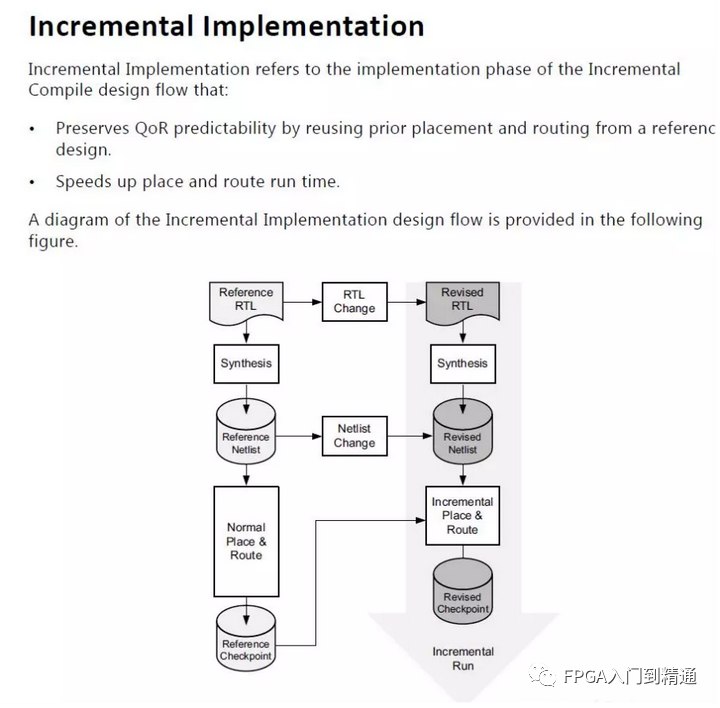

Incremental Compile增量编译是Vivado提供的一项高阶功能。目的旨在当设计微小的改变时,重用综合和布局布线的结果,缩短编译时间。

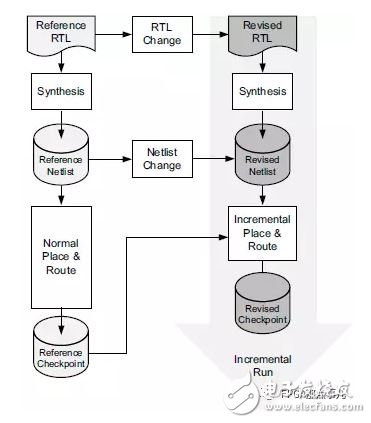

下图是增量编译的流程:

增量编译需要已经编译完成的原始设计的dcp文件作为参考,当我们在原始设计上做微小的改动时,就可以使用增量编译的流程。这些改动包括:

- RTL代码的微小修改

- 网表的微小修改,比如增加或者改变ILA

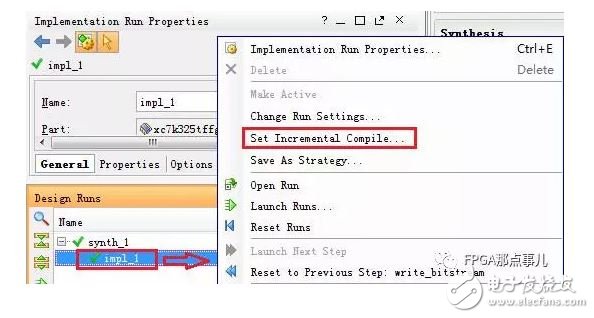

在Vivado里面,使能IncrementalCompile的方式非常简洁,在Impl run上右键选择“Set Incremental Compile…”,然后设置相应的参考dcp文件即可:

Tips:

1. 当参考设计和当前设计的相似度大于95%的时候,最适合用增量编译技术

相似度低于75%时,工具会关闭增量编译

2. 有些时候,即使很小的RTL改动,也会造成网表的巨大差异。比如

a) 改变HDL中的某些全局常量

b) 增加总线的位宽

-

Vivado

+关注

关注

19文章

835浏览量

69158

发布评论请先 登录

Altium如何放置compile mask(编译屏蔽)

谁能缩短大容量FPGA的编译时间?增量式编译QIC!

Vivado Design Suite 2015.3的新功能介绍

Vivado Design Suite 2015.3新增量编译功能介绍

Vivado综合引擎的增量综合流程

Vivadoz中增量编译与设计锁定

Vivado增量编译的基本概念、优点、使用方法以及注意事项

Xilinx Vivado使用增量实现

Vivado中的Incremental Compile增量编译技术详解

Vivado中的Incremental Compile增量编译技术详解

评论