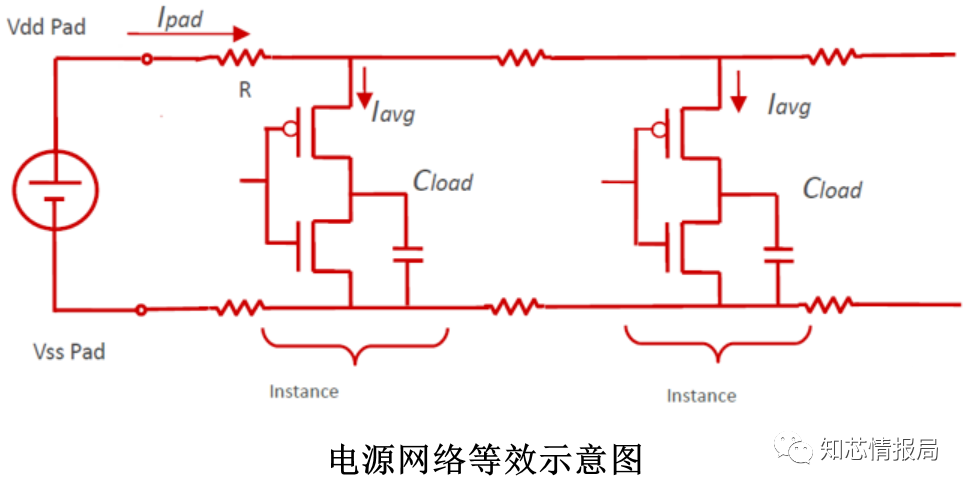

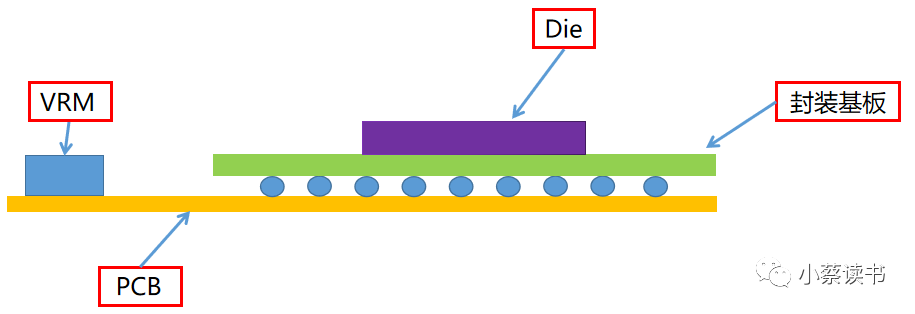

IR Drop仿真是一个系统层面的问题,需要考虑完整的Power Distribution System(PDS)链路上所有压降,并以此来优化每颗器件所接收到的供电电压。

在设计设计中所有的电源供电芯片在相应的设计下都有一个标称的输出电压与电压波动范围(可能是由于芯片本身或所用分压电阻误差造成)。每颗SINK芯片也有标称的正常工作的电压与上下容限范围。我们需要根据这些给定条件结合PowerDC仿真结果来判断PDS设计是否符合要求。

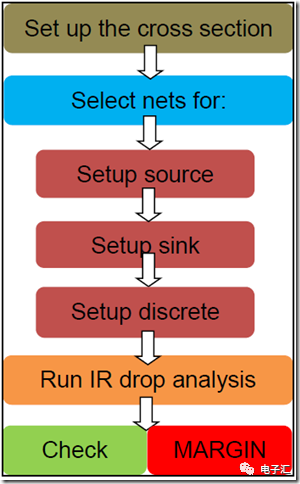

典型的PowerDC仿真流程:

案例1:实际电压低于正常额定电压

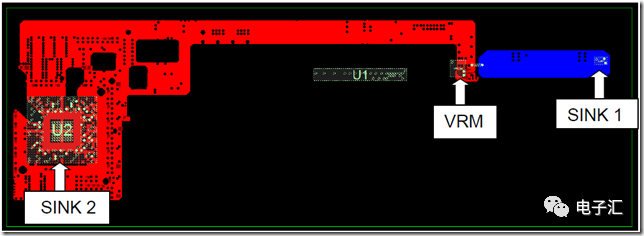

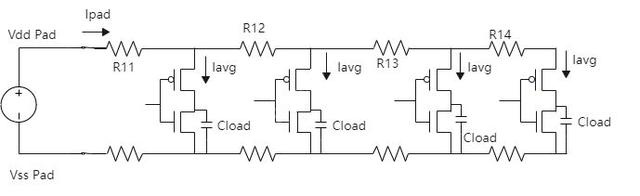

如下图所示的一个PCB板,一个VRM同时给两个SINK供电,SINK1通过一个被动元件(如磁珠或电阻等)与VRM连接,SINK2直接通过PCB敷铜与VRM连接。假设VRM输出电压为1.5V,输出容限为0%,SINK1和SINK2额定供电电压为1.5V, 容限为1%,供电电流分别为5A和0.2A。

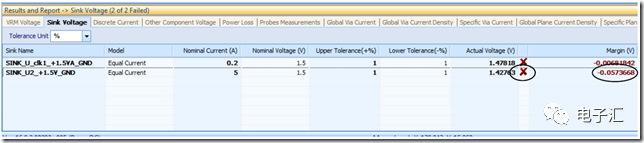

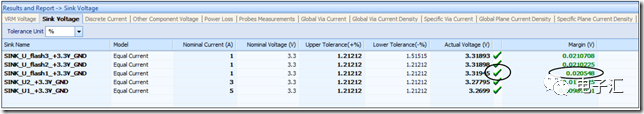

PowerDC的仿真结果如下图所示,SINK1和SINK2结果都为FAIL。那么PowerDC软件是如何计算Margin值的呢?

当实际电压低于正常额定电压时,Margin通过下面公式计算:

Margin = (Actual voltage + SinkLowerTolerance) – (Normal voltage + VRMoutputTolerance)

因此以U2为例计算得到U2的Margin为:

U2_margin = [1.42763 + (1.5 * 1%)] – [1.5 + (1.5*0%)]

= 1.44263 – 1.5 = –0.05737V

当Margin为负时则说明IR Drop仿真结果Fail, 在PowerDC报告中会出现一个红色的叉叉。

案例2:实际电压高于正常额定电压

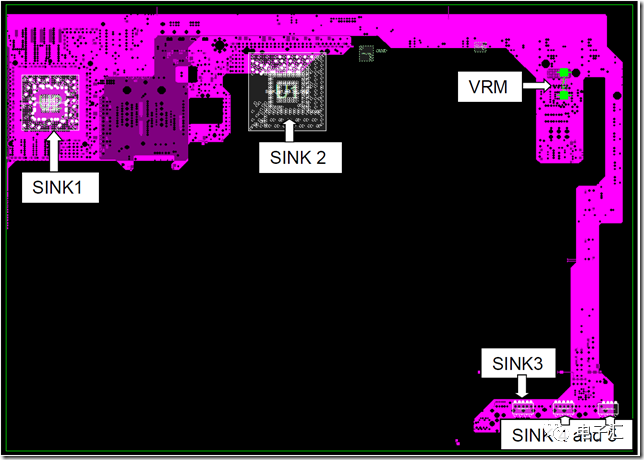

假设有一个PCB设计如下图所示, 包含一个VRM和4个SINK芯片,VRM与SINK的设计参数见下图仿真结果表格所设。

PowerDC最终的仿真结果显示所有SINK的IR Drop仿真结果都PASS,那这些Margin值又是如何计算出来的呢?

当实际电压高于正常额定电压时,Margin通过下面公式计算:

Margin = (Normal voltage + SinkUpperTolerance) – (Actual voltage + VRMoutputTolerance)

因此以SINK_U_flash1为例计算得到SINK_U_flash1的Margin为:

SINK_U_flash1_margin = [3.3 + (3.3 * 1.2121%)] – [3.31945 + (3.3*0%)]

= 3.33999996 – 3.31945 = 0.020548V

当Margin为负时则说明IR Drop仿真结果Pass, 在PowerDC报告中会出现一个绿色的勾。

审核编辑:汤梓红

-

PCB板

+关注

关注

27文章

1480浏览量

53723 -

仿真

+关注

关注

52文章

4315浏览量

136243 -

PCB设计

+关注

关注

396文章

4827浏览量

91193 -

DC

+关注

关注

10文章

3685浏览量

682992 -

电源供电

+关注

关注

0文章

173浏览量

22519

原文标题:Sigrity PowerDC是如何计算IR Drop Margin?

文章出处:【微信号:电子汇,微信公众号:电子汇】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

谈谈芯片设计中的IR-drop

什么是DC IR Drop?DC IR Drop仿真有何意义?

Cadence Sigrity PowerDC应用程序的用户手册资料免费下载

PowerDC直流仿真操作说明详细概述

电源完整性之Cadence Sigrity Power DC_IR_Drop仿真

IR Drop对芯片性能及功能的影响

IR Drop与封装分析

IR Drop对芯片性能及功能的影响

IR Drop与封装(一)

技术资讯 | PowerDC直流压降分析

2022 Sigrity Aurora SPB 17.4 版本更新 I IR Drop 直流电压降仿真支持自动剪切功能

缓解高性能存算一体芯片IR-drop问题的软硬件协同设计

Sigrity PowerDC是如何计算IR Drop Margin?

Sigrity PowerDC是如何计算IR Drop Margin?

评论