三星电子晶圆代工事业部在国际互连技术大会(IITC, International Interconnect Technology Conference)上发表了一篇主题为“EUV Minimum Pitch Single Patterning(EUV单图案最小节距)”的论文。我们为此特别准备了这篇博文,希望将论文内容和EUV(极紫光外刻)技术的特点分享给更多人。

1. 用更细的笔即可画出更细的线!

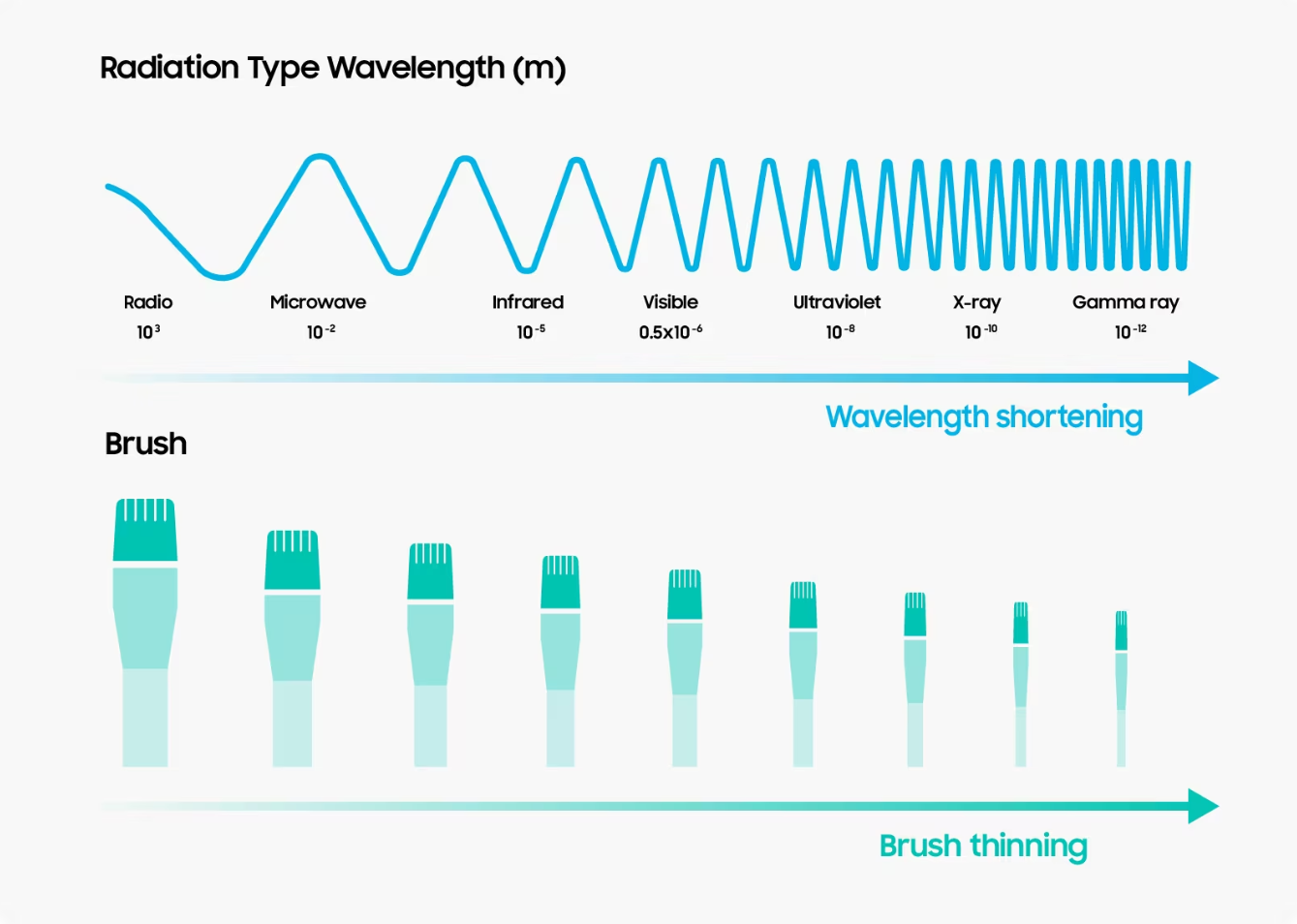

在上一篇博文中,我们了解了光刻技术(Photolithography)所面临的阻碍,并在文章结尾处提到了如何从根本上解决光的性质带来的局限性,即缩短波长,因为不同的波长会带来不同程度的衍射现象。而短波长,能够缩小衍射的扩散角度,最终克服光刻工艺的局限性。如图[1]所示,正如想要画出细线就需要细毛笔一样,想要突破绘制的局限,用波长更短的光即可。

图[1] 波长 (Wavelength) 变短类似于画图的毛笔变细。

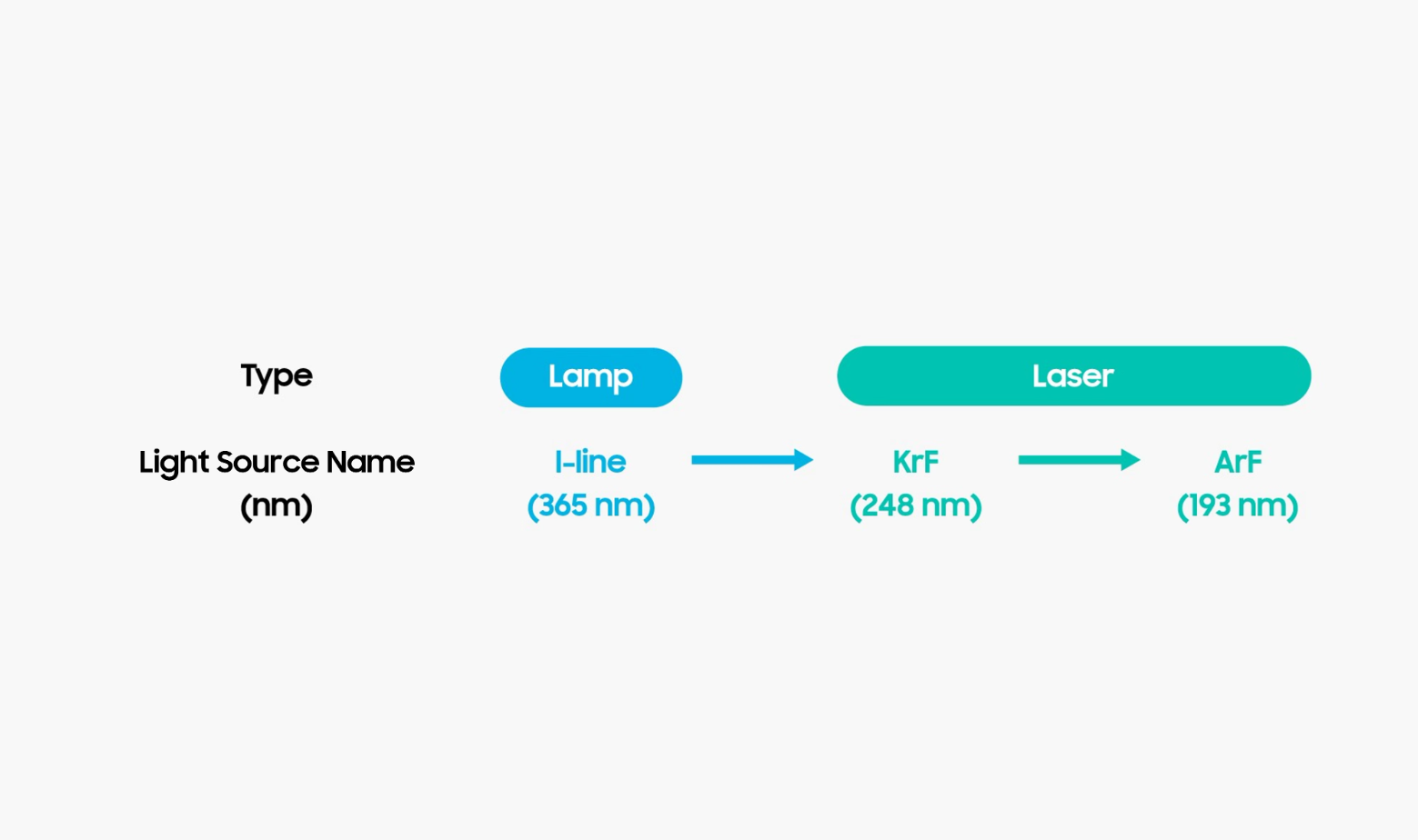

因此,如图[2]所示,为了绘制更小的图案,光刻工艺经历了绘制所用光的波长逐渐变短的发展历程。

图[2] 大体来说,光刻工艺使用的光从灯泡光照变为了激光。具体到激光,则是从利用 Kr(氪,Krypton)的 KrF (氟化氪)激光发展到利用 Ar(氩,Argon)的 ArF (氟化氩)激光来改变光源,达到缩短波长的目的。

然而,为了满足制作更小晶体管的需求,ArF (193 nm) 的波长也不够短。于是,EUV (极紫光,Extreme Ultra Violet) 应运而生了。

2. EUV (极紫光,Extreme Ultra Violet) 的出师表

为了打破波长的局限性,EUV 解决方案如同彗星一般登场!

EUV 最大的特点就是波长短。为了达到精密绘制的目的,我们需要短的波长,从而需要引入 EUV。

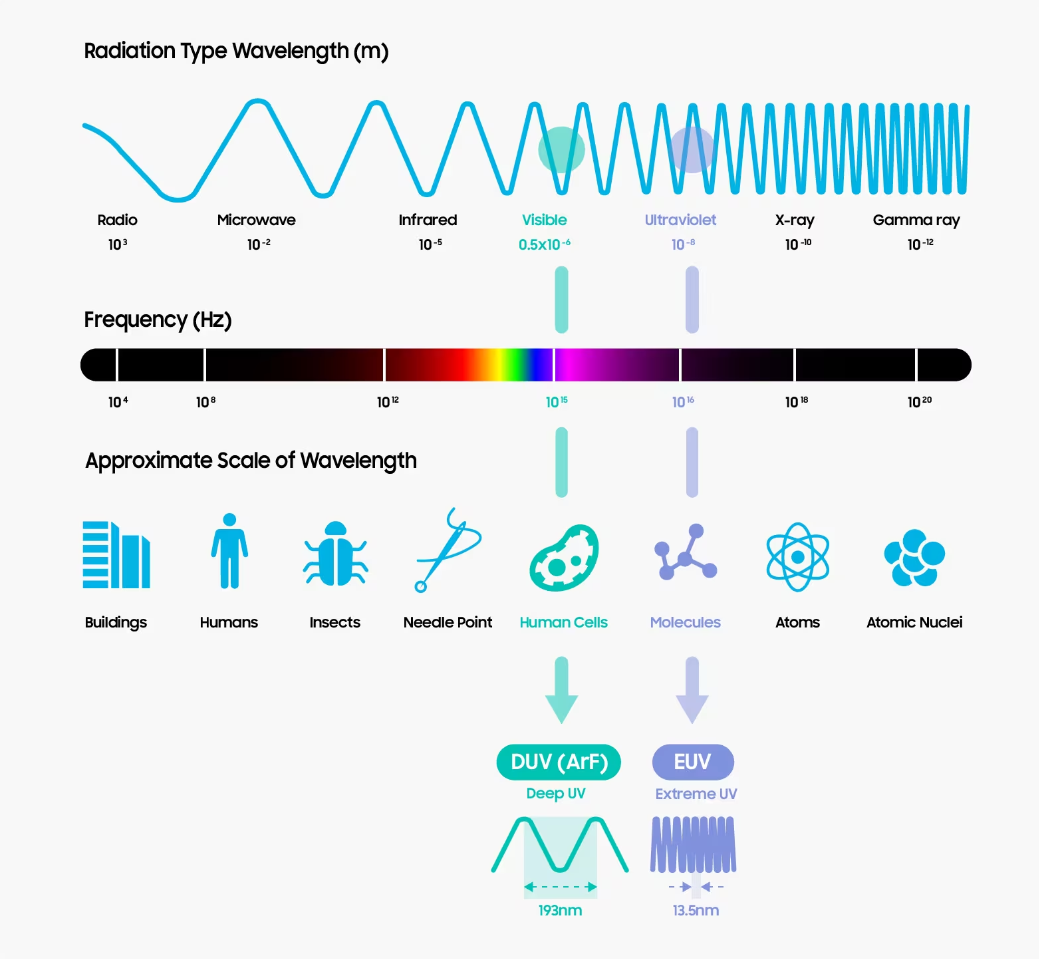

正如图[3]所示,我们使用的是波长极短的 EUV,只有 13.5 nm。

图[3] 将波长与我们所熟知物体的大小进行类比。先前使用的 ArF 是波长为 193 nm的一种 DUV (深紫外光,Deep UV),而波长为 13.5 nm的 EUV 甚至比分子更小。

先前使用的 ArF 的波长为 193 nm,而 EVU 的波长仅为 13.5 nm,就波长的差异而言,EUV 本身可以说是一个巨大的变化。那么,光刻工艺在应用了这一巨大变化的主角 EUV 之后,又具备了什么特点呢?让我们来仔细了解一下。

A. 强大的等离子体发出的短波

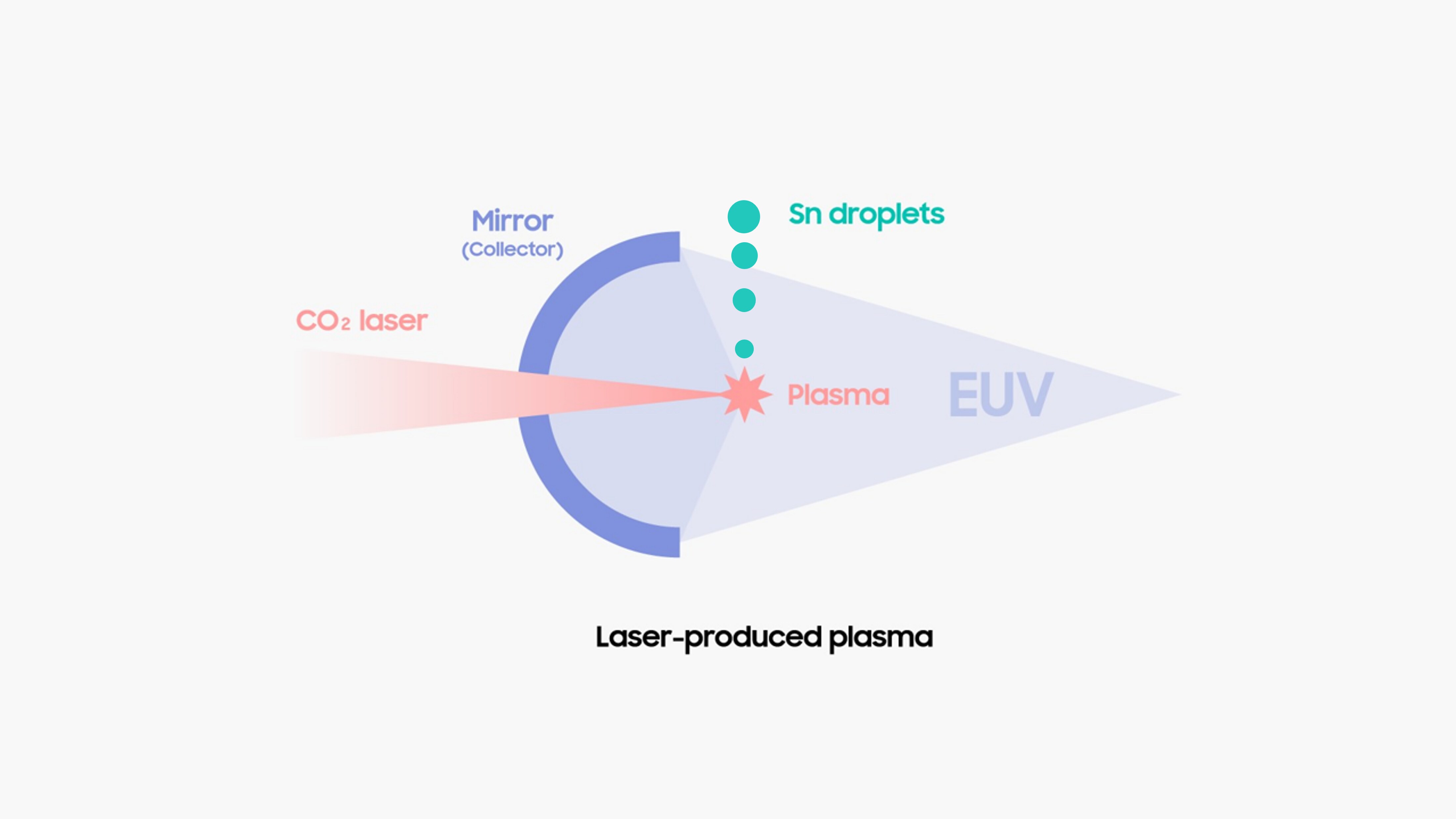

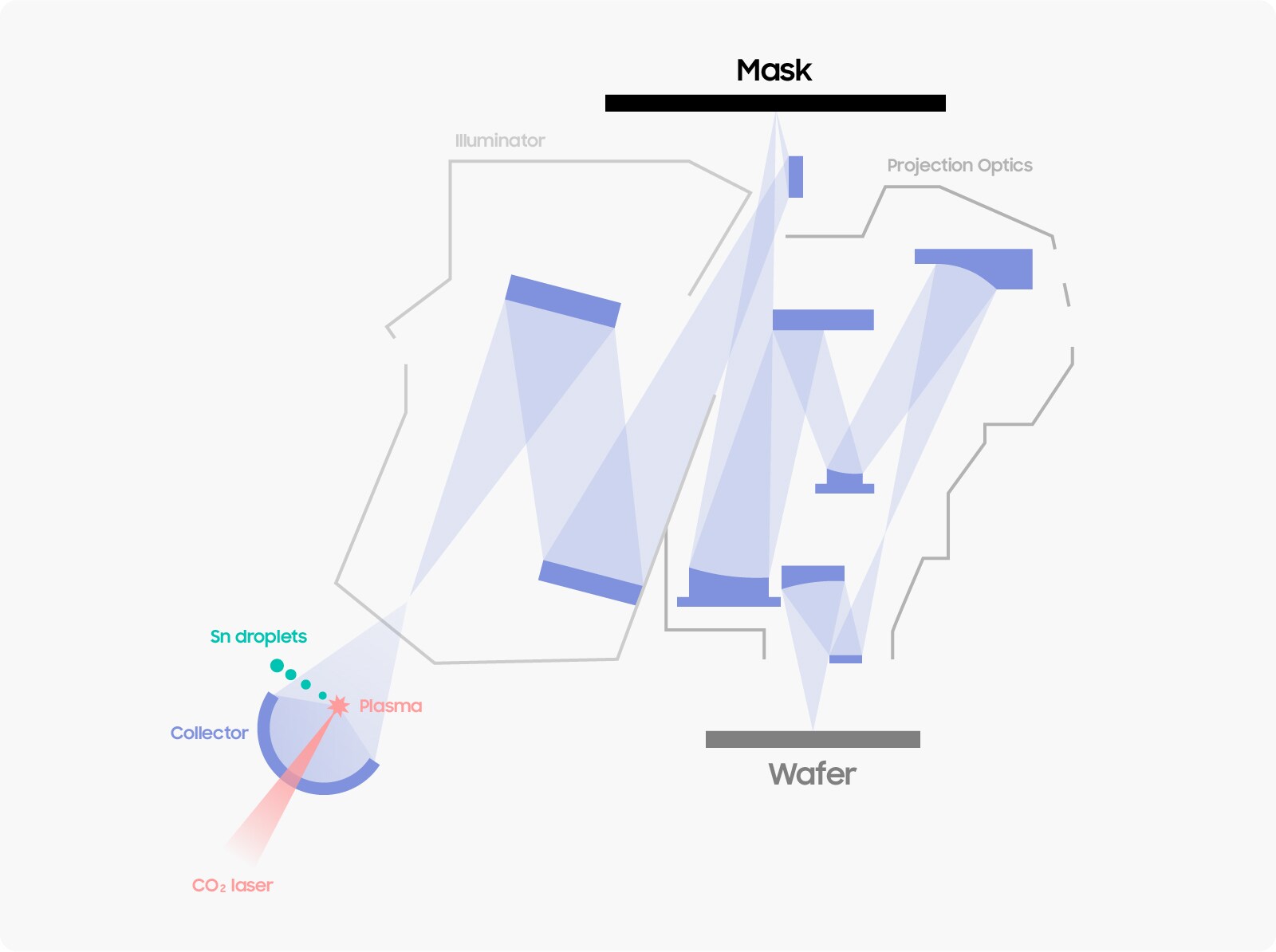

在上方的图[3]中,可以看到组成彩虹颜色的光的范围。按照波长由长到短的顺序,依次罗列了能够烧伤人们皮肤的紫外线、可穿透肌肉的 X 射线,还有强大到能够杀死癌细胞的伽玛射线。我们也可由此看出,波长越短的光,所蕴含的能量就越大。而相应地,在发射更短波长的光时,需要的能量也通常会更多。做个类比,想要打出全垒打,棒球就要飞得更远、更快,那么挥舞棒球棒的力度也要更大。然而,先前用于发射 DUV 光的激光,不具备足够的能量,无法发出我们所需的短波。因此,如图[4]所示,EUV 使用了处于极高能量状态的等离子体(Plasma),即气体被分离为电子和离子的状态,是固体、液体、气体之外的另外一种物质状态,具有很高的能量。

图[4] 让 CO2 激光(Laser)与掉落的 Sn(锡)准确碰撞来产生等离子体,并使用镜子将等离子体生成的光集合起来,最终产生 EUV。

如图[4]所示,产生 EUV 必须使用一种特制的工具:集合光的镜子! 镜子,不仅可用来产生 EUV,更是使用 EUV 的整个工艺流程中不可或缺的重要因素。下面就让我们来了解一下 EUV 技术中的核心要素:镜子。

B. 反射光学 - 使用镜子而非放大镜

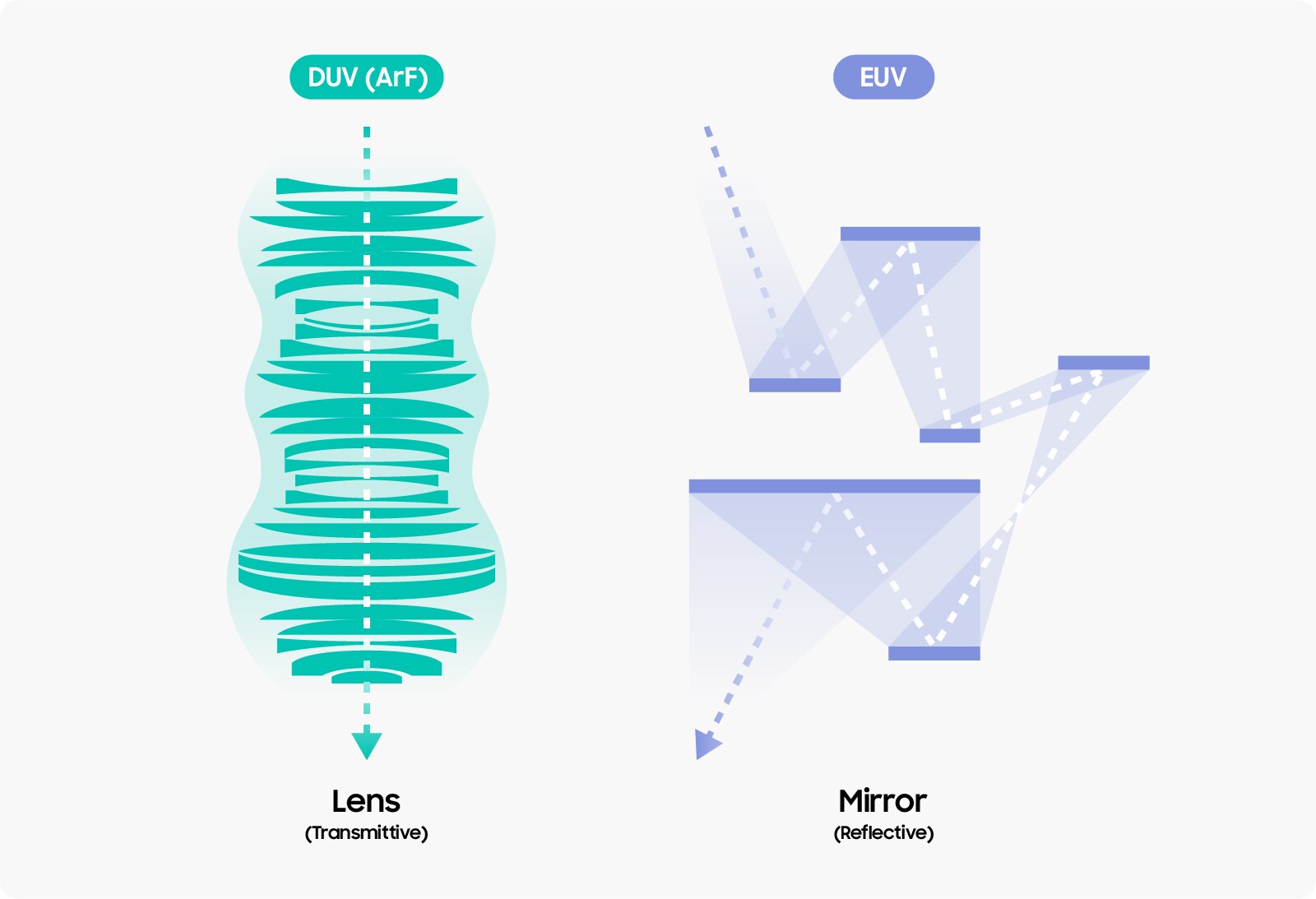

光的特点是波长越短,就越容易被其它物质吸收。EUV 的波长极短,甚至能被大气吸收。而为防止这种情况出现,EUV 设备(使用了 EUV 的光刻工艺设备)在工序开始前,先将内部进行了真空处理。在操作 EUV 工艺时使用镜子,也是为了减少光被吸收的类似情况:假如让波长极短的 EUV 通过透镜,则会被透镜大量吸收。因此,通过用镜子替代先前的透镜,让光进行反射而非透射,则可以减少吸收量。只有极大降低吸收量从而让光像图[5]一样安全地到达光刻胶,才能进行完整的绘制。

图[5] 直到 DUV,光刻技术都一直在使用透镜,而 EUV 波长较短,使用透镜会加大吸收率。为改善这一问题,我们使用了吸收率相对较低的反射模式,即通过镜子来实现。

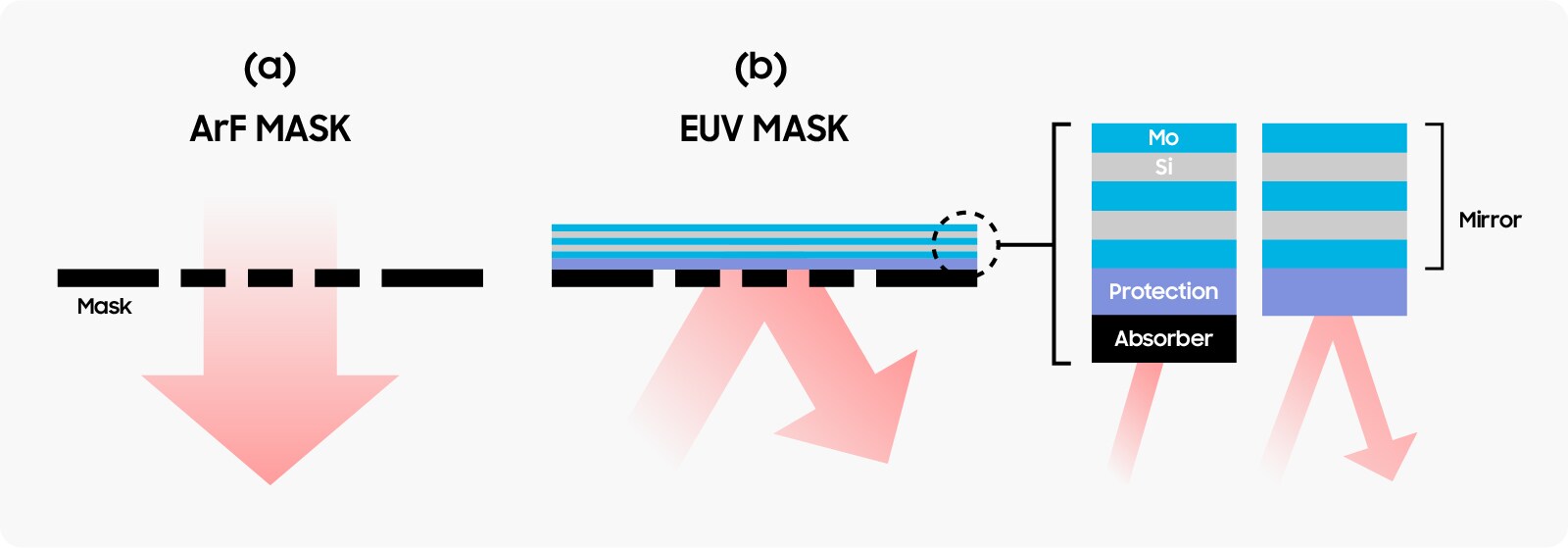

讲到这里,大家可能会产生一个疑问。用来透射光的掩膜怎么办? 利用 EUV 的光刻工艺中所用的掩膜同样是运用反射原理制成的。如图[6]所示,将原本(a)形式,遮挡和透射光的掩膜,换成像 (b) 形式,反射和吸收光的掩膜。

图[6] 为了尽可能降低吸收率,EUV 掩膜使用了 Mo(钼)和 Si(硅)多层叠加结构的反射镜,并通过充当保护膜角色的保护层(Protection)来保护镜子。不应出现反射现象的区域,则使用吸收层(Absorber)(TaN)来吸收光。

通过图[7],可以直观地了解以上关于 EUV 光刻工艺的解释。

图[7] 展示了 EUV 光刻工艺的整个曝光(向晶片上照射光的)过程。

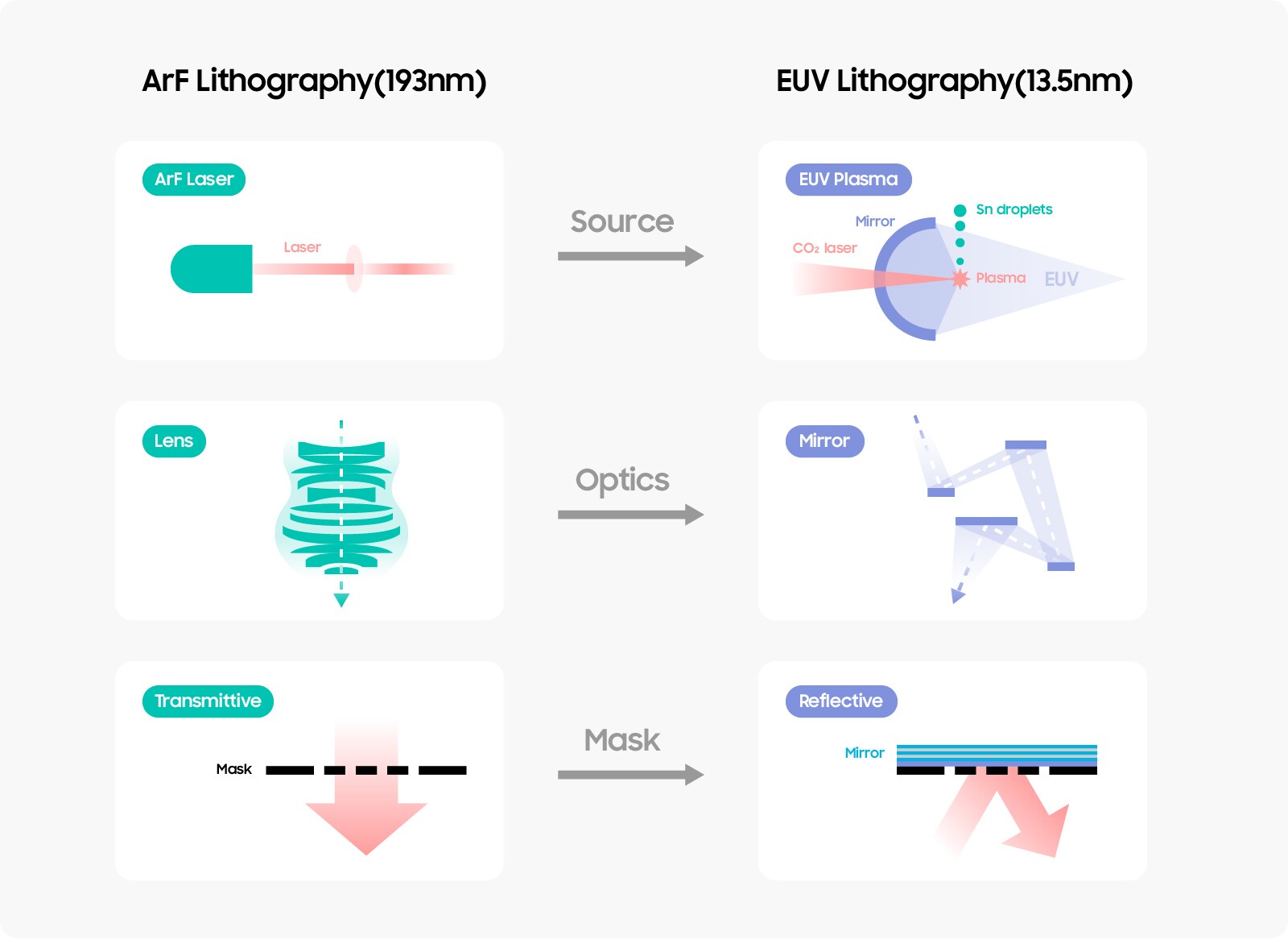

下面再对 EUV 和 ArF 进行简单的比较,对比内容如图[8]所示。

图[8] ArF 光刻工艺利用激光产生光,并使用透镜(Lens)和透射型(Transmittive)掩膜。EUV 则与之不同,它利用等离子体产生光,并使用镜子 (Mirror) 和反射型(Reflective)掩膜。

如图[8]所示,EUV 光刻工艺与先前的工艺完全不同,可以画出之前无法画出的更小图案。然而, EUV 的优势,并不仅仅在于能够画出更小的图案。

3. 画出以前难以实现的图案,省去反复绘制的麻烦,一次搞定!

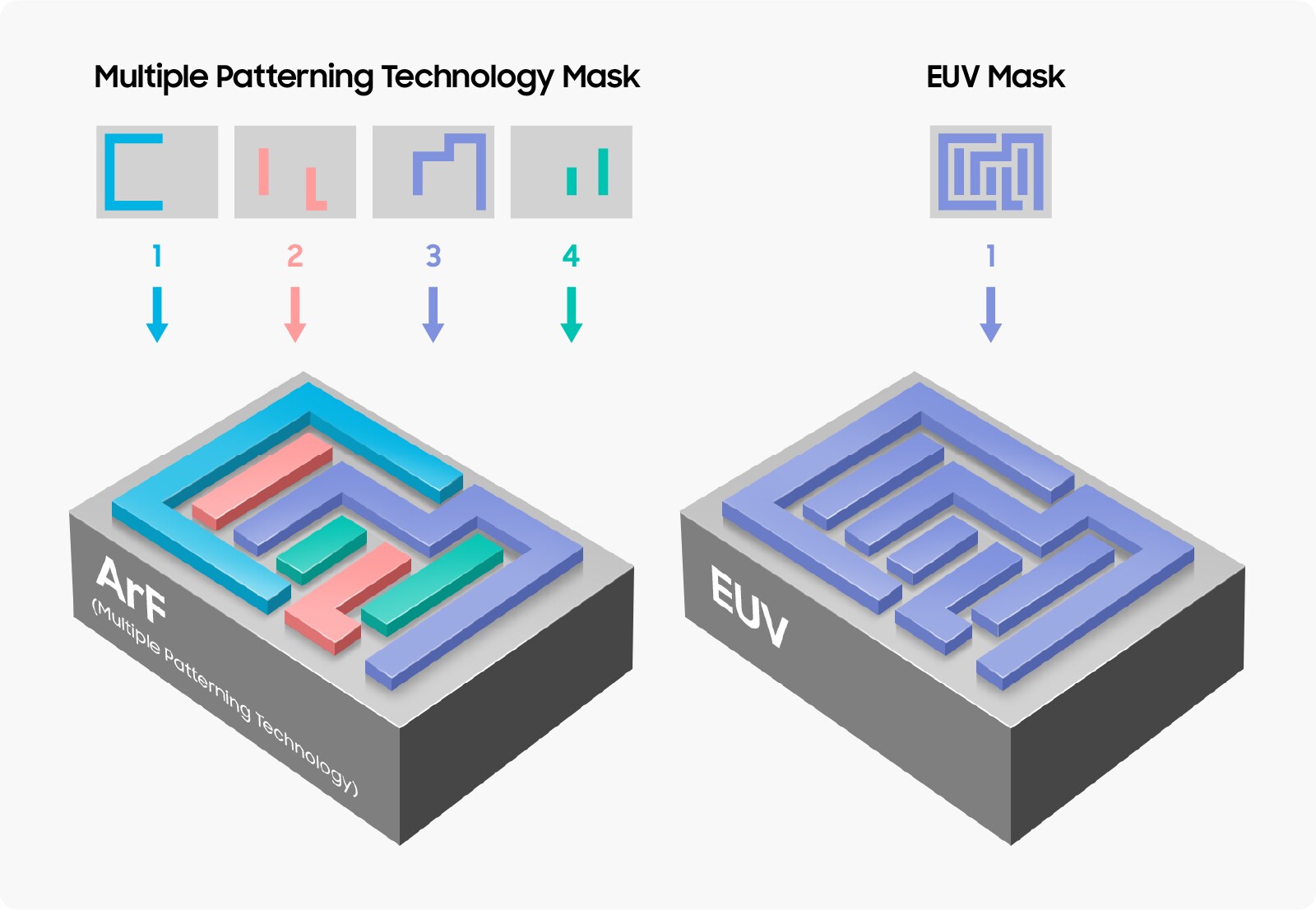

在前面的第一章博文中,我们介绍到,为了打破波长的局限性,一个图案不得不分成几次进行绘制。这就是 MPT (多重图案技术,Multiple Patterning Technology)。MPT 技术虽然具有绘制小图案的优势,但如图[9](a)所示,它的缺点是需要多个掩膜,而且需要进行多次工序操作。然而使用波长较短的 EUV 时,就可以像图[9](b)一样,仅通过一个掩膜和一次工序,便绘制出图案。

图[9] 使用四个相同掩膜进行绘制的 ArF 和仅使用一个掩膜进行绘制的 EUV。

这种改进具有时间、良率和费用上的优势。

A. 时间 - 缩短了工序时间

在获取结果的过程中,如果步骤增多,相应地,耗时也会变长。举个简单的例子来说明,图[9]的(a)工厂做出一个面包需要四个小时,(b)工厂做一个面包则只需要一个小时。这是因为步骤的精简大大提升了工序的速度。

B. 良率 - 降低污染,提高良率

多个步骤,就意味着相应存在多次污染的可能。比如白色黏土,反复揉捏,就容易变脏。在半导体工艺中,污染是导致良率降低的原因,而 EUV 可减少污染,从而起到提高良率的作用。

C. 费用 - 降低掩膜制作成本

制作掩膜也需要成本。原本的工艺需要制作多张掩膜,但使用 EUV 后,所需的掩膜会减少到一张,制作成本也相应减少。

4. 工欲善其事,必先利其器

如上所述,EUV 的出现给光刻工艺带来了很大优势,如今我们要做的,就是努力去探索如何才能更加有效地利用这一利器。

审核编辑黄宇

-

晶圆

+关注

关注

53文章

5212浏览量

130287 -

光刻

+关注

关注

8文章

350浏览量

30754 -

EUV

+关注

关注

8文章

610浏览量

87467

发布评论请先 登录

什么是晶圆级扇入封装技术

签约顶级封装厂,普莱信巨量转移技术掀起晶圆级封装和板级封装的技术革命

在毫米级晶圆上,绘制纳米级图案

在毫米级晶圆上,绘制纳米级图案

评论