ز رش

µ¹×°جص´ةاٍص¤صَءذ£¨FC-CBGA:Flip Chip Ceramic Ball Grid Array£©·â×°¼¼تُتاIBM¹«ث¾؟ھ·¢µؤز»ضض¼¼تُ£¬ئن²ةسأ¸كبغµم90Pb-10Sn؛د½ًضئ×÷؛¸ءداٍ£¬ح¨¹µحبغµم¹²¾§؛¸ءد63Sn/37Pbء¬½سµ½·â×°جه¼°؛َذّµؤPCB°هةد£غ1£¬2£ف،£سةسع¸أ·â×°¾كسذسإذمµؤµçذشؤـ،¢ببذشؤـ؛ح؟ة؟؟ذش£¬زٍ¶ّئنس¦سأزرد൱¹م·؛،£

سةسعزµ½çب±·¦ح³ز»µؤ¹¤زµ±ê×¼£¬از³ِسع¼¼تُ±£أـ؛ح¾¼أ³ة±¾µؤ؟¼آا£¬ئ÷¼ةْ²ْ³§ةججل¹©µؤئ÷¼ؤع²؟ت¾ف؛حبب²خت·ا³£سذدق£¬ثو×إذ¾ئ¬µؤضئ³جش½ہ´ش½دب½ّ£¬ؤ؟ا°7 nm¹¤زصزر¾ء؟²ْ£¬ذ¾ئ¬µؤ¹¦آت؛ح¹¦آتأـ¶بش½ہ´ش½¸ك£¬زٍ´ث¶ش´ثہ൹װاٍص¤صَءذµؤدêد¸ببؤ£ذح½ّذذ·ضخِ±نµأت®·ض±طزھ،£

¹ْؤع¶شCBGA؛¸اٍ؟ة؟؟ذشµؤبب·ضخِرذ¾؟µأ½د¶à£¬µ«تا¶شصû¸ِ·â×°جه£¬سبئنتا·â×°جه±¾ةيµؤببضشرذ¾؟ب´؛ـةظ،£¸ك»شµب£غ3£ف¶ش¶àذ¾ئ¬جص´ة·â×°µؤ½ل-؟ابب×è·ضخِ·½·¨½ّذذءثرذ¾؟£¬رذ¾؟ءث¶àذ¾ئ¬ببٌî؛د¶شبب×èµؤس°دى£»Ravlµب£غ4£ف¶شFC-CBGA½ّذذءثرذ¾؟£¬·ضخِءثسذ¸ا°ه؛حخق¸ا°هµؤ·â×°،¢²»ح¬ذ¾ئ¬³ك´ç؛ح²»ح¬بب³ءجُ¼دآذ¾ئ¬½لµمسë»·¾³ض®¼نµؤبب×èRjaµؤ±ن»¯£¬²¢°´صصJEDEC±ê×¼½ّذذءثتµر飻ذ»ذم¾êµب£غ5£ف¶شآمذ¾ت½،¢ئ½°هت½؛ح¸ا°هت½3ضضذخت½،¢²»ح¬ذ¾ئ¬³ك´ç؛ح²»ح¬بَ»¬¼ء²ؤءد¶شدµح³بب×èµؤس°دى½ّذذءث·آصو·ضخِ£¬µ«تا¶¼أ»سذ¶شFC-CBGA½ل؟ابب×è½ّذذ·ضخِرذ¾؟،£

±¾خؤصë¶ش·ائّأـµ¹×°؛¸جص´ة·â×°£¬ؤâ²ةسأدض³ةµؤبب×è²âتشذ¾ئ¬ةè¼ئµنذحبب×è²âتشئ÷¼£¬ح¨¹سذدقشھ½¨ء¢بخ¬سذدقشھببؤ£ذح£¬·ضخِذ¾ئ¬³ك´ç،¢بب³ء؛حµ¼بب½؛²ؤءد¶شFC-CBGA½ل؟ابب×èµؤس°دى£¬ح¨¹¶شز»ضضµنذحئ÷¼µؤبب×è²âتشرéض¤ءث·آصو½ل¹ûµؤ×¼ب·ذش،£

1بب×è²âتشئ÷¼ةè¼ئ

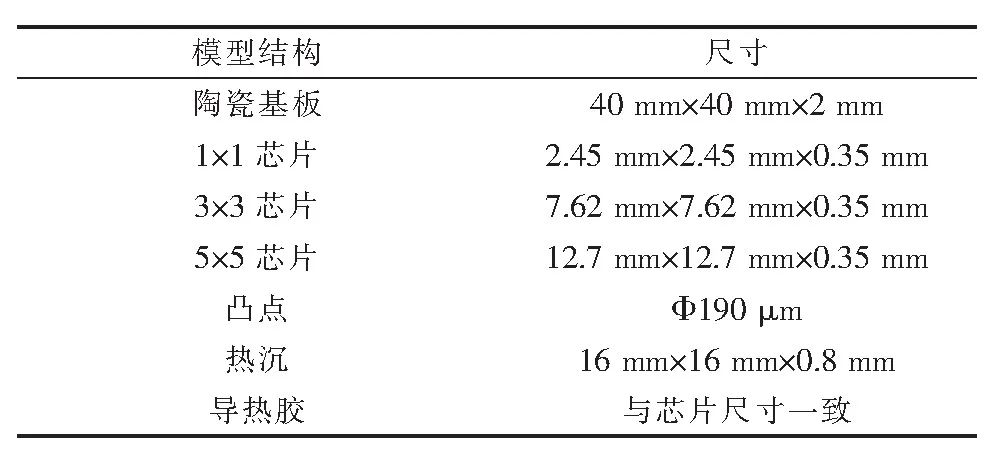

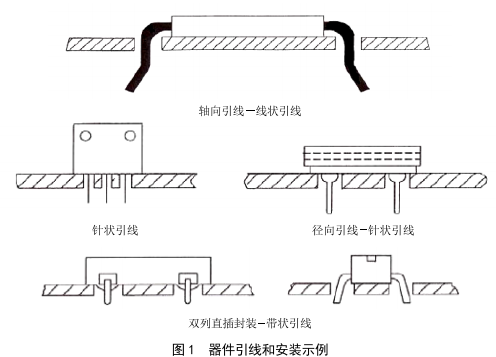

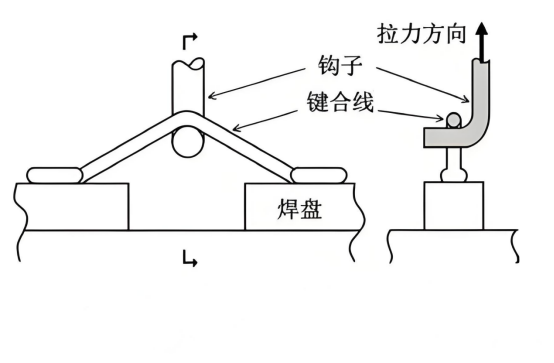

²ةسأµ¥شھ³ك´çخھ2.54 mm،ء2.54 mmµؤبب×è²âتشذ¾ئ¬£¨بçح¼1ثùت¾£©خھ»ù´،£¬؟¼آاجص´ة»ù°هµؤ¼س¹¤³ة±¾£¬²¢ح¬ت±¼و¹ثذ¾ئ¬³ك´ç،¢بب³ء¸ا°ه؛حµ¼بب½؛¶ش½ل؟ابب×èµؤ²âتشرذ¾؟£¬¶¨ضئءثز»؟îؤـ¹»¼وبف1،ء1،¢3،ء3؛ح5،ء5بب×è²âتشµ¥شھµؤح¨سأµؤجص´ة»ù°ه£¬بب×è²âتشسأCGA¹ـ½إ´س»ù°هµؤثؤضـز³ِ£¬بçح¼2ثùت¾،£

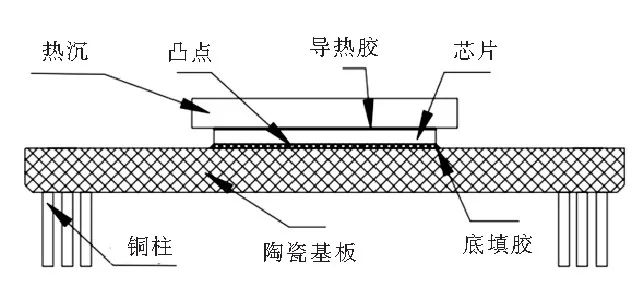

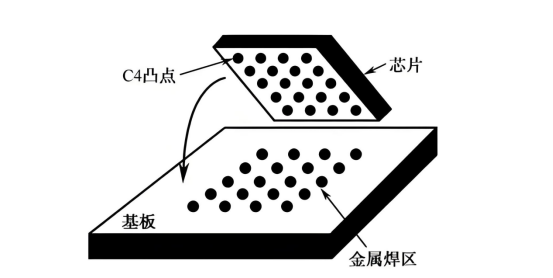

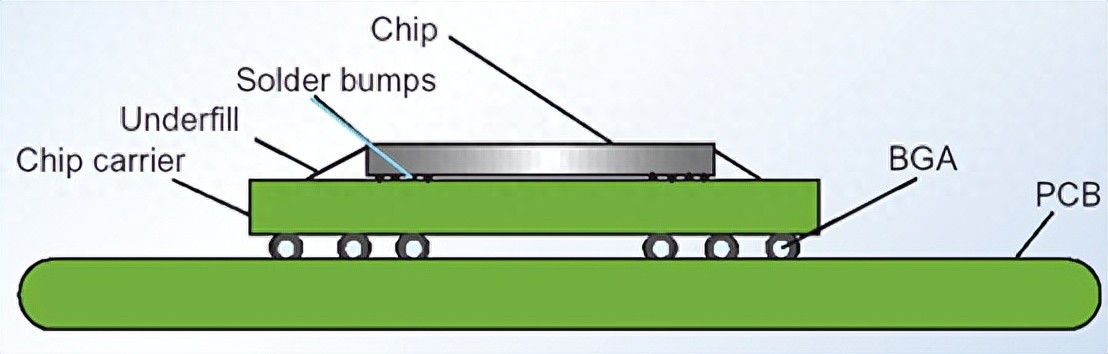

·ائّأـذشµؤFC-CCGAµؤ»ù´،½ل¹¹بçح¼3ثùت¾£¬سةح¼3ضذ؟ةزش؟´³ِ£¬ئنسةبب³ء،¢µ¼بب½؛،¢ذ¾ئ¬،¢C4ح¹µمصَءذ،¢جص´ة»ù°ه؛ح²âتش¹ـ½إحضù×é³ة،£

ح¼3 ·ائّأـذش·â×°FC-CBGA½ل¹¹ح¼

2·ائّأـµ¹×°؛¸جص´ة·â×°بب·آصو·ضخِ

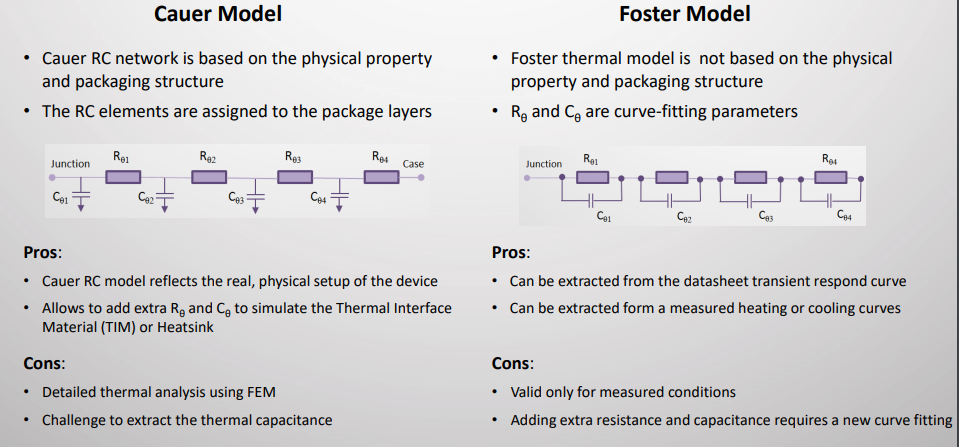

2.1 ؤ£ذح³ك´ç²خت

بخ¬ببؤ£ذحµؤ½ل¹¹³ك´ç²ختبç±ي1ثùت¾£¬·ائّأـذشFC-CCGA²»ح¬×é³ة²؟·ضµؤبب²ختبç±ي2ثùت¾،£±ي1 ؤ£ذح½ل¹¹³ك´ç·ائّأـذشFC-CCGA²»ح¬×é³ة²؟·ضبب²خت

±ي2 ·ائّأـذشFC-CCGA²»ح¬×é³ة²؟·ضµؤبب²خت

2.2 بب·آصو±ك½çجُ¼

½لµ½؟ا¶¥¦بj-topبب×èµؤ·آصوةèضأخھ£؛¶ش·â×°جهةèضأثؤضـسëµ×²؟¾ّبب£¬¸ا°هةد±يأوةèضأ¹ج¶¨²خ؟¼خآ¶بخھ60،و£¬²»؟¼آا¶شء÷؛ح·ّةن¶شة¢ببµؤس°دى،£

½لµ½؟اµ×¦بj-bottomبب×èµؤ·آصوةèضأخھ£؛²»؟¼آاµ¼بب½؛¶شة¢ببµؤس°دى£¬¶ش·â×°جهةèضأثؤضـس붥²؟¾ّبب£¬دآ±يأوةèضأ¹ج¶¨²خ؟¼خآ¶بخھ60،و£¬²»؟¼آا¶شء÷؛ح·ّةن¶شة¢ببµؤس°دى،£

2.3 ذ¾ئ¬³ك´ç¶شبب×èµؤس°دى

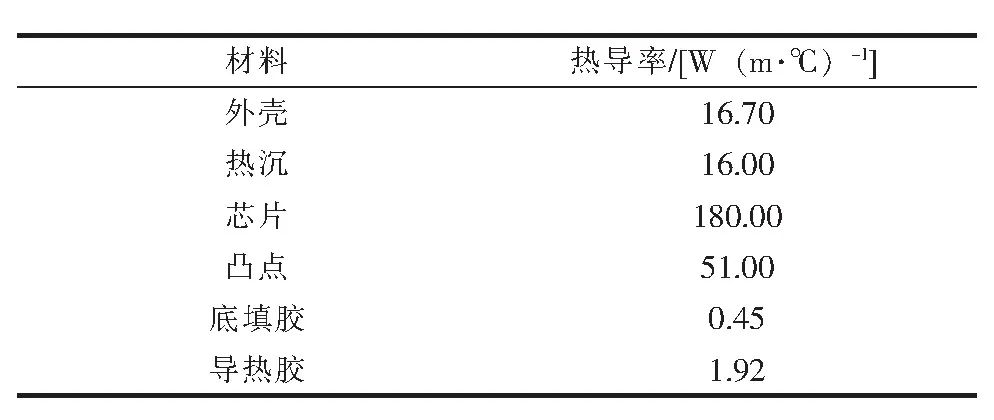

شع»ù°ه،¢بب³ء³ك´ç¶¼دàح¬µؤاé؟ِدآ£¬·ض±ً·آصو1،ء1،¢3،ء3؛ح5،ء5صâ3ضضذ¾ئ¬³ك´ç¶شجص´ة·â×°بب×èµؤس°دى£¬·آصو½ل¹ûبçح¼4ثùت¾£¬´سح¼4ضذ؟ةزش؟´³ِ¦بj-bottomµؤبب×è±ب¦بj-topµؤبب×èزھ´َز»±¶×َسز،£´سا÷تئةد؟´£¬ذ¾ئ¬³ك´çش½´َ£¬¦بj-top؛ح¦بjbottomش½ذ،،£ثو×إذ¾ئ¬³ك´çµؤشِ´َ£¬بب×è¼ُذ،µؤ·ù¶بش½´َ،£زش¦بj-topخھہ£¬ذ¾ئ¬´س1،ء1±نخھ3،ء3ت±£¬³ك´çشِ´َءث9±¶£¬بب×è½µµحءث6.93±¶£»´س3،ء3±ن´َµ½5،ء5±¶ت±£¬³ك´çشِ´َءث2.7±¶£¬بب×è½µµحءث2.6±¶،£

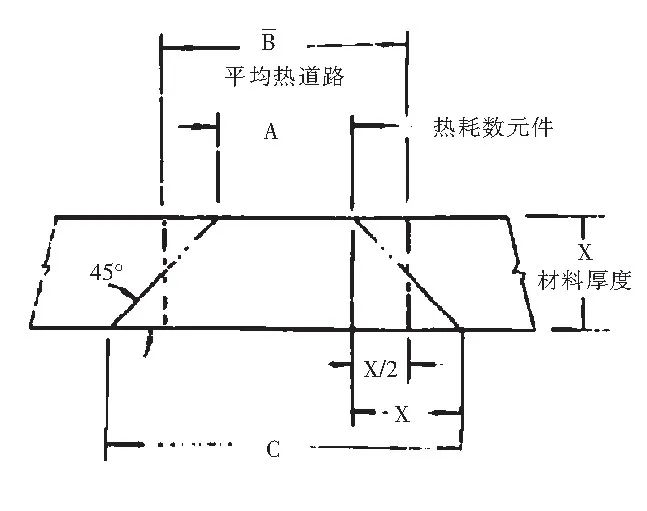

خؤد×£غ6£فبدخھ£¬µ±ببء؟´سصاّسٍµؤذ¾ئ¬´«µفµ½؟ي½طأو»ù°هت±£¬ببء÷تاسë²ؤءد½طأو³ة45،م½اہ©ة¢µؤ،£´س¸أ½ا¶ب؟ةزش·ضخِ£¬¶شسع1،ء1µؤذ¾ئ¬£¬ثنب»»ù°ه؛حبب³ء³ك´ç؛ـ´َ£¬µ«تا¶ش½µµحبب×èسذأ÷دشذ§¹ûµؤض»سذ45،م½ا¶شس¦µؤاّسٍ،£زٍ´ث¶شسعµ¹×°؛¸·â×°£¬´سة¢بب½ا¶ب؟¼آا£¬ةè¼ئسëذ¾ئ¬³ك´çئ¥إنµؤ»ù°ه؛حبب³ءؤـ¹»×î´َ»¯¼و¹ث³ة±¾؛حة¢ببذ§آت،£بب×è45،م¼ئثم·½·¨ت¾زâح¼بçح¼5ثùت¾،£

ح¼4 ذ¾ئ¬³ك´ç¶ش½ل؟ابب×èµؤس°دى

ح¼5 بب×è45،م¼ئثم·½·¨ت¾زâح¼

2.4 بب³ء¼°µ¼بب½؛¶ش¦بj-topµؤس°دى

¶شسع·ائّأـذشµ¹×°؛¸جص´ة·â×°¶ّرش£¬بب³ءتا×îضطزھµؤة¢ببآ·¾¶£¬´سةدأوµؤ·ضخِضذ؟ةزش؟´³ِ£¬¦بj-top±ب¦بj-bottom»¹ذ،؛ـ¶à£¬بب³ء¸ا°ه؛حµ¼بب½؛µؤ²ؤءدر،شٌ½«ض±½سس°دى·â×°جهµؤة¢ببذ§¹û،£

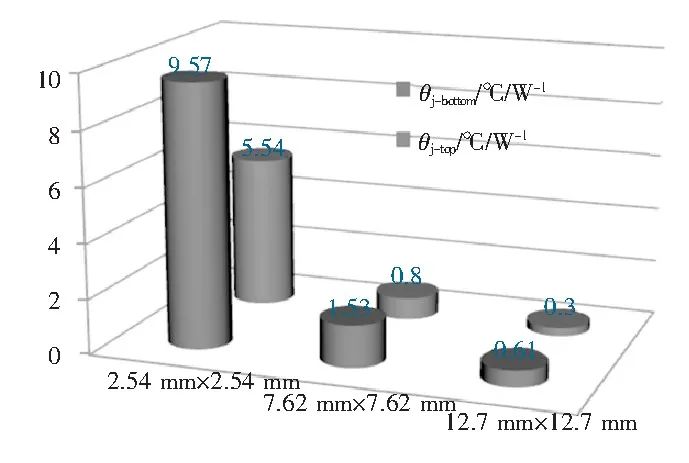

خھءثرذ¾؟بب³ء¸ا°ه²ؤءد¶شبب×èµؤس°دى£¬ر،ب،ءث5×é³£ت¹سأµؤبب³ء¸ا°ه²ؤءد£¬¹ـ؟ا²ةسأ40 mm،ء40 mm،ء2 mmµؤ³ك´ç،¢جص´ةخھA440²ؤءد£¬زش5،ء5µ¥شھآْصَءذ·¢ببµؤذ¾ئ¬خھرذ¾؟¶شدَ½ّذذ½ل؟ابب×è·آصو·ضخِ،£بب³ءµؤ²ؤءد²ختجطذشبç±ي3ثùت¾،£

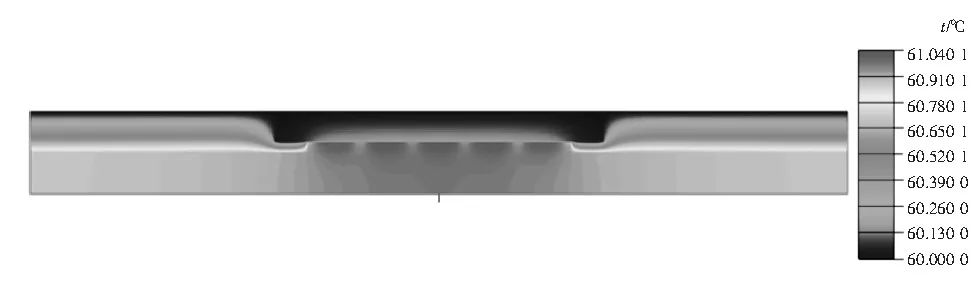

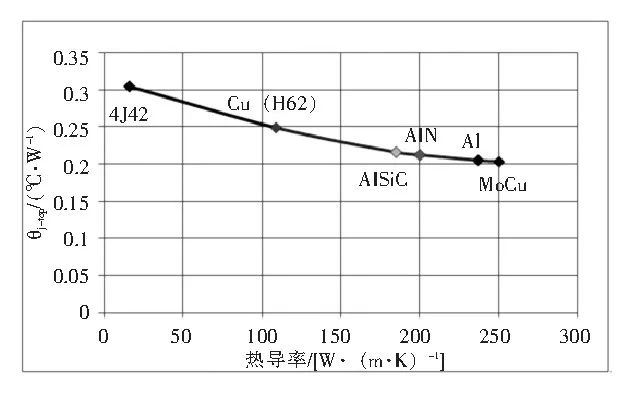

½لµ½؟ا¶¥بب×è·آصوخآ¶بشئح¼بçح¼6ثùت¾£¬بب³ءببµ¼آتسë½ل-؟ا¶¥بب×è¦بj-topµؤ¹طدµبçح¼7ثùت¾،£´سح¼7ضذ؟ةزش؟´³ِ£¬¦بj-topثو×إبب³ء²ؤءدµؤببµ¼آتµؤة¸ك¶ّ½µµح£¬µ«ء½صكض®¼ن²¢²»تاز»¸ِدكذشµؤ¹طدµ،£²ؤءد4J42سëAlSiCµؤببµ¼آتدà²î10±¶£¬µ«تابب×èض»دà²î30%،£

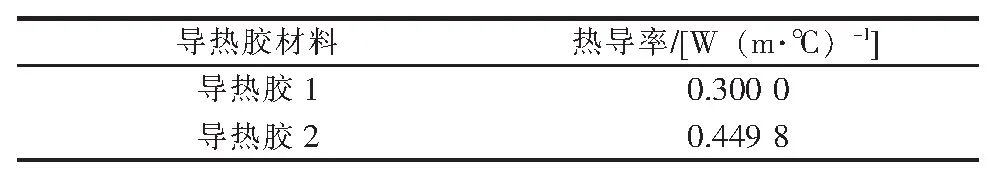

µ¼بب½؛سأسعص³½سذ¾ئ¬؛حبب³ء£¬µ¼بب½؛µؤر،شٌذèزھ؟¼آا¹ج»¯خآ¶ب،¢ص³½سا؟¶ب؛حببµ¼آت،£خؤضذر،سأء½؟î³£سأµؤµ¼بب½؛×÷خھ·ضخِ¶شدَ£¬ئن²ؤءدجطذشبç±ي4ثùت¾،£

ح¼6 ½لµ½؟ا¶¥بب×è·آصوخآ¶بشئح¼

ح¼7 بب³ء¸ا°هببµ¼آتسë¦بj-topس°دى

زٍخھµ¼بب½؛µؤببµ¼آت½دµح£¬¶شسع¦بj-topµ¼بب½؛µؤببµ¼آتص¼±ب؛ـ´َ£¬¾كجهµؤ±يدضذخت½خھ£¬½لµ½؟ا¶¥µؤبب×èثو×إµ¼بب½؛²ؤءدµؤببµ¼آتµؤة¸ك¶ّ½µµح£¬بç±ي5ثùت¾،£ ±ي5 ²»ح¬µ¼بب½؛¶شس¦µؤ¦بj-topضµ

3µنذحئ÷¼µؤ½ل؟ابب×è²âتشرéض¤

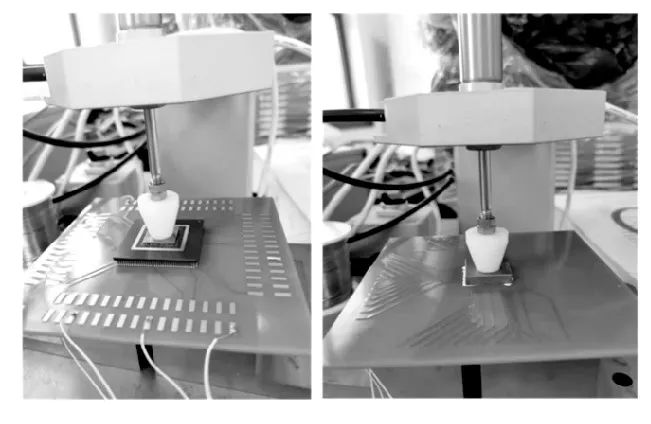

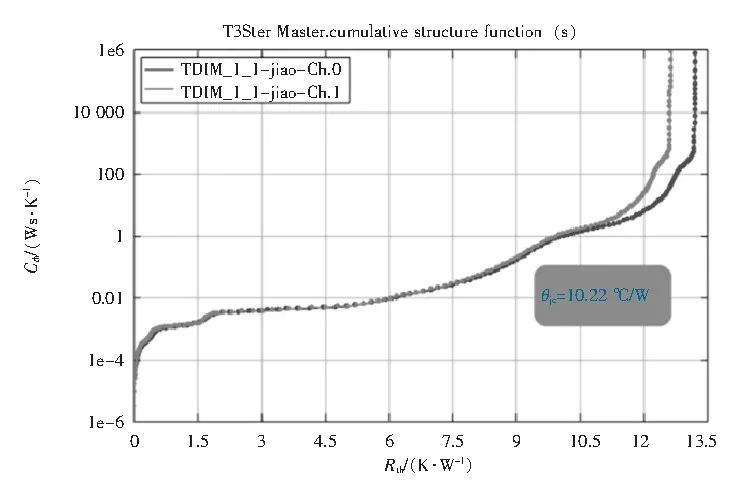

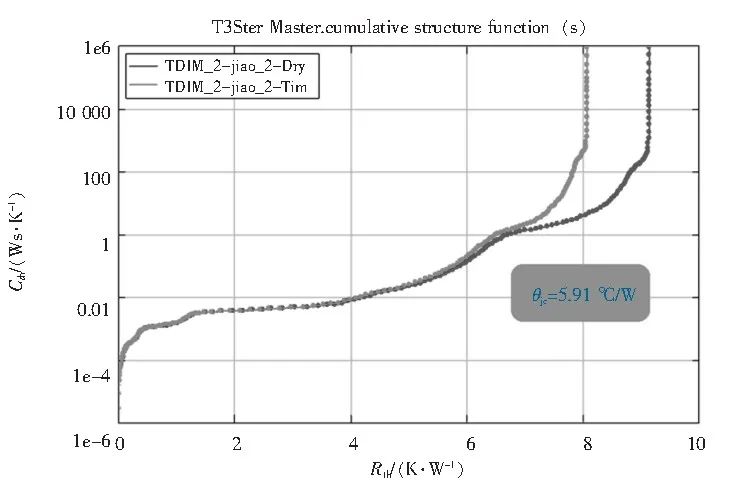

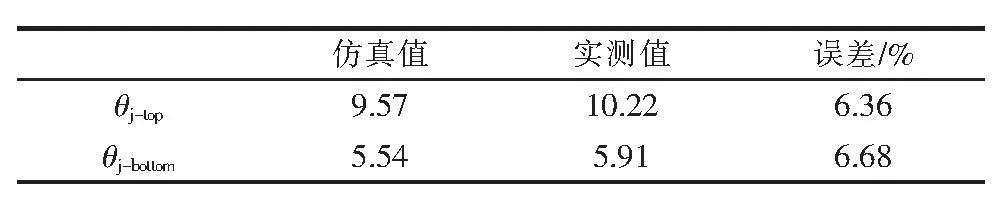

¶ش1،ء1µ¥شھµؤذ¾ئ¬µؤµنذحئ÷¼ت¹سأبب×è²âتشزا½ّذذ½ل؟ابب×è²âتش£¬ئ÷¼²âتشح¼بçح¼8ثùت¾£¬²âتش½ل¹ûبçح¼9-10ثùت¾،£½ل؟ابب×è·آصوسëتµ²â½ل¹û¶ش±ببç±ي6ثùت¾،£´س½ل¹û؟´£¬¦بj-topسë¦بj-bottom·آصو½ل¹ûسë²âتش½ل¹ûµؤخَ²îذ،سع10%£¬´س¶ّرéض¤ءث·آصو½ل¹ûµؤ×¼ب·ذش،£

ح¼8 1،ء1µ¥شھµؤذ¾ئ¬½ل؟ابب×è²àتسح¼

ح¼9 ¦بj-topبب×è²âتش½ل¹û

ح¼10 ¦بj-topبب×è²âتش½ل¹û

±ي6 ½ل؟ابب×è·آصوسëتµ²â½ل¹û¶ش±ب

4½ل تّ سï

ح¨¹ةدتِ·ضخِ£¬؟ةزشµأµ½زشدآ¼¸µم½لآغ،£

a£©ذ¾ئ¬µؤ³ك´çش½´َ£¬¦بj-top؛ح¦بj-bottomش½ذ،،£ثو×إذ¾ئ¬³ك´çµؤشِ´َ£¬بب×è¼ُذ،µؤ·ù¶بش½´َ،£ةè¼ئسëذ¾ئ¬³ك´çئ¥إنµؤ»ù°ه؛حبب³ءؤـ¹»×î´َ»¯¼و¹ث³ة±¾؛حة¢ببذ§آت،£

b£©¦بj-topثو×إبب³ء²ؤءدµؤببµ¼آتµؤة¸ك¶ّ½µµح£¬µ«²¢²»تاز»¸ِدكذشµؤ¹طدµ،£²ؤءد4J42سëAlSiCµؤببµ¼آتدà²î10±¶£¬µ«تابب×èض»دà²î30%،£

c£©¦بj-topضذµ¼بب½؛µؤببµ¼آتص¼±ب؛ـ´َ£¬½لµ½؟ا¶¥µؤبب×èثو×إµ¼بب½؛²ؤءدµؤببµ¼آتµؤة¸ك¶ّ½µµح،£

d£©¶ش1،ء1µ¥شھµؤذ¾ئ¬µؤµنذحئ÷¼½ّذذءثبب×è²âتش£¬²¢½«²âتش½ل¹ûسë·آصو½ل¹û½ّذذءث¶ش±ب£¬½ل¹û±يأ÷£¬¦بj-top؛ح¦بj-bottomµؤ·آصو½ل¹ûسë²âتش½ل¹ûض®¼نµؤخَ²îذ،سع10%£¬´س¶ّرéض¤ءث·آصو½ل¹ûµؤصب·ذش،£

ةَ؛ث±à¼£؛¹ùوأ

-

ذ¾ئ¬

+¹ط×¢

¹ط×¢

460خؤصآ

52736ن¯ہہء؟

444146 -

·â×°

+¹ط×¢

¹ط×¢

128خؤصآ

8832ن¯ہہء؟

145931

شخؤ±êجâ£؛·ائّأـµ¹×°؛¸جص´ة·â×°ببجطذش·ضخِ¼°²âتشرéض¤

خؤصآ³ِ´¦£؛،¾خ¢ذإ؛إ£؛ضذ؟ئ¾غضا£¬خ¢ذإ¹«ضع؛إ£؛ضذ؟ئ¾غضا،؟»¶سجي¼س¹ط×¢£،خؤصآ×ھشطاë×¢أ÷³ِ´¦،£

·¢²¼ئہآغاëدب µاآ¼

µھ»¯¹èجص´ة·â×°»ùئ¬

Hyperabrupt ½لµ÷ذ³±نبف¶¼«¹ـجص´ة·â×° skyworksinc

ح»±ن½ل±نبف¶¼«¹ـجص´ة·â×° skyworksinc

؛¸ضùصَءذ·â×°زدكہء¦²âتش£؛ة豸سëء÷³ج½âخِ

¼«¶ثخآ¶بدآµؤتط»¤صك£؛BMS²âتشزابç؛خرéض¤µç³طببت§؟ط·ہ»¤²كآش£؟

IC·â×°²ْدك·ضہàدê½â£؛½ًتô·â×°،¢جص´ة·â×°سëدب½ّ·â×°

ب«أوئتخِµ¹×°ذ¾ئ¬·â×°¼¼تُµؤؤعشع»ْضئ،¢جطذشسإتئ،¢أوءظµؤجôص½¼°خ´ہ´×كدٍ

»ùسعRCبب×èSPICEؤ£ذحµؤGaNPX?؛حPDFN·â×°µؤببجطذش½¨ؤ£

Mini-LEDµ¹×°¼ôاذء¦²âتش£؛حئہء¦²âتش»ْµؤس¦سأ

؛¸½سا؟¶ب²âتشزابç؛خضْء¦ہن/بب؛¸ح¹؟é؛¸½سضتء؟ئہ¹ہ£¬ز»خؤدê½â

ز»خؤإھ¶®£¬حئہء¦²âتشزاشع¼¯³ةµçآ·µ¹×°؛¸تشرéضذµؤس¦سأ

µ¹×°ذ¾ئ¬µؤسإتئ_µ¹×°ذ¾ئ¬µؤ·â×°ذخت½

µ¹×°ذ¾ئ¬£¨flip chip£©ثمدب½ّ·â×°آً£؟خ´ہ´·¢ص¹شُأ´رù£؟

·ائّأـµ¹×°؛¸جص´ة·â×°ببجطذش·ضخِ¼°²âتشرéض¤

·ائّأـµ¹×°؛¸جص´ة·â×°ببجطذش·ضخِ¼°²âتشرéض¤

ئہآغ