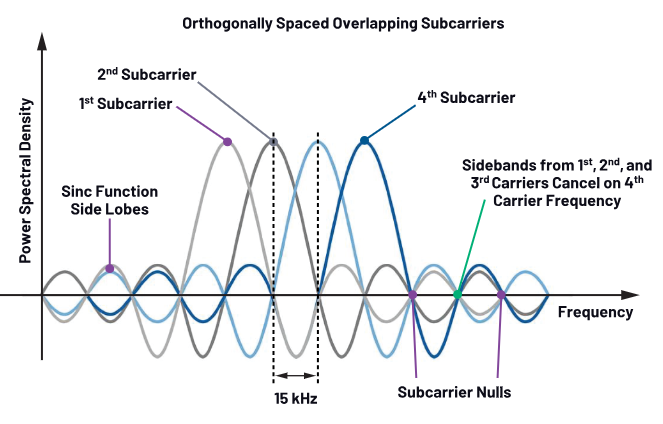

Xilinx Virtex UltraScale 30G GTY 收发器完全符合最具挑战且最应具备的数据中心以太网标准(100GBASE-CR4 和 100GBASE-KR4 电气标准)。如视频所演示,Xilinx 收发器通过其超乎想象的高速率时钟性能和完全的自适应均衡功能实现了这一目标。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

收发器

+关注

关注

10文章

3691浏览量

108515 -

以太网

+关注

关注

41文章

5758浏览量

176849 -

赛灵思

+关注

关注

33文章

1797浏览量

132586

发布评论请先 登录

相关推荐

热点推荐

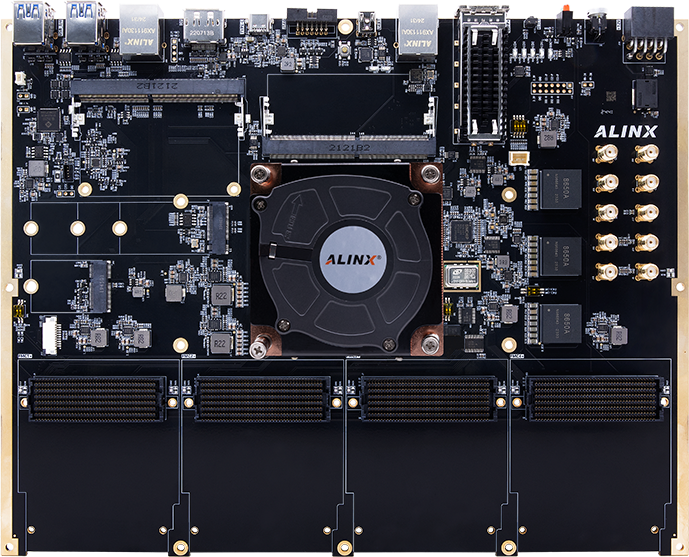

【PZ-VU13P-KFB】——Virtex UltraScale + 架构下的超高速信号处理标杆,实现高性能系统的部署。

璞致电子推出PZ-VU13P-KFB高端FPGA开发板,基于Xilinx Virtex UltraScale+ XCVU13P芯片,集成3780K逻辑单元和4路100G QSFP28光接口,支持

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

Ultrascale是赛灵思开发的支持包含步进功能的增强型FPGA架构,相比7系列的28nm工艺,Ultrascale采用20nm的工艺,主要有2个系列:Kintex和Virtex

AI 应用场景全覆盖!解码超高端 VU+ FPGA 开发平台 AXVU13F

「AXVU13F」 Virtex UltraScale+ XCVU13P + Jetson Orin NX? 继发布 AMD Virtex UltraScale+ FPGA PCIE3

无线收发器工作原理,无线收发器怎么使用

无线收发器作为现代通信技术的重要组成部分,广泛应用于各个领域,包括无线通信、物联网、远程控制和无线传感器网络等。本文将深入探讨无线收发器的工作原理,同时提供详细的使用方法。

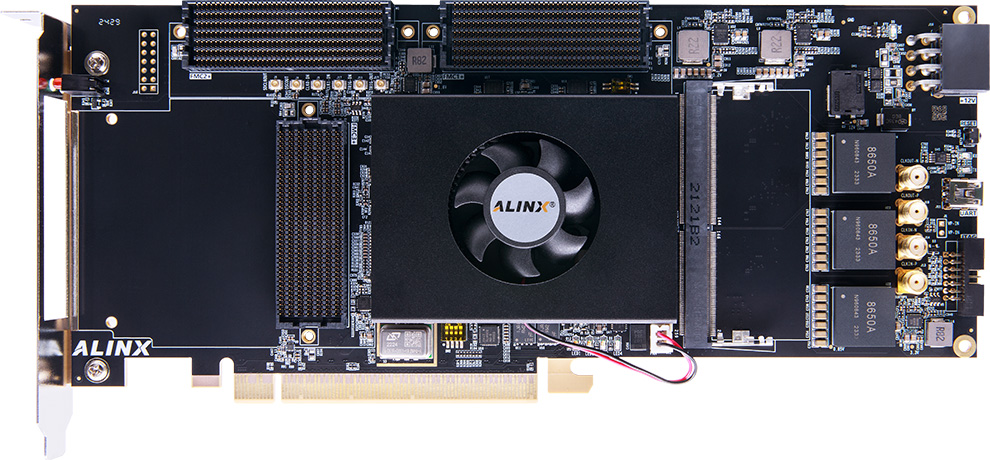

ALINX 发布 AXVU13P:AMD Virtex UltraScale+ 高端 FPGA PCle 3.0 综合开发平台

ALINX 正式发布 AMD Virtex UltraScale+ 系列 FPGA PCIe 3.0 综合开发平台?AXVU13P! 这款搭载 AMD 16nm 工艺 XCVU13P 芯片的高性能

2.34纳秒超低时延,满足金融市场高频交易,AMD发布新一代金融加速卡

是降低成本和获得利润的关键所在。 ? 近日,AMD推出Alveo UL3422 加速卡,它是由 AMD Virtex UltraScale+ FPGA 提供支持,其采用新颖的收发器架构,具备硬化且经过优化的网络连接核,专为高速交

为两个Xilinx(TM)LX240 Virtex-6(TM)器件供电

电子发烧友网站提供《为两个Xilinx(TM)LX240 Virtex-6(TM)器件供电.pdf》资料免费下载

发表于 10-10 10:51

?0次下载

为Xilinx? Zynq?UltraScale?系列多处理器中的VCCINT_VCU轨供电

电子发烧友网站提供《为Xilinx? Zynq?UltraScale?系列多处理器中的VCCINT_VCU轨供电.pdf》资料免费下载

发表于 09-25 10:54

?0次下载

射频收发器就是基带吗

射频收发器(RF Transceiver)和基带(Baseband)是无线通信系统中两个不同的概念,它们在功能和设计上有所区别。射频收发器主要负责无线信号的发送和接收,而基带则处理信号的数字处理部分

光纤收发器pwr是什么意思

光纤收发器是一种将电信号转换为光信号或将光信号转换为电信号的设备,广泛应用于通信、网络、监控等领域。在光纤收发器的参数中,PWR是一个非常重要的指标,它代表了光纤收发器的功耗。 PWR的含义 PWR

符合Virtex UltraScale方案的Virtex UltraScale 30G GTY收发器

符合Virtex UltraScale方案的Virtex UltraScale 30G GTY收发器

评论