声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1797浏览量

132580 -

IP

+关注

关注

5文章

1824浏览量

153144 -

时钟

+关注

关注

11文章

1908浏览量

133456

发布评论请先 登录

相关推荐

热点推荐

黑芝麻智能跨域时间同步技术:消除多域计算单元的时钟信任鸿沟

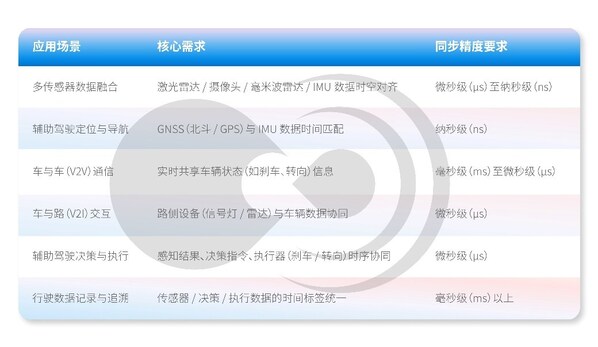

,并以黑芝麻智能武当 C1296 芯片为例,通过多方式同步实现多域高精度对齐,消除时钟信任鸿沟的实测效果。 智能汽车的核心是通过多维度感知、实时决策和精准控制实现辅助驾驶与智能交互,而这一切的前提是?"时间基准一致",由于不同传感器采集数据的频率、机制不同,只有在时间

AMD Vivado Design Suite 2025.1现已推出

AMD Vivado Design Suite 2025.1 现已推出,支持 AMD Spartan UltraScale+ 和新一代 Versal 器件。这一最新版本还新增了多项功能,可显著提升 Versal SSIT 器件的 FMAX 值,并对所有系列产品在 IP 集

跨异步时钟域处理方法大全

该方法只用于慢到快时钟域的1bit信号传递。在Xilinx器件中,可以使用(* ASYNC_REG = "TRUE" *)标记,将两个寄存器尽量靠近综合,降低 亚稳态因导线延迟太大而传播到第二个寄存器的可能性。

FPGA时序约束之设置时钟组

Vivado中时序分析工具默认会分析设计中所有时钟相关的时序路径,除非时序约束中设置了时钟组或false路径。使用set_clock_groups命令可以使时序分析工具不分析时钟组中

Vivado FIR IP核实现

Xilinx的FIR IP核属于收费IP,但是不需要像 Quartus那样通过修改license文件来破解。如果是个人学习,现在网络上流传的license破解文件在破解Vivado的同时也破解

混合域示波器的原理和应用

部分包括一个或多个模拟通道,用于测量和显示模拟信号的波形;数字部分包括一个或多个数字通道,用于测量和显示数字信号的时序波形;RF通道则专门用于捕获和分析射频信号。

采样:混合域示波器通过模拟通道和数

发表于 12-27 15:54

Vivado中DDRX控制器(mig)ip核配置中关于命令序号选择和地址映射说明

本篇主要讨论Vivado中DDRX控制器(mig)ip核配置中关于命令序号选择和地址映射说明(一) 利用Xilinx 7系列FPGA开发时,经常需要驱动外部存储器--DDRX。Xilinx提供了

AMD Vivado Design Suite 2024.2全新推出

AMD Vivado Design Suite 2024.2 全新推出,使用 AMD Versal Adaptive SoC 进行设计的重大改进。此版本为 AMD Versal 自适应 SoC

vivado导入旧版本的项目,IP核心被锁。

vivado导入其他版本的项目的时候,IP核被锁,无法解开,请问该如何解决。

使用软件:vivado 2019.2

导入项目使用版本:vivado 2018

发表于 11-08 21:29

Vivado中FFT IP核的使用教程

本文介绍了Vidado中FFT IP核的使用,具体内容为:调用IP核>>配置界面介绍>>IP核端口介绍>>MATLAB生成测试数据>>测试verilogHDL>>TestBench仿真>>结果验证>>FFT运算。

Vivado使用小技巧

有时我们对时序约束进行了一些调整,希望能够快速看到对应的时序报告,而又不希望重新布局布线。这时,我们可以打开布线后的dcp,直接在Vivado Tcl Console里输入更新后的时序约束。如果调整

香港站群服务器多ip怎么样?

香港站群服务器多IP是指在香港地区部署的服务器,这些服务器具有多个独立的IP地址,用于托管和管理多个网站。以下是对香港站群服务器多

IP 地址管理与无类域间路由

CIDR是什么? 无类域间路由(CIDR)是一种用于 IP 地址分配和路由的技术。它摒弃了传统的 IP 地址分类(A、B、C 等类),采用可变长度子网掩码(VLSM),允许网络管理员根据实际需求灵活

如何使用Vivado IP Integrator组装具有多个时钟域的设计

如何使用Vivado IP Integrator组装具有多个时钟域的设计

评论