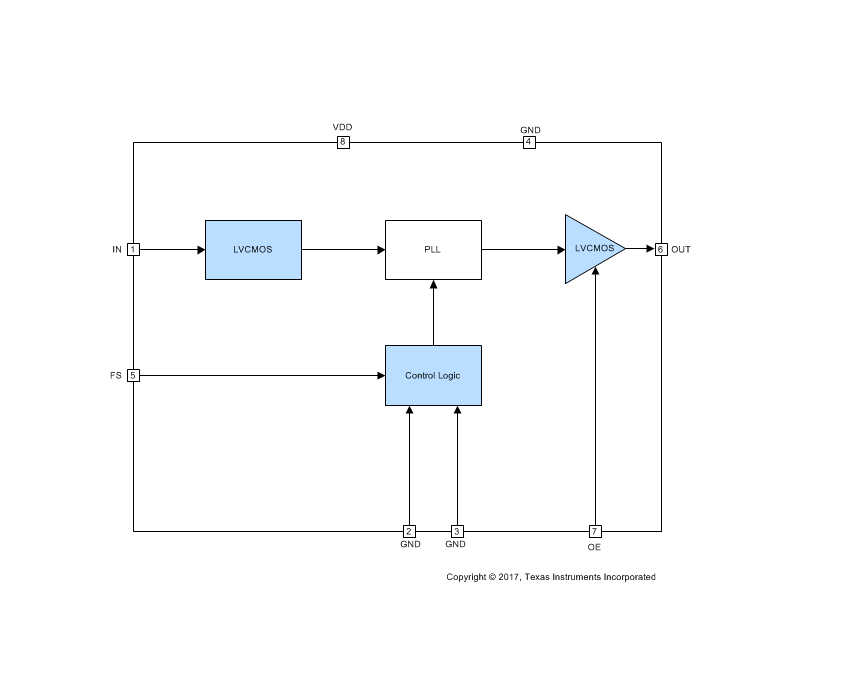

CDCS504-Q1器件是LVCMOS输入时钟缓冲器,具有可选的倍频功能。

CDCS504-Q1具有输出使能引脚。

*附件:cdcs504-q1.pdf

该器件在输入端接受3.3V LVCMOS信号。

输入信号由锁相环 (PLL) 处理,其输出频率等于输入频率或乘以 4 倍。

这样,该器件可以产生 2 MHz 至 108 MHz 之间的输出频率。

可以使用单独的控制引脚来启用或禁用输出。CDCS504-Q1器件在3.3 V环境中工作。

它的工作温度范围为–40°C至105°C,采用8引脚TSSOP封装。

特性

- 符合汽车应用标准

- AEC-Q100 测试指南,结果如下:

- 器件温度等级 2:–40°C 至 105°C 环境工作温度范围

- 设备 HBM ESD 分类等级 H2

- 设备 CDM ESD 分类级别 C3B

- 易于使用的时钟发生器器件系列的一部分

- 具有可选输出频率的时钟乘法器

- 频率倍增可在 x1 或 x4 之间选择,带有一个外部控制引脚

- 通过控制引脚输出禁用

- 单 3.3V 器件电源

- 宽温度范围:–40°C 至 105°C

- 低空间消耗 8 引脚 TSSOP 封装

- 使用 CDCS504-Q1 创建自定义设计,并使用WEBENCH 电源设计器^?^

参数

方框图

?1. 产品概述?

CDCS504-Q1是德州仪器(TI)推出的汽车级LVCMOS输入时钟缓冲/乘法器,具有以下核心特性:

- ?汽车认证?:通过AEC-Q100 Grade 2认证(-40°C至105°C工作温度范围),符合HBM ESD H2级和CDM ESD C3B级标准。

- ?灵活频率控制?:通过外部引脚(FS)选择×1(缓冲)或×4(倍频)模式,输出频率范围2 MHz至108 MHz。

- ?低功耗设计?:单3.3V电源供电,典型工作电流24 mA(输入频率3.072 MHz时)。

- ?紧凑封装?:8引脚TSSOP封装(3.0 mm × 4.40 mm)。

?2. 关键功能?

- ?输出使能?:通过OE引脚控制输出状态(高电平启用,低电平禁用)。

- ?低抖动性能?:典型周期抖动为144 ps(×4模式,110 MHz输出)。

- ?宽温支持?:全温度范围内保持稳定输出,适用于严苛环境。

?3. 应用场景?

?4. 设计要点?

- ?电源建议?:需在VDD引脚附近放置0.01 ?F去耦电容。

- ?输入要求?:LVCMOS输入信号需满足VIH/VIL电平标准(VIL ≤ 0.3×VDD, VIH ≥ 0.7×VDD)。

- ?无输入时钟时?:建议置OE为低以避免随机输出脉冲。

?5. 文档结构?

- ?技术参数?:包含绝对最大额定值、ESD等级、电气特性(如VOH/VOL电平、上升/下降时间)。

- ?典型曲线?:提供抖动、功耗与温度/频率的关系图。

- ?布局示例?:推荐PCB设计指南及50Ω阻抗匹配方案。

?6. 订购信息?

- 型号:CDCS504TPWRQ1(TSSOP-8封装,卷带包装,2000片/卷)。

- 环境评级:符合RoHS标准,MSL3级(260℃峰值回流焊)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时钟缓冲器

+关注

关注

2文章

175浏览量

51488 -

封装

+关注

关注

128文章

8920浏览量

146416 -

引脚

+关注

关注

16文章

1908浏览量

53817 -

LVCMOS

+关注

关注

1文章

113浏览量

11786

发布评论请先 登录

相关推荐

热点推荐

MPY600 具有负载驱动功能的乘法器

如图所示为有负载驱动能力的乘法电路。由乘法器MPY600和高速缓冲器OPA633组成具有负载驱动能力的乘法器电路

发表于 01-29 19:01

?1604次阅读

使用verilogHDL实现乘法器

VerilogHDL语言实现的两位阵列乘法器和传统的 Booth编码乘法器进行了性能比较,得出用这种混合压缩的器乘法器要比传统的4-2压缩器

发表于 12-19 13:30

?1.1w次阅读

乘法器原理_乘法器的作用

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数技术来实现。

发表于 02-18 15:08

?2.8w次阅读

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析 什么是时钟缓冲器(Buff

发表于 10-18 18:36

?3w次阅读

CDCL6010 1.8V 11输出时钟乘法器、分配器、抖动消除器和缓冲器数据表

电子发烧友网站提供《CDCL6010 1.8V 11输出时钟乘法器、分配器、抖动消除器和缓冲器数据表.pdf》资料免费下载

发表于 08-22 11:18

?0次下载

CDCF5801A具有延迟控制和相位对准的时钟乘法器数据表

电子发烧友网站提供《CDCF5801A具有延迟控制和相位对准的时钟乘法器数据表.pdf》资料免费下载

发表于 08-22 10:56

?0次下载

CDCS503带可选SSC的时钟缓冲器/时钟乘法器数据表

电子发烧友网站提供《CDCS503带可选SSC的时钟缓冲器/时钟乘法器数据表.pdf》资料免费下载

发表于 08-22 09:18

?0次下载

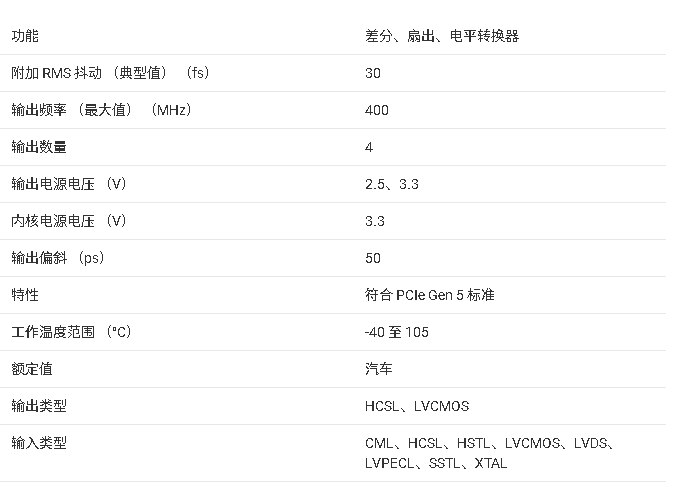

?LMK00334-Q1 四输出时钟缓冲器和电平转换器技术文档总结

LMK00334 -Q1 器件是一款 4 输出 HCSL 扇出缓冲器,用于高频、低抖动时钟、数据分配和电平转换。它能够为 ADC、DAC、多千兆以太网、XAUI、光纤通道、SATA/SAS、SONET/SDH、CPRI 和高频背

?CDCS504-Q1 时钟缓冲器和时钟乘法器技术文档总结

?CDCS504-Q1 时钟缓冲器和时钟乘法器技术文档总结

评论