LMK04228 器件是业界高性能时钟调节器,支持 JEDEC JESD204B。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个JESD204B转换器或其他逻辑器件。SYSREF 可以使用直流和交流耦合提供。不仅限于JESD204B应用,14 个输出中的每一个都可以单独配置为传统时钟系统的高性能输出。

高性能与在功率或性能之间权衡的能力、双 VCO、保持以及每个输出可调的模拟和数字延迟等功能相结合,使该LMK04228成为提供灵活的高性能时钟树的理想选择。

*附件:lmk04228.pdf

特性

- JEDEC JESD204B支持

- 超低 RMS 抖动

- 156 fs RMS 抖动(12 kHz 至 20 MHz)

- 245 fs RMS 抖动(100 Hz 至 20 MHz)

- 245.76 MHz时–162.5 dBc/Hz本底噪声

- PLL2 提供多达 14 个差分器件时钟

- 多达 7 个 SYSREF 时钟

- 最大时钟输出频率:1.25 GHz

- 来自PLL2的LVPECL、LVDS可编程输出

- 缓冲VCXO或PLL1的晶体输出

- LVPECL、LVDS、2xLVCMOS 可编程

- 双环路PLLatinum? PLL架构

- PLL1

- 多达 3 个冗余输入时钟

- 自动和手动切换模式

- 无中断开关和LOS

- 集成低噪声晶体振荡器电路

- 输入时钟丢失时的保持模式

- 多达 3 个冗余输入时钟

- PLL2

- 归一化 [1 Hz] PLL 本底噪声为

–224 dBc/Hz - 相位检测器速率高达 155 MHz

- OSCin 倍频器

- 两个集成低噪声VCO

- 归一化 [1 Hz] PLL 本底噪声为

- 50% 占空比输出分频,1 至 32

(偶数和奇数) - 精密数字延迟

- 25 ps 步进模拟延迟

- 多模:双 PLL 或单 PLL

- 工业温度范围:–40°C 至 85°C

- 3.15V 至 3.45V 工作电压

- 封装:64 引脚 WQFN (9.0 × 9.0 × 0.8 mm)

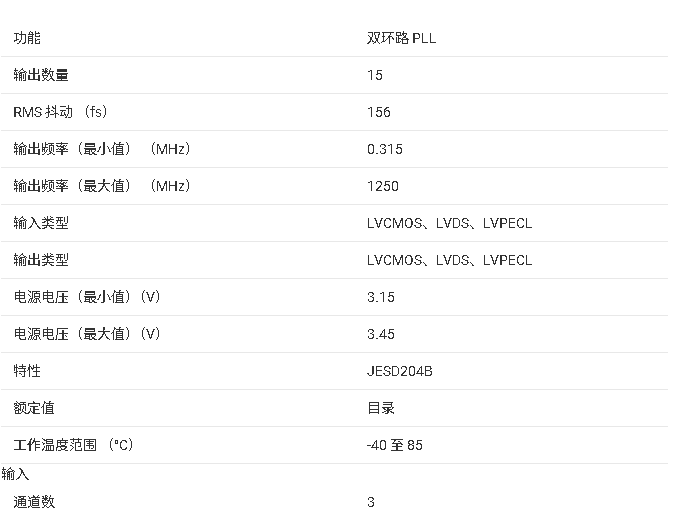

参数

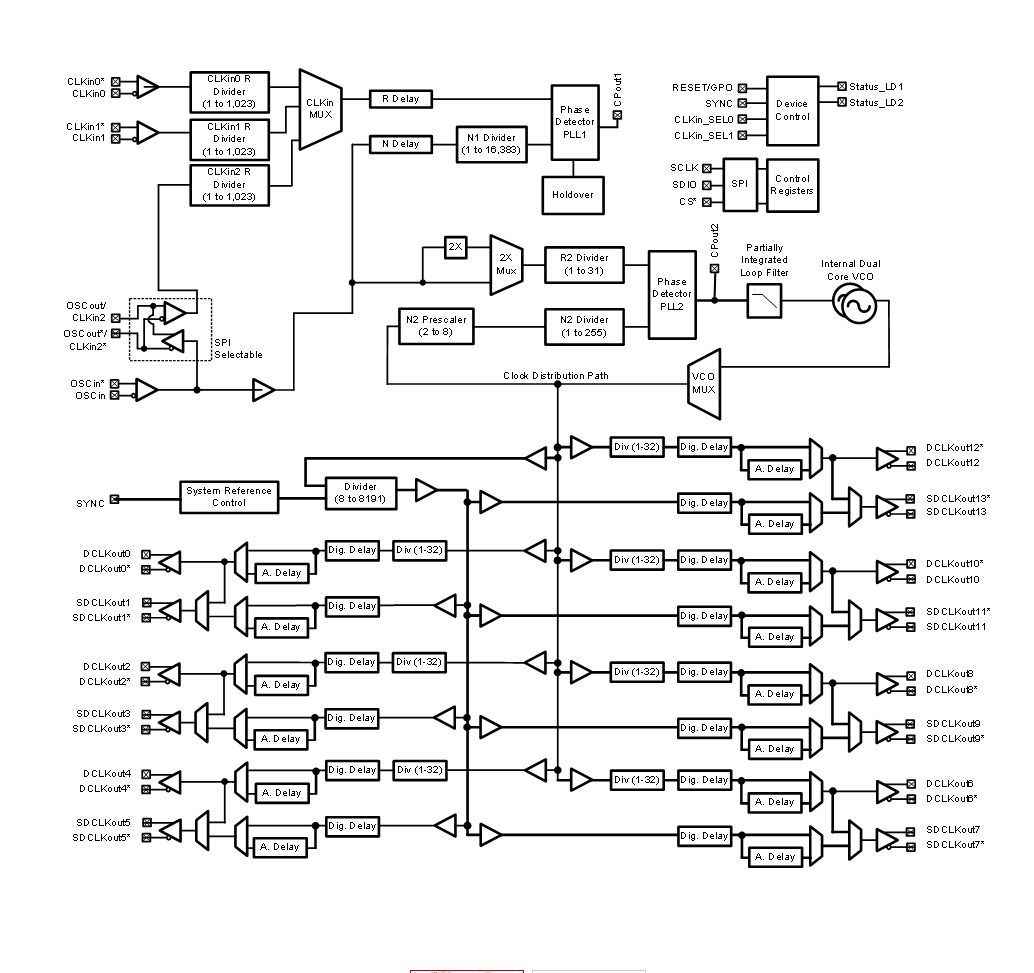

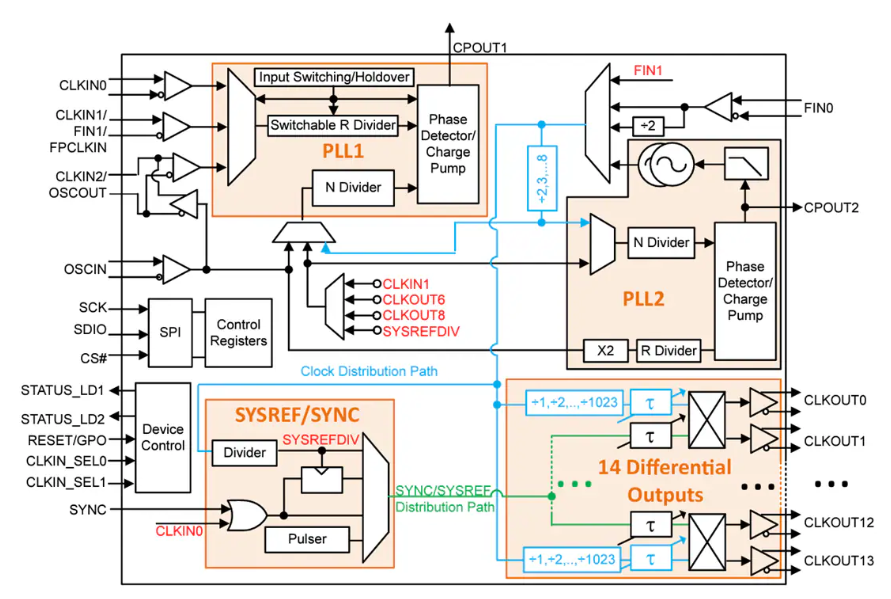

方框图

?1. 核心功能?

- ?双环PLL架构?:集成PLL1(参考时钟清洁)和PLL2(频率合成),支持JESD204B协议,提供超低RMS抖动(156 fs @12kHz-20MHz)。

- ?时钟输出?:14路可配置差分时钟(LVPECL/LVDS),最高1.25 GHz,支持7路设备时钟+7路SYSREF时钟,适用于JESD204B转换器或传统时钟系统。

- ?冗余输入?:3路参考时钟输入(CLKin0/1/2),支持自动/手动切换和故障切换(Hitless Switching)。

?2. 关键特性?

- ?低噪声性能?:噪声低至-162.5 dBc/Hz(245.76 MHz),集成双VCO(2370-2630 MHz和2920-3080 MHz)。

- ?灵活配置?:

- 可编程输出延迟(数字延迟3.5-32 VCO周期,模拟延迟25 ps步进)。

- 支持晶体/VCXO输入,提供缓冲输出(OSCout)至LVDS/LVPECL/LVCMOS。

- ?工业级可靠性?:工作温度-40°C至85°C,3.15-3.45V供电,64引脚WQFN封装(9×9 mm)。

?3. 应用场景?

?4. 技术细节?

- ?PLL1?:支持40 MHz相位检测频率,电荷泵电流可调(50-1550 ?A),集成保持模式(Holdover)以应对输入时钟丢失。

- ?PLL2?:155 MHz相位检测频率,内置可编程环路滤波器(3rd/4th阶),支持频率校准(通过寄存器0x168触发)。

?5. 编程与控制?

?6. 设计支持?

- 推荐使用TI的Clock Design Tool和TICS Pro软件进行频率规划和寄存器配置优化。

?附件内容范围?:涵盖器件特性、寄存器映射、电气参数、布局指南及典型应用电路。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pll

+关注

关注

6文章

904浏览量

136883 -

逻辑器件

+关注

关注

0文章

97浏览量

20489 -

调节器

+关注

关注

5文章

887浏览量

48401 -

清除器

+关注

关注

0文章

38浏览量

6031 -

交流耦合

+关注

关注

0文章

40浏览量

12494

发布评论请先 登录

相关推荐

热点推荐

LMK04832-SP时钟抖动清除器

3200 MHz时的超低噪声:61-fs RMS抖动(12 kHz至20 MHz)RMS抖动67-fs(100 Hz至100 MHz)–156.5-dBc / Hz的本底噪声锁相

发表于 03-24 16:13

LMK04714-Q1符合JESD204B/C标准的汽车级、超低噪声、双环路时钟抖动清除器数据表

电子发烧友网站提供《LMK04714-Q1符合JESD204B/C标准的汽车级、超低噪声、双环路时钟抖动

发表于 08-20 10:37

?0次下载

LMK04832-SEP符合JESD204B/C标准的航天级、超低噪声、双环路时钟抖动清除器数据表

电子发烧友网站提供《LMK04832-SEP符合JESD204B/C标准的航天级、超低噪声、双环路时钟抖动

发表于 08-20 10:39

?0次下载

LMK04368-EP符合JESD204B/C标准的超低噪声、双环路时钟抖动清除器数据表

电子发烧友网站提供《LMK04368-EP符合JESD204B/C标准的超低噪声、双环路时钟抖动清除器

发表于 08-20 09:52

?0次下载

LMK04832-SP符合JESD204B标准的航天级、超低噪声、双环路时钟抖动清除器数据表

电子发烧友网站提供《LMK04832-SP符合JESD204B标准的航天级、超低噪声、双环路时钟抖动清除

发表于 08-20 09:32

?0次下载

带双环路PLL且符合JESD204B标准的LMK04832超低噪声时钟抖动清除器数据表

电子发烧友网站提供《带双环路PLL且符合JESD204B标准的LMK04832超低噪声时钟抖动

发表于 08-21 09:20

?0次下载

LMK04906带6路可编程输出的,超低噪声时钟抖动清除器和乘法器数据表

电子发烧友网站提供《LMK04906带6路可编程输出的,超低噪声时钟抖动清除器和乘法器数据表.pdf》资料免费下载

发表于 08-21 09:21

?0次下载

具有双环路PLL的LMK04228超低噪声且符合JESD204B标准的时钟抖动清除器数据表

电子发烧友网站提供《具有双环路PLL的LMK04228超低噪声且符合JESD204B标准的时钟抖动

发表于 08-21 09:12

?0次下载

LMK04616 超低噪声低功耗JESD204B兼容时钟抖动清除器总结

LMK0461x 器件系列是业界性能最高、功耗最低的抖动清除器,支持 JESD204B。16 个时钟输出可配置为使用器件和 SYSREF 时钟

?LMK04228 超低噪声双环PLL时钟抖动清除器技术文档总结

?LMK04228 超低噪声双环PLL时钟抖动清除器技术文档总结

评论