Texas Instrument LMK04714-Q1双环时钟抖动清除器是一款高性能时钟调节器,支持JEDEC JESD204B/C,适用于航天应用。PLL2的每个14时钟输出均可配置为驱动七个JESD204B/C转换器。Texas Instrument LMK04714-Q1还可以使用自身和SYSREF时钟驱动其他逻辑器件。 SYSREF可以使用直流和交流耦合来提供。由于该器件不限于JESD204B/C应用,因此14输出可以单独配置为传统时钟系统的高性能输出。

数据手册:*附件:Texas Instruments LMK04714-Q1双环时钟抖动清除器数据手册.pdf

特性

- AEC-Q100等级1(-40°C至125°C)

- 3255MHz最大时钟输出频率

- 多模:双PLL、单PLL和时钟分配

- 6GHz外部VCO或分配输入

- 在2500MHz下的超低噪声

- 54fs RMS抖动(12kHz到20MHz)

- 64fs RMS抖动(100Hz到20MHz)

- 本底噪声:-157.6dBc/Hz

- 3200MHz处的超低噪音

- 61fs RMS 抖动(12kHz 至 20MHz)

- 67fs RMS 抖动(100Hz 到 100MHz)

- 本底噪声:-156.5dBc/Hz

- PLL2

- -230dBc/Hz的PLL FOM

- -128dBc/Hz的PLL 1/f

- 鉴相器速率高达320MHz

- 两个集成VCO:2440MHz至2600MHz和2945MHz至3255MHz

- 最多14个差分设备时钟

- 最多1个缓冲VCXO/XO输出

- LVPECL、LVDS、2xLVCMOS可编程

- 1-1023 CLKOUT整数分频器

- 1-8191 SYSREF整数除法器

- SYSREF时钟的25ps步进模拟延迟

- 设备时钟和SYSREF的数字延迟和动态数字延迟

- 使用PLL1的保持模式

- 0延迟与PLL1或PLL2

- 高可靠性

- 受控基线

- 唯一组装/测试站点

- 唯一制造厂

- 延长的产品寿命周期

- 延长的产品变更通知

- 产品可追溯性

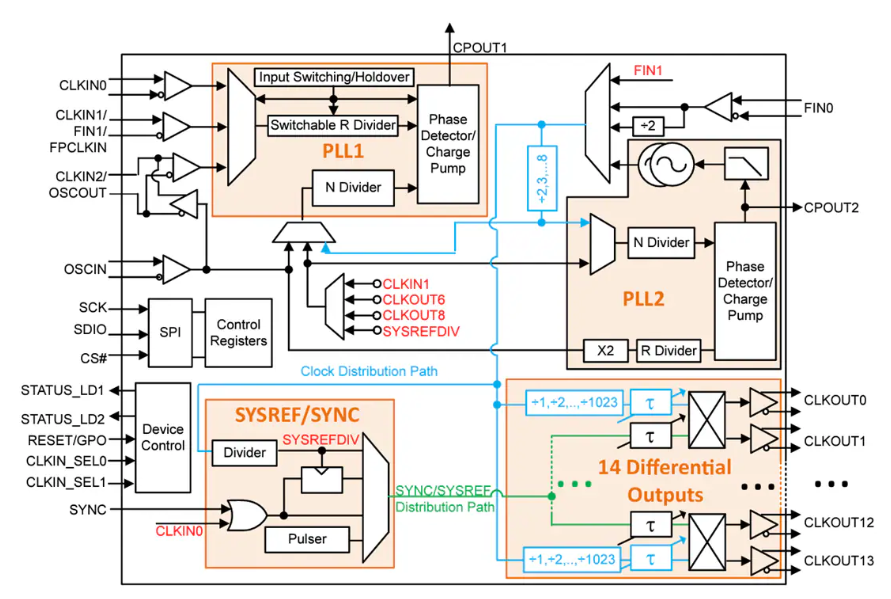

功能框图

高性能时钟抖动清除器LMK04714-Q1技术解析

一、产品概述

LMK04714-Q1是德州仪器(TI)推出的一款汽车级超低噪声双环时钟抖动清除器,专为JESD204B/C数据转换器时钟应用设计。作为AEC-Q100 Grade 1认证器件,它可在-40°C至+125°C温度范围内稳定工作,满足汽车雷达、激光雷达(LIDAR)等严苛环境应用需求。

该器件采用双PLL架构,集成两个内部VCO(2440-2600MHz和2945-3255MHz),支持高达3255MHz的时钟输出频率。其卓越的噪声性能表现在:

- 2500MHz时仅54-fs RMS抖动(12kHz-20MHz)

- 3200MHz时61-fs RMS抖动(12kHz-20MHz)

- 噪声底低至-157.6dBc/Hz

二、关键特性与技术优势

1. 双PLL架构设计

LMK04714-Q1采用创新的双PLL架构:

- ?PLL1?:负责低频段抖动清除,支持外部VCXO输入,典型环路带宽10-200Hz

- ?PLL2?:实现高频段频率合成,集成双VCO核心,典型环路带宽50-200kHz

这种架构通过对参考时钟进行两级处理,既保持了低频段的相位噪声优势,又利用了高频VCO的优异宽带噪声特性。

2. JESD204B/C系统支持

器件提供14个可配置差分输出,支持灵活分配为:

3. 高级时钟管理功能

- ?数字延迟?:支持8-1023个VCO周期的可编程延迟,步进精度达半周期(如3.2GHz时156.25ps)

- ?动态相位调整?:可在运行时微调时钟相位,最小调整量为一个时钟周期

- ?SYSREF同步?:提供全局和本地两级延迟控制,确保与设备时钟的精确时序对齐

- ?多模式操作?:支持双PLL、单PLL和纯时钟分配模式

三、典型应用设计要点

1. 电源设计建议

器件包含多个独立电源域:

- 数字电路电源(VCC5_DIG)

- PLL1电源(VCC6_PLL1)

- VCO电源(VCC1_VCO)

- PLL2电源(VCC10_PLL2)

- 时钟输出组电源(分4组)

建议采用星型拓扑供电,每组电源单独滤波。关键模拟电源推荐使用LC滤波,如10μF钽电容并联0.1μF陶瓷电容。

2. 环路滤波器设计

PLL2集成部分环路滤波器元件:

- C1i = 60pF

- R3 = 2400Ω

- C3 = 50pF

- R4 = 200Ω

- C4 = 10pF

外部只需设计C1、C2和R2。使用TI的PLLatinum Sim工具可优化设计,例如对于245.76MHz相位检测频率,典型值为:

- C1 = 220pF

- C2 = 68nF

- R2 = 120Ω

3. 时钟输出布局

输出按物理位置分为4组,各组间存在不同耦合程度:

- 组0(CLKOUT0/1/12/13):高交叉干扰

- 组1(CLKOUT2/3):中等干扰

- 组2(CLKOUT4-7):低干扰

- 组3(CLKOUT8-11):中等干扰

建议将相同频率或可容忍干扰的时钟分配在同一组,关键高频时钟优先使用组2。

四、汽车应用中的特殊考量

作为汽车级器件,LMK04714-Q1具备多项可靠性增强特性:

- ?扩展温度范围?:-40°C至+125°C全温域性能保证

- ?故障检测?:集成LOS(信号丢失)检测电路,支持自动切换和保持模式

- ?保持模式?:参考时钟丢失时,自动保持输出频率精度(典型±0.71ppm)

- ?增强ESD保护?:HBM ±2000V,CDM ±250V

在汽车雷达系统中,建议配置:

- 主时钟输入使用具有LOS检测的CLKIN0

- 备用时钟输入连接至CLKIN1

- 启用自动切换模式(CLKin_SEL_AUTO_EN=1)

- 设置合理的保持模式退出条件

五、设计支持资源

TI提供完整的开发支持工具链:

通过合理配置LMK04714-Q1的丰富功能,设计人员可构建满足最严苛汽车应用要求的时钟子系统,同时简化BOM并提高系统可靠性。

-

时钟抖动

+关注

关注

1文章

64浏览量

16208 -

高性能

+关注

关注

0文章

239浏览量

21014 -

清除器

+关注

关注

0文章

18浏览量

5998 -

双环

+关注

关注

0文章

4浏览量

6395

发布评论请先 登录

德州仪器(TI)推出最灵活高集成时钟抖动清除器/乘法器

请问LMK04610可以单端输出吗?

LMK04832-SP时钟抖动清除器

如何采用系统参考模式设计JESD204B时钟

TLK3134 具有集成时钟抖动清除器的高灵活性四通道Ser

AD9543:四路输入、10路输出、双DPLL/IEEE 1588同步器和抖动清除器

LMK04714-Q1符合JESD204B/C标准的汽车级、超低噪声、双环路时钟抖动清除器数据表

LMK04832-SEP符合JESD204B/C标准的航天级、超低噪声、双环路时钟抖动清除器数据表

LMK04368-EP符合JESD204B/C标准的超低噪声、双环路时钟抖动清除器数据表

LMK04832-SP符合JESD204B标准的航天级、超低噪声、双环路时钟抖动清除器数据表

带双环路PLL且符合JESD204B标准的LMK04832超低噪声时钟抖动清除器数据表

LMK04906带6路可编程输出的,超低噪声时钟抖动清除器和乘法器数据表

具有双环路PLL的LMK04228超低噪声且符合JESD204B标准的时钟抖动清除器数据表

高性能时钟抖动清除器LMK04714-Q1技术解析

高性能时钟抖动清除器LMK04714-Q1技术解析

评论