LMKDB 器件是一系列极低抖动的 LP-HCSL 缓冲器,支持 PCIe Gen 1 至 Gen 7,并且符合 DB2000QL 标准。这些器件提供灵活的上电顺序、故障安全输入、故障安全输出、单独的输出有源和非有源引脚、输入信号丢失 (LOS) 检测和自动输出禁用功能,以及出色的电源噪声抑制性能。

支持 1.8V 和 3.3V 电源电压。LMKDB1120,与 3.3V 相比,1.8V 电源可节省 250mW 功率。

*附件:lmkdb1104.pdf

特性

- LP-HCSL 时钟缓冲器和时钟多路复用器,支持:

- PCIe 第 1 代至第 7 代

- CC(共时钟)和 IR(独立参考)PCIe 架构

- 带或不带 SSC 的输入时钟

- 符合DB2000QL标准:

- 所有设备均符合DB2000QL规格

- LMKDB1120与DB2000QL引脚兼容

- 极低的附加抖动:

- 156.25MHz时最大12kHz至20MHz RMS附加抖动为31fs

- PCIe Gen 4 的最大附加抖动为 13fs

- PCIe Gen 5 的最大附加抖动为 5fs

- PCIe Gen 6 的 3fs 最大附加抖动

- PCIe Gen 7 的 2.1fs 最大附加抖动

- 故障安全输入

- 故障安全输出(仅限LMKDB1120FS、LMKDB1108FS和LMKDB1104FS)

- 灵活的上电顺序

- 自动输出禁用

- 单独输出使能

- SBI(边带接口)用于高速输出启用或禁用

- LOS(信号丢失)输入检测

- 85Ω 或 100Ω 输出阻抗

- 1.8V / 3.3V ± 10% 电源

- –40°C 至 105°C 环境温度

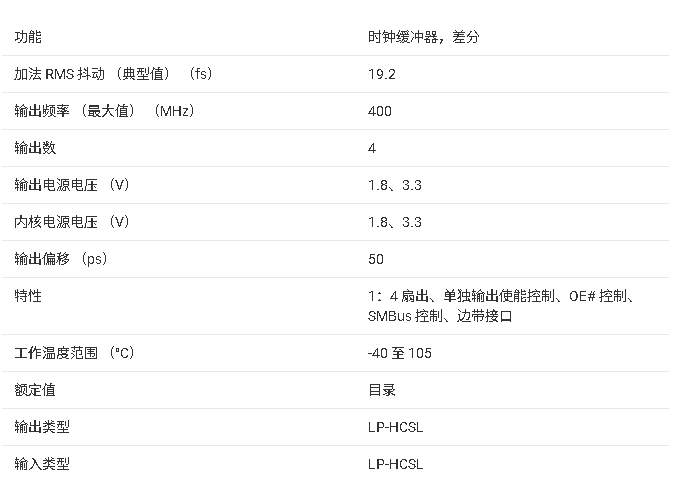

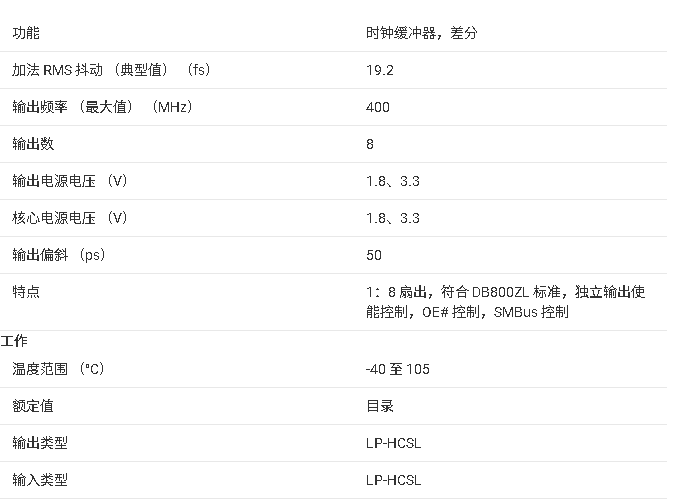

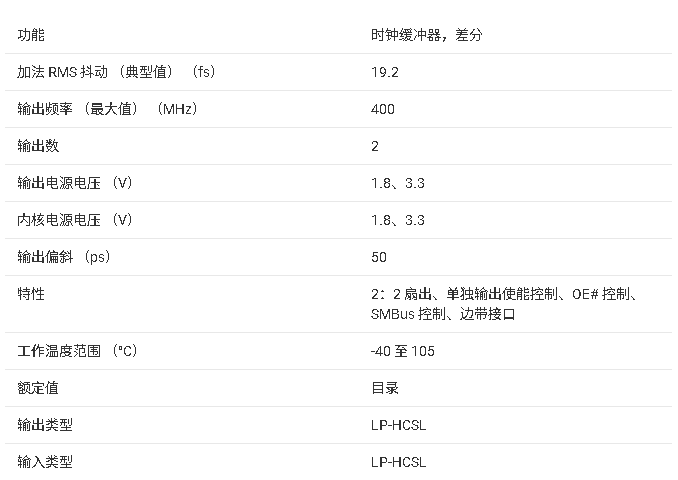

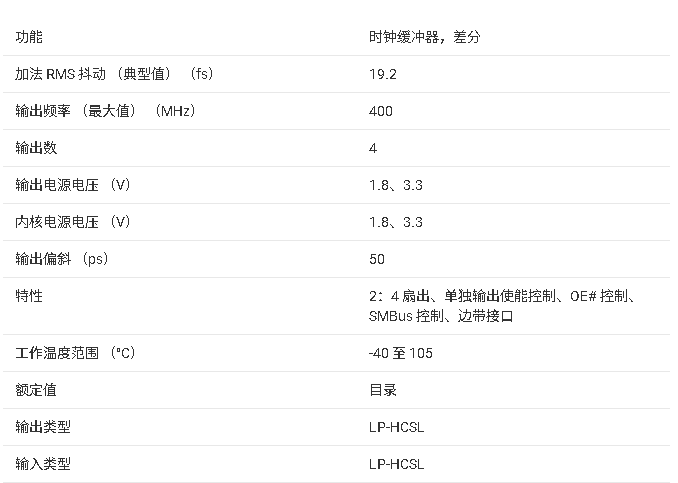

参数

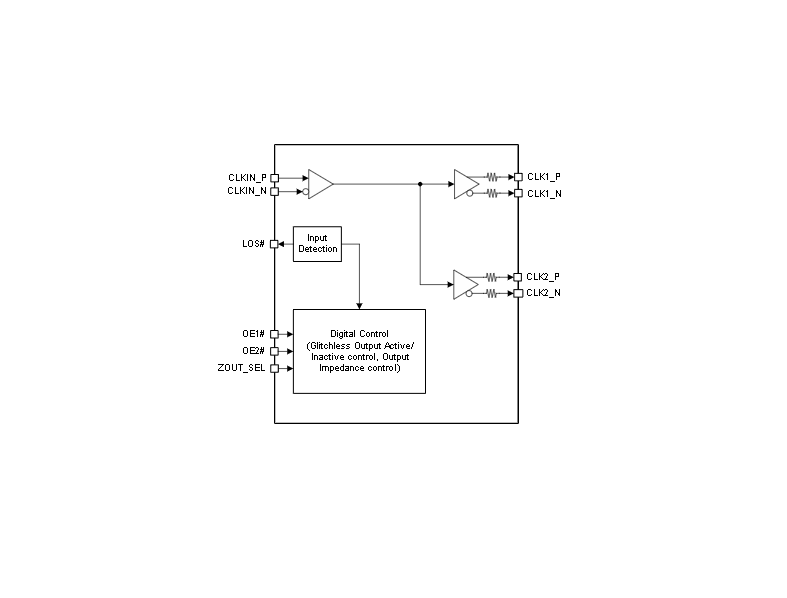

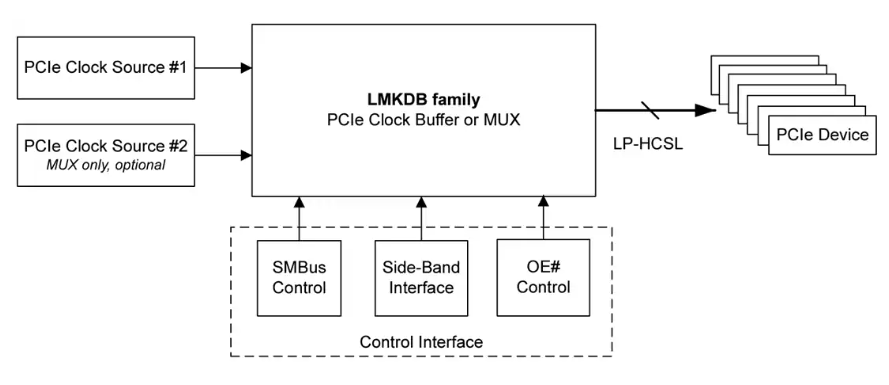

方框图

?1. 产品概述?

LMKDB11xx是德州仪器(TI)推出的超低抖动LP-HCSL时钟缓冲器家族,支持PCIe Gen 1至Gen 7标准,符合DB2000QL规范。关键特性包括:

- ?超低抖动性能?:Gen 5/6/7的RMS加性抖动低至5fs/3fs/2.1fs

- ?灵活配置?:支持85Ω或100Ω输出阻抗、1.8V/3.3V双电压供电

- ?故障保护?:输入/输出失效保护(部分型号支持输出失效保护)

- ?应用场景?:高性能计算、服务器主板、智能网卡等

?2. 核心功能?

- ?时钟分配?:提供2至20路LP-HCSL输出(依型号不同)

- ?控制接口?:支持SMBus、侧带接口(SBI)和引脚控制三种模式

- ?自动输出禁用?:检测输入时钟丢失时自动关闭输出

- ?可编程特性?:输出摆幅(600-975mV)、压摆率(16级可调)

?3. 关键参数?

| 参数 | 典型值 |

|---|---|

| 工作频率 | 1MHz至400MHz |

| 加性抖动(12k-20MHz) | 31fs @156.25MHz |

| 启动时间 | ≤0.8ms |

| 电源噪声抑制 | >85dBc(10kHz-10MHz) |

?4. 封装选项?

- ?LMKDB1102?:3×3mm VQFN-20

- ?LMKDB1104/1108?:4×4mm/5×5mm VQFN

- ?LMKDB1120?:6×6mm TLGA-80

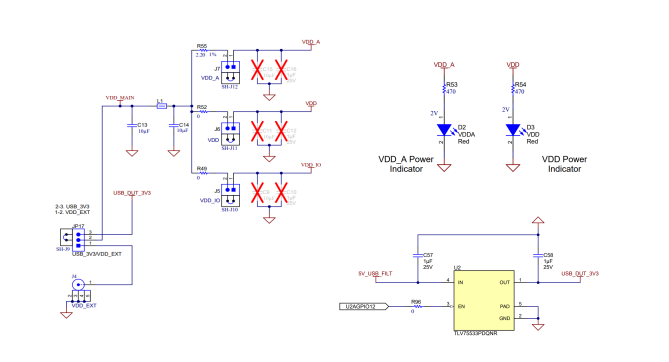

?5. 设计支持?

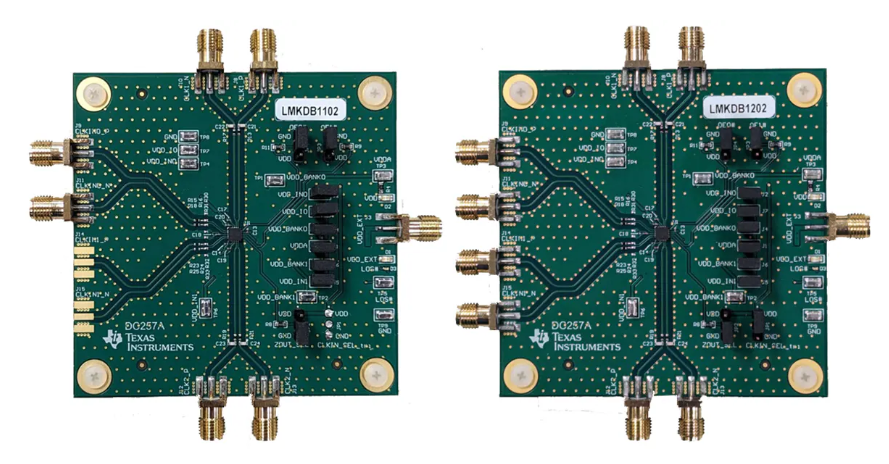

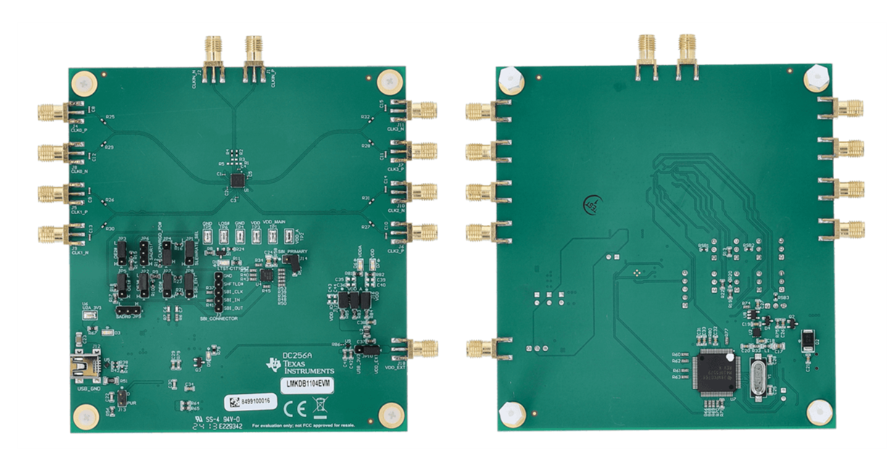

- 提供评估模块(EVM)和TICS Pro配置工具

- 布局建议:匹配85Ω/100Ω阻抗,每个电源引脚配置0.1μF去耦电容

?文档结构?

包含详细的技术规格、寄存器映射(支持SMBus编程)、时序图、热性能数据及典型应用电路。完整数据见SNAS855E Rev. August 2025版本。

-

缓冲器

+关注

关注

6文章

2100浏览量

47680 -

PCIe

+关注

关注

16文章

1384浏览量

86132 -

引脚

+关注

关注

16文章

1893浏览量

53787 -

电源噪声

+关注

关注

3文章

164浏览量

17910 -

输入信号

+关注

关注

0文章

481浏览量

12984

发布评论请先 登录

瑞萨电子推出符合PCIe Gen6标准的时钟缓冲器和多路复用器

业内首款低功耗PCI Express Gen 4缓冲器提升功耗及性能标杆

核芯互联推出符合DB2000QL及PCIe Gen5和Gen 6标准的低抖动时钟缓冲器CLB2000

核芯互联推出全新20路LP-HCSL差分时钟缓冲器CLB2000

LMKDB1120和LMKDB1108超低抖动PCIe第1代到第6代LP-HCSL时钟缓冲器数据表

CDCDB800/803超低附加抖动、8路输出PCIe Gen1至Gen5时钟缓冲器

Texas Instruments LMKDB1x02EVM 评估模块数据手册

Texas Instruments LMKDB1104EVM评估模块数据手册

Texas Instruments LMKDB1204EVM 评估模块(EVM)数据手册

LMKDB1108 用于 PCIe Gen 1 至 Gen 7 的 8 输出 LP-HCSL 时钟缓冲器技术手册

LMKDB1104 用于 PCIe Gen 1 至 Gen 7 的 4 输出 LP-HCSL 时钟缓冲器技术手册

LMKDB1104 用于 PCIe Gen 1 至 Gen 7 的 4 输出 LP-HCSL 时钟缓冲器技术手册

评论