布局

全局布局

在全局布局中,尤其是在 PSIP 中,不同的优化中会发生一些复制,包括:

关键单元优化:适用于含负载数 <=30 的关键信号线的复制

扇出优化:适用于含负载数大于 30 且小于等于 100 的关键信号线的复制

超高扇出优化:对驱动高扇出信号线(扇出 > 1000,裕量 < 2.0 ns)的寄存器进行复制。

按 SLR 进行复制优化:对驱动其他 SLR 内的关键负载的 FF 进行复制

动态/静态区域接口信号线复制:对 DFX 设计的每个静态区域/动态区域的驱动程序进行复制

注释:在 Versal 默认流程和 Explore 流程中已停用

除上述优化外,还可以通过下列属性(按优先顺序列示)来影响高扇出信号线的初始布局:

MAX_FANOUT:该属性会将每个驱动程序的扇出限制告知工具,并通过指示布局器了解扇出限制来指引该工具对高扇出的负载进行分配。此属性可同时应用于 FF 与 LUT 驱动程序。当 MAX_FANOUT 值小于约束的信号线的实际扇出时,将对该信号线进行寄存器复制评估。值得注意的是,仅当时序会得到改善的情况下,才会发生优化。

MAX_FANOUT_MODE:该属性会指定强制执行扇出限制的方式。您可基于物理器件属性(CLOCK REGION、SLR、MACRO)来强制执行复制。如果设置该属性,那么会将高扇出信号线的负载集中到同一个 SLR 中或采用您为该属性设置的任意值。支持该属性的宏 (MACRO) 包括:块 RAM、UltraRAM 和 DSP。

FORCE_MAX_FANOUT:该属性会被应用于特定信号线,以限制复制优化后信号线的最大物理扇出。借助该属性,即可在 PSIP 期间强制进行复制优化,并且该工具不考虑时序因素。

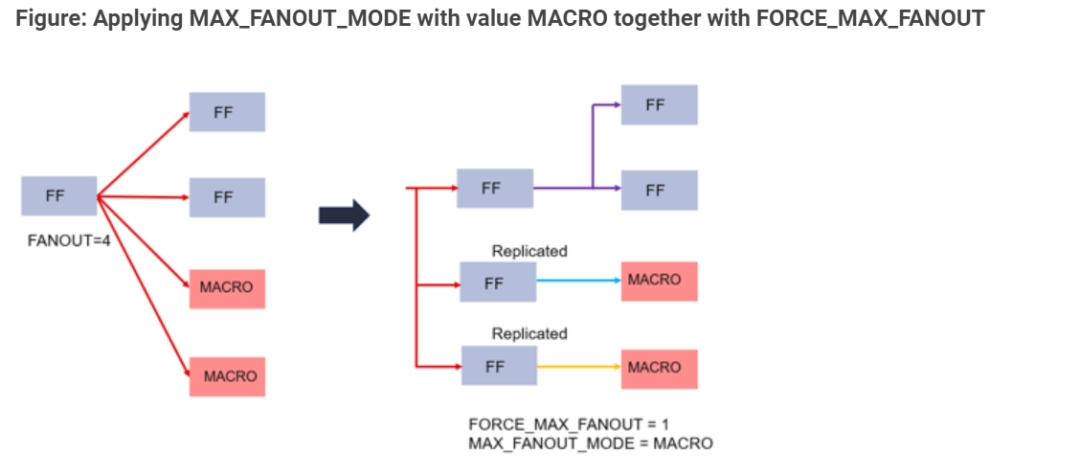

图 9:在此示例中,将 MAX_FANOUT_MODE 属性设置为 MACRO 并将 FORCE_MAX_FANOUT 设置为 1

针对每项 MACRO 负载,驱动程序均已执行复制。请注意,MAX_FANOUT_MODE 优先于 FORCE_MAX_FANOUT 属性。

布局后优化

以下操作在布局后流程中完成:

BUFG 插入阶段——在布局后操作期间还包含 BUFG 插入阶段,在此期间,工具会将高扇出信号线推广到全局布线。在此阶段,布局器会自动将高扇出信号线布线到任何可用的全局布线走线上。满足以下条件的信号线都会被纳入插入的考量范围:Versal 中扇出 > 10,000 的信号线,以及 UltraScale/UltraScale+ 中扇出 > 1,000 并且所驱动的控制信号裕量大于 1 ns 的信号线。这是时序驱动的插入,仅当插入有助于改善时序时才会发生。

在 place_design 命令中使用 -no_bufg_opt 即可关闭此优化。

物理优化

在物理优化 (phys_opt_design) 期间,有若干优化可用于应对高扇出信号线,其中部分优化默认已启用:

高扇出优化

在该流程中默认启用此项优化。针对此优化,若高扇出信号线所含负时序裕量在 WNS 的某一百分比范围内,则会被纳入复制的考量范畴。仅当复制有助于改善时序时,才会发生复制。

-force_replication_on_nets

“force replication on nets”(在信号线上强制复制)选项可用于强制对任意指定信号线进行驱动程序复制,与该信号线的时序裕量无关。如果您在布线后注意到高扇出信号线变得非常关键,那么此优化可能很有用。您可以在该特定信号线上再次运行物理优化并强制复制,以查看是否有所帮助。

-directive AggressiveFanoutOpt

物理优化中另有一个选项是 AggressiveFanoutOpt 指令。在某些情况下,物理优化无法解决所有关键的高扇出信号线。因此,建议您搭配该指令重新运行物理优化,以便进行更为激进的优化。

-lut_opt

该选项旨在通过移动或复制 LUT 来减少路径延迟。

如果您熟悉先前被称为“High fanout optimization”(高扇出优化)和“Very high Fanout optimization”(超高扇出优化)的旧优化,在最新架构中不再支持这些旧优化。而是改为采用 -interconnect_retime (Vivado 2022.1+) 选项和 -lut_opt (Vivado 2023.1+) 选项来代替这些优化。

-iphys_opt_design

此命令描述了由 phys_opt 执行的特定优化,如果您在 write_iphys_opt_tcl 中包含 -place,那么此命令也可以写出由布局完成的优化。它可在不同阶段用于应用优化。例如,该命令允许在布局前设计上执行通常在 phys_opt 之后执行的各项优化。换言之,该命令可帮助您通过 Tcl 复用/重复优化。

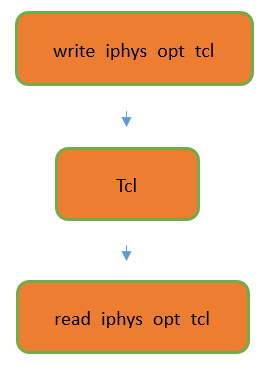

图 10:此流程图显示了 iphys_opt 命令的正常使用顺序

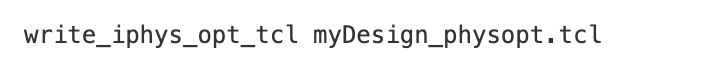

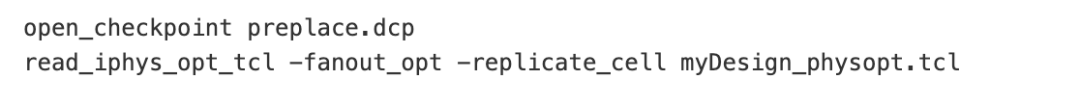

示例:

基线运行轮次:

复用 iphys_opt_tcl 的轮次:

请参阅 UG835 以了解有关 iphys_opt_design、write_iphys_opt_tcl 和 read_iphys_opt_tcl 的更多信息:

https://docs.amd.com/r/en-US/ug835-vivado-tcl-commands/write_iphys_opt_tcl

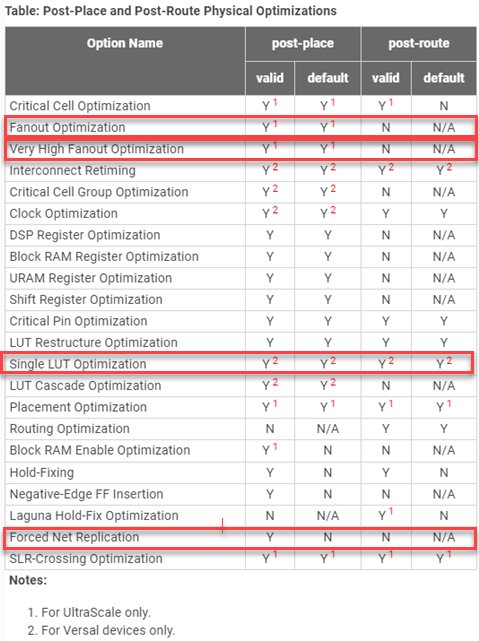

物理优化期间执行的优化取决于运行物理优化的实现阶段。根据物理优化是在布局后还是布线后运行的,部分其他可用优化(默认优化除外)可能会发生更改。默认如果在布局后运行物理优化,则会执行“Fanout optimization”(扇出优化)和“Very High Fanout Optimization”(超高扇出优化),但布线后运行物理优化时,这两个选项则不可用。

如需了解更多相关信息,请参阅下表:

图 11:布局后和布线后物理优化可用的选项

-

寄存器

+关注

关注

31文章

5460浏览量

125718 -

信号线

+关注

关注

2文章

183浏览量

21989 -

时序

+关注

关注

5文章

401浏览量

38233

原文标题:开发者分享|高扇出信号线优化技巧(下)

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Altium Designer信号线束的使用

电源线的直径可以和信号线的直径相同吗?

信号线是什么线

使用总线别名(Bus Alias)实现信号线束的功能

差分信号线的选择与处理

信号线和光纤线的区别是什么

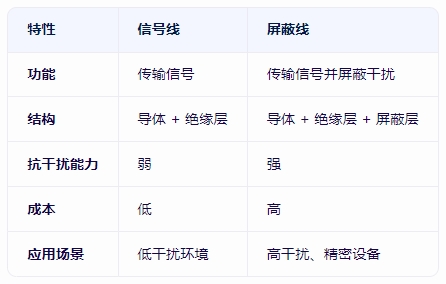

信号线和屏蔽线有什么区别

高扇出信号线优化技巧(下)

高扇出信号线优化技巧(下)

评论