文章来源:学习那些事

原文作者:小陈婆婆

本文将介绍WLCSP在3D维度上的可行路径。

晶圆级芯片尺寸封装(WLCSP)因其“裸片即封装”的极致尺寸与成本优势,已成为移动、可穿戴及 IoT 终端中低 I/O(< 400 bump)、小面积(≤ 6 mm × 6 mm)器件的首选。然而,当系统级集成需求把 3D 封装/3D IC 技术推向 WLCSP 时,传统方案——引线键合堆叠、PoP、TSV 硅通孔——因工艺窗口、CTE 失配及成本敏感性而显著受限。

本文将介绍WLCSP在3D维度上的可行路径:从早期 Shellcase 侧壁 RDL 的 CIS/MEMS 专用 3D WLCSP,到利用 TMV 的扇出型 PoP;从无需 TSV 的铜柱-微凸点倒装堆叠,到嵌入式 WLCSP 在 PCB 级实现的异构 3D 集成,分述如下:

晶圆级芯片尺寸封装概况

3D MEMS和传感器WLCSP

嵌入式WLCSP

晶圆级3D集成

在半导体封装领域,晶圆级芯片规模封装(WLCSP)凭借其独特的工艺特性,在三维集成技术路径的选择上呈现出显著的差异化特征。作为唯一直接以裸芯片形态实现集成电路封装的解决方案,WLCSP的技术演进始终围绕其全晶圆工艺基础展开,这种工艺特性决定了其三维集成方案必须与常规3D封装及3D IC技术形成策略性区分。

从工艺本质来看,WLCSP依托全晶圆级加工流程,通过阵列式凸块构造实现芯片与基板的互连,其应用边界天然受限于低I/O密度(通常小于400个凸点)和小型化尺寸(典型封装体不超过6mm×6mm)。这种物理限制使得传统3D封装中的引线键合芯片堆叠技术仅在特定场景下具备可行性——当WLCSP芯片与模块基板进行共封装时,引线键合组件需以并排布局方式实现功能整合,而非垂直堆叠。这种设计选择既规避了WLCSP在Z轴方向的空间局限,又维持了其作为独立封装单元的工艺完整性。

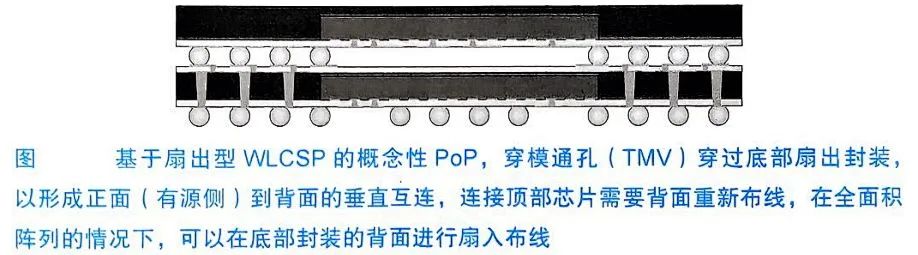

在三维集成创新领域,扇出型WLCSP通过模具通孔(TMV)技术开辟了新的可能性。基于TMV的堆叠封装(PoP)架构被证明是扇出型WLCSP的增值选项,其核心价值在于突破了传统扇入型WLCSP的尺寸约束。通过重构晶圆工艺扩展有效封装区域,扇出型方案将热机械应力控制水平提升至接近BGA基板封装标准,这使得早期应用于BGA领域的三维概念(如下图所示的TMV-PoP结构)得以技术移植与优化。

值得注意的是,这种创新路径并未简单复制既有3D封装方案,而是结合扇出型WLCSP的低成本优势和TMV的高密度互连特性,形成了具有市场竞争力的垂直集成解决方案。

反观硅通孔(TSV)技术,其在通用扇入型WLCSP中的适用性持续受限。尽管TSV在2.5D/3D IC领域已实现商业化突破,但WLCSP对额外空间占用的敏感性和终端市场的成本容忍度,使得这项技术难以获得广泛接受。

目前扇出型WLCSP正在引领三维集成技术的革新方向。通过结合TMV与重布线层(RDL)工艺,该技术已成功应用于先进移动终端的射频前端模块,实现功率放大器与滤波器的三维共封装。这种增长动力主要源自消费电子对轻薄化需求的持续升级,以及汽车电子领域对高可靠性三维封装方案的迫切需求。

值得关注的是,MEMS传感器与WLCSP的融合正在催生新的三维集成范式。通过在扇出型WLCSP中嵌入压力传感单元,实现芯片级环境感知功能整合,这种创新方案已在可穿戴设备领域完成概念验证。与此同时,一些领先厂商正在开发基于WLCSP的异质集成技术,将逻辑芯片与存储单元通过晶圆级键合实现三维堆叠,这为边缘计算设备的小型化提供了全新解决方案。

从技术演进路径分析,WLCSP的三维集成方向正逐步形成两大分支:其一聚焦于扇入型架构的垂直功能增强,通过优化凸块布局和材料体系提升I/O密度;其二则依托扇出型工艺突破物理限制,构建多芯片三维集成系统。这种双轨发展策略既保持了WLCSP的成本优势,又通过技术创新拓展其应用边界,为半导体封装领域提供了独特的价值主张。

3D MEMS和传感器WLCSP

在半导体封装技术的演进历程中,3D MEMS与传感器晶圆级芯片规模封装(WLCSP)的融合创新始终占据独特地位。其技术的核心在于实现芯片有源面与背面的高效互连。其工艺通过倾斜芯片/封装侧壁的再布线设计,在芯片边缘暴露触点并重构电气路径,最终在封装背面形成高密度焊球阵列。

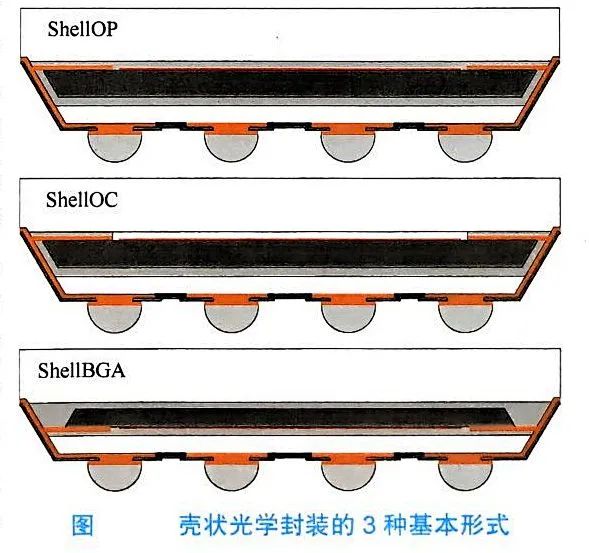

这种架构在CMOS图像传感器封装中衍生出三种典型形态:ShellOP作为基础光学封装,提供全边缘布线与传感区域保护;ShellOC通过引入光学腔体设计,优化光接收效率;而ShellBGA则专为背照式(BSI)传感器开发,通过消除芯片表面金属层的散射效应,显著提升微光环境下的成像性能。

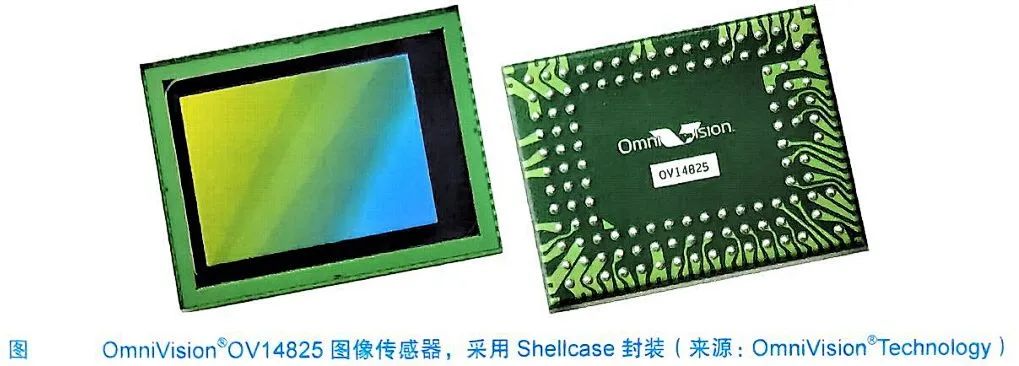

以OmniVision 2010年推出的OV14825传感器为例,该器件采用116针芯片级封装,依托Shellcase的边缘互连技术,在4416×3312像素的BSI架构上实现了15帧/秒全分辨率输出与60帧/秒高清视频录制,其500μm级的封装厚度完美适配移动设备对轻薄化的严苛要求。

技术迭代方面,Shellcase工艺的演进呈现出两条并行路径:传统工艺通过优化玻璃载体使用与300mm晶圆适配,持续降低封装高度;而ShellcaseRMVP方案则引入TSV技术,构建垂直互连通道。相较于边缘布线方案,TSV架构突破了焊盘尺寸与间距的限制,允许更窄的切割道设计,从而提升晶圆利用率并降低单位成本。这种创新在2018年后的高端图像传感器市场中尤为显著,多家头部厂商开始采用TSV-WLCSP混合架构,将封装厚度压缩至300μm以下,同时保持光学性能的稳定性。

在MEMS领域,3D WLCSP的价值体现更为本征。由于MEMS器件依赖深反应离子刻蚀(DRIE)形成三维机械结构,传统封装工艺难以兼顾结构保护与电气互连。3D MEMS WLCSP通过晶圆对晶圆(CoW)或芯片对晶圆(WoW)的堆叠方式,将ASIC控制芯片与MEMS传感单元进行面对面键合,结合倒装芯片技术与微型凸点互连,实现了信号处理与感知功能的垂直集成。此类方案在惯性导航、压力传感等应用中已实现商业化,例如某国际大厂2022年推出的六轴MEMS传感器,通过3D WLCSP将ASIC与MEMS芯片堆叠,封装尺寸较传统方案缩小40%,同时功耗降低25%。

尽管通用型WLCSP的3D堆叠仍面临成本敏感性问题,但特定领域的创新持续涌现。

如上图所示的3D WLCSP概念图,通过集成铜柱凸点、前侧模塑成型与再布线技术,在无需TSV的情况下构建多层互连结构。这种方案在射频前端模块(RF Front-End Module)中已获得应用,将功率放大器与滤波器进行三维共封装,有效缩短信号传输路径并减少寄生效应。

嵌入式WLCSP

在半导体封装技术的创新版图中,嵌入式晶圆级芯片规模封装(WLCSP)以其独特的工艺路径和应用价值,成为系统级封装(SiP)领域的重要分支。不同于依赖晶圆级处理的3D WLCSP,嵌入式方案通过PCB面板级工艺实现芯片与基板的深度集成,其技术本质在于将WLCSP器件直接嵌入印刷电路板(PCB)内部,构建紧凑且高可靠性的电子模块。

嵌入式WLCSP的技术可行性源于其与PCB工艺的天然适配性。首先,WLCSP的细间距凸点阵列(通常≤0.5mm)与PCB激光通孔工艺的精度范围高度匹配,确保电气互连的精准对位;其次,WLCSP的铜基底金属化层(UBM)直径普遍超过200μm,这一尺寸恰好满足激光钻孔设备对接触焊盘的最小加工要求,同时铜材质与PCB化学镀铜/电解镀铜工艺的兼容性,避免了金属化层的额外处理步骤;再者,WLCSP的背面研磨技术已非常成熟,通过控制研磨深度可将芯片厚度降至50μm以上,配合标准晶圆切割工艺,可轻松实现嵌入式模块的厚度控制。这些工艺特性的协同作用,使得嵌入式WLCSP在硅侧集成过程中展现出极高的技术成熟度。

从应用价值来看,嵌入式方案的核心优势体现在空间效率与可靠性的双重提升。以USB-OTG升压调节器模块为例,通过将WLCSP芯片嵌入PCB基板并整合表面贴装无源元件,模块整体尺寸缩减超过44%,且无需改变封装高度或影响散热性能。这种空间优化在移动终端、可穿戴设备等对体积敏感的领域尤为关键。可靠性方面,嵌入式架构通过两种机制显著改善了热机械应力表现:其一,芯片嵌入后模块基板与PCB的CTE(热膨胀系数)差异被大幅削弱,焊点承受的应力水平低于传统表面贴装方案;其二,硅芯片与PCB的物理分离距离增加,降低了CTE失配导致的界面应变。实验数据显示,嵌入式模块在板级跌落测试和TMCL(热循环)测试中的故障率较传统方案降低30%以上。

尽管嵌入式WLCSP具备显著优势,其技术适用性仍受限于具体场景。由于嵌入过程会占用PCB内部空间,原本用于穿层通孔(Via)的区域被压缩,可能对3D模块的垂直互连设计构成挑战。此外,虽然模块内的埋入铜层和通孔结构可形成有效的热传导路径,但在高功耗应用(如汽车功率模块)中,仍需结合外部散热方案以确保热稳定性。不过,随着PCB基板材料的迭代(如引入高导热树脂)和激光钻孔精度的提升(最小孔径≤50μm),嵌入式WLCSP正在向更广泛的应用领域渗透。

目前,嵌入式WLCSP与先进封装技术的融合正在加速。2024年,某国际半导体厂商推出基于嵌入式WLCSP的5G射频前端模块,通过将功率放大器(PA)芯片嵌入PCB并集成滤波器元件,实现了信号路径缩短30%的同时,模块厚度控制在1.2mm以内。在汽车电子领域,嵌入式方案已被应用于车载摄像头模块,将CMOS图像传感器嵌入柔性PCB基板,结合TSV技术实现光学防抖(OIS)功能的三维集成。值得关注的是,2025年台积电推出的嵌入式WLCSP-CoWoS混合架构,通过将HBM内存芯片嵌入有机基板并与逻辑芯片进行2.5D互连,将AI加速卡的带宽密度提升至2TB/s,这一创新预示着嵌入式技术在高性能计算领域的巨大潜力。

从工艺演进趋势分析,嵌入式WLCSP正朝着两个方向深化发展:其一,通过超薄芯片处理技术(厚度≤30μm)和纳米级激光钻孔(孔径<30μm)提升集成密度;其二,结合3D打印导电胶和临时键合技术,实现异质材料(如硅与玻璃)的嵌入式集成。这些创新不仅将拓展嵌入式方案的应用边界,更可能重新定义PCB作为载体与功能单元的双重角色,推动电子系统向更小型化、更高性能的方向演进。

-

芯片

+关注

关注

460文章

52821浏览量

445673 -

晶圆

+关注

关注

53文章

5235浏览量

130374 -

封装

+关注

关注

128文章

8868浏览量

146092 -

集成技术

+关注

关注

0文章

29浏览量

11093

原文标题:小到极致,反见天地:WLCSP三维集成技术

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

三维逆向工程的成果及应用案例

三维触控技术突破“二向箔”的束缚

三维快速建模技术与三维扫描建模的应用

广西扫描服务三维检测三维扫描仪

三维设计应用案例

上海黄浦三维媒体动画技术

基于LTCC技术的三维集成微波组件

三维数字化集成检测系统实现关键技术分析

详解WLCSP三维集成技术

详解WLCSP三维集成技术

评论