概述

高扇出信号线 (HFN) 是具有大量负载的信号线。作为用户,您可能遇到过高扇出信号线相关问题,因为将所有负载都连接到 HFN 的驱动程序需要使用大量布线资源,并有可能导致布线拥塞。鉴于负载分散,导致进一步增大信号线延迟,因此在高扇出信号线上也可能难以满足时序。

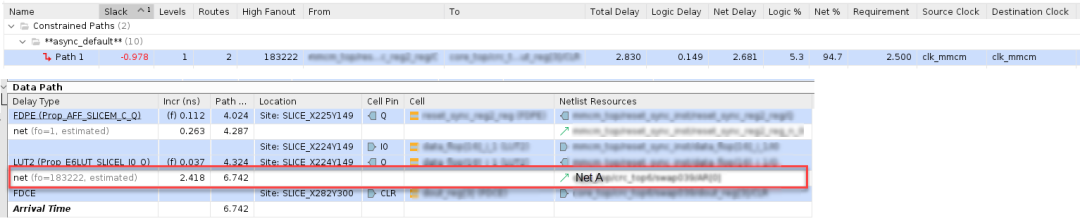

图 1:违例达 0.978 ns 的时序路径

通过观察数据路径即可发现,高扇出信号线 Net A 是由 LUT 驱动,它造成了 2.418 ns 延迟。优化此高扇出信号线有助于解决此时序路径问题。

如何查询高扇出信号线

您可使用 report_high_fanout_nets 命令来识别设计中的非时钟高扇出信号线。此命令有多个选项可用于打印有关高扇出信号线的详细信息,包括驱动程序信息、时序信息 (-timing) 和负载位置信息 (-slr)。如需获取这些选项的完整列表,请参阅 UG906:

https://docs.amd.com/r/zh-CN/ug906-vivado-design-analysis

如果您的设计中具有导致 QoR 问题的高扇出信号线,那么强烈建议您在实现的中间步骤转储该报告。

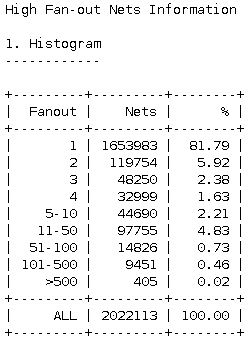

图 2:“report_high_fanout_nets -histogram”的结果

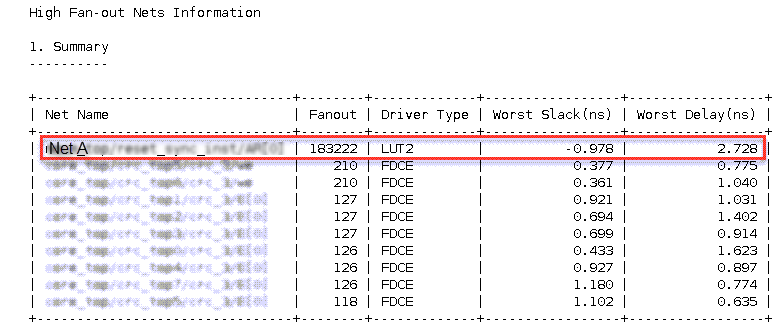

图 3:“report_high_fanout_nets –timing”的结果

查询高扇出信号线的另一种方法是采用以下表达式:

set fanout [expr {[get_property FLAT_PIN_COUNT [get_nets $Net_A] -1 }]

如何在不同实现阶段应对高扇出信号线

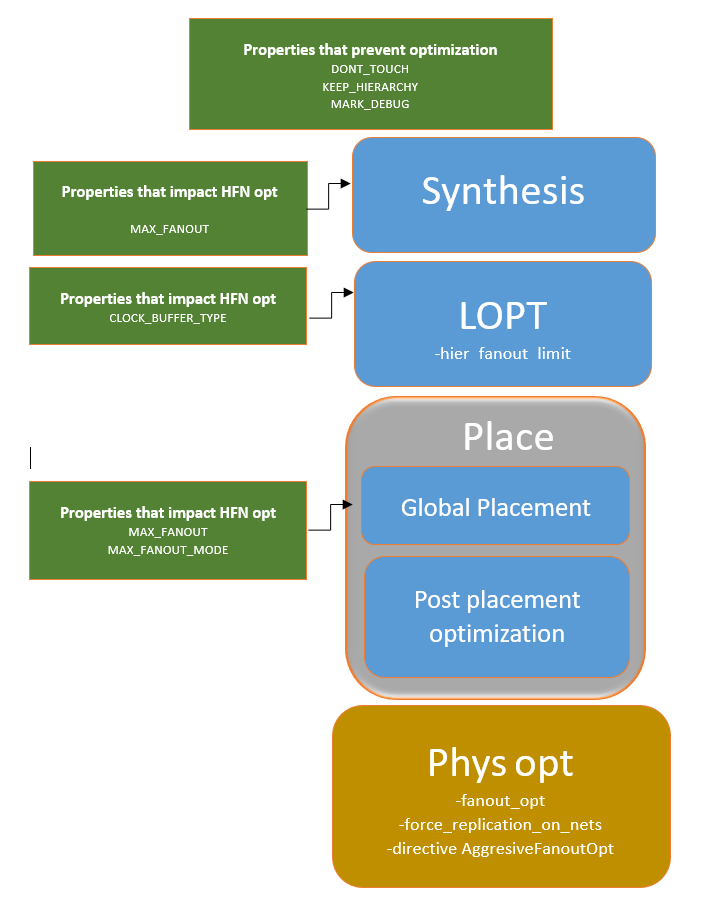

图 4:此图呈现了在实现的不同部分中影响高扇出信号线优化的命令选项和属性。

DON'T_TOUCH 属性、KEEP HIERARCHY 属性和 MARK_DEBUG 属性会阻止执行任何 HFN 优化。其他属性包括 MAX_FANOUT、CLOCK_BUFFER_TYPE 和 MAX_FANOUT_MODE,这些属性全都会影响 HFN 优化。

综合

MAX_FANOUT

在综合期间,您可使用 MAX_FANOUT 属性来强制复制寄存器。该属性用于控制发生寄存器复制的时机。如果某条信号线的扇出大于 MAX_FANOUT 值,就会考虑对该寄存器进行复制。请注意,无论时序如何,都会应用该属性,因此务必谨慎使用,过量使用会因过度复制而导致更多问题(当 HFN 位于寄存器控制信号上时尤其如此)。建议在综合期间慎用该属性。

set_property MAX_FANOUT [get_nets -hier ]

建议不要在驱动程序与负载之间设置额外的组合逻辑,否则会妨碍某些复制优化操作。

有些属性可能会阻碍执行此类有益的复制操作,其中包括:

DONT_TOUCH:阻止在设计元素上发生任何修改或复制

KEEP_HIERARCHY:指示工具在复制期间保留层级(如果 HFN 驱动程序及其负载位于同一模块内,则会阻止复制)

MARK_DEBUG:禁止呈现某条信号线以供调试

如需了解有关这些属性的更多详情,请参阅 UG901:

https://docs.amd.com/r/en-US/ug901-vivado-synthesis/KEEP_HIERARCHY

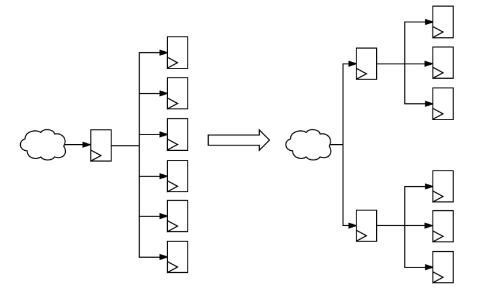

以下是一个简单的示例。如果该信号线的 MAX_FANOUT 属性设为 3,则该信号线的驱动程序必须复制 2 次,如下所示:

图 5:通过复制源寄存器来减少扇出的简单示例。

同样,如果有个源,其中有 10,000 负载分布在整个设计中,并且您通过将 MAX_FANOUT 设为 1,000 来限制扇出,那么,该工具会将该源复制 10 次,然后为复制的每个源分配 1,000 负载。

逻辑优化

在逻辑优化 (opt_design) 期间,有多种间接的方式可用于控制高扇出信号线。以下部分选项可能有用:

BUFG 插入

默认在逻辑优化中,会在满足某些要求的高扇出控制信号线上插入 BUFG 或 BUFG_FABRIC 时钟缓冲器(在 Versal 架构中)。这是很有效的,因为全局时钟布线资源可以减少互连结构布线上的拥塞,从而帮助缓解时序问题。

非时钟信号线的扇出必须大于 25k 才符合此条件。 使用 BUFG 插入时,该工具较为保守,对于 Ultrascale+/Versal,限制是 24 个 BUFG(此限制不包括 BUFG_GT)

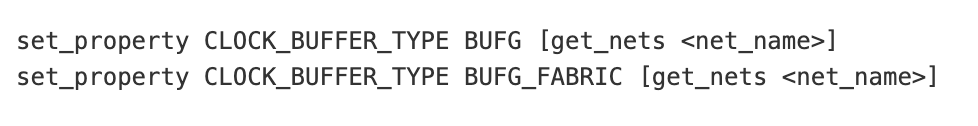

用户指定的 BUFG 插入

如果信号线没有插入 BUFG,您可以通过 CLOCK_BUFFER_TYPE 属性强制执行 BUFG 插入。该工具会为任何指定的信号线添加 BUFG/BUFG_FABRIC,并且不会将其计入先前提及的限值 24,前提是有走线可用。

BUFG 负载拆分

在某些情况下,插入 BUFG 的过程中会拆分时钟网络,使其分别驱动组合负载与时序负载。发生拆分时,时序负载由 BUFG 驱动,组合负载则由原始驱动程序来驱动。针对 opt_design 插入的 BUFG 和用户插入的 BUFG 都会发生此拆分操作。当 BUFG 输出信号线驱动组合负载与非时钟时序负载(例如,高扇出复位)时,预计会发生负载拆分。

层级复制

用户还可通过该工具使用 -hier_fanout_limit 选项根据高扇出信号线的逻辑层级来复制该信号线的驱动程序。该工具会在层级内查找,如果发现驱动程序所驱动的负载超出指定限值,那么该工具就会复制驱动程序。

这有助于缓解高扇出信号线所导致的拥塞。这是一种基于规则的复制,无法感知时序,因此建议谨慎使用。

注释:为 -hier_fanout_limit 选项指定的最小限值为 512。

图 6:扇出为 60,000 的信号线

当 -hier_fanout_limit 设为 1000 时,HFN 驱动程序会复制 59 次,每次复制的驱动程序都会驱动 1000 个负载。

您可使用以下命令实现此目的:

opt_design -hier_fanout_limit 1000

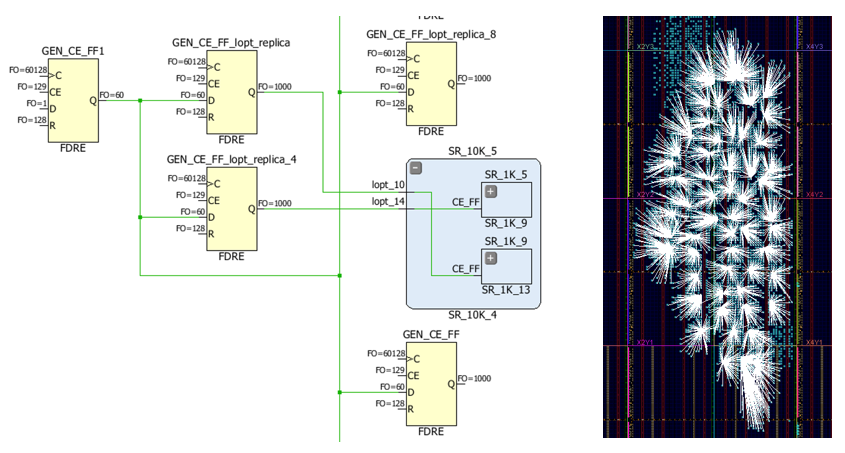

了解对某个设计要素进行了哪些优化是很有帮助的。OPT_MODIFIED 属性会明示对设计要素执行了哪些优化(按优化的执行顺序)。同样,OPT_SKIPPED 会显示设计要素上跳过了哪些优化。在某些情况下,DONT_TOUCH 或类似属性可能阻止优化。建议搜索日志,查找有关跳过某一项优化的具体原因的更多信息。与前述属性类似,PHYS_OPT_MODIFIED 与 PHYS_OPT_SKIPPED 是用于物理优化的等效属性。

图 7:含 opt_design 选项与对应 OPT_MODIFIED 值的表

如果您在 opt_design 中遇到因使用 hier_fanout_limit 选项而导致复制的驱动程序,那么您会发现 OPT_MODIFIED 属性与 HIER_FANOUT_LIMIT 相等。

-

负载

+关注

关注

2文章

628浏览量

35419 -

寄存器

+关注

关注

31文章

5460浏览量

125718 -

信号线

+关注

关注

2文章

183浏览量

21989 -

时序

+关注

关注

5文章

401浏览量

38233

原文标题:开发者分享|高扇出信号线优化技巧(上)

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高扇出信号线优化技巧(下)

如何在模拟电路PCB板上做好信号线的布局走线?

音频信号线的工作原理和制作要求

Altium Designer信号线束的使用

信号线是什么线

差分信号线的选择与处理

信号线和光纤线的区别是什么

信号线和屏蔽线有什么区别

高扇出信号线优化技巧(上)

高扇出信号线优化技巧(上)

评论