半导体外延和薄膜沉积是两种密切相关但又有显著区别的技术。以下是它们的主要差异:

定义与目标

半导体外延

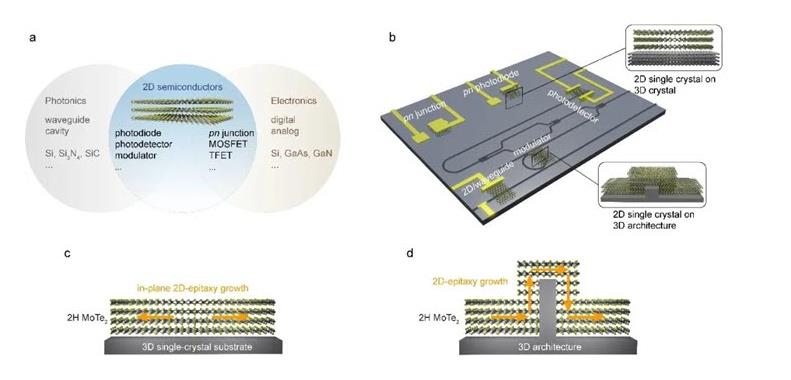

- 核心特征:在单晶衬底上生长一层具有相同或相似晶格结构的单晶薄膜(外延层),强调晶体结构的连续性和匹配性36;

- 目的:通过精确控制材料的原子级排列,改善电学性能、减少缺陷,并为高性能器件提供基础结构。例如,硅基集成电路中的应变硅技术可提升电子迁移率4。

薄膜沉积

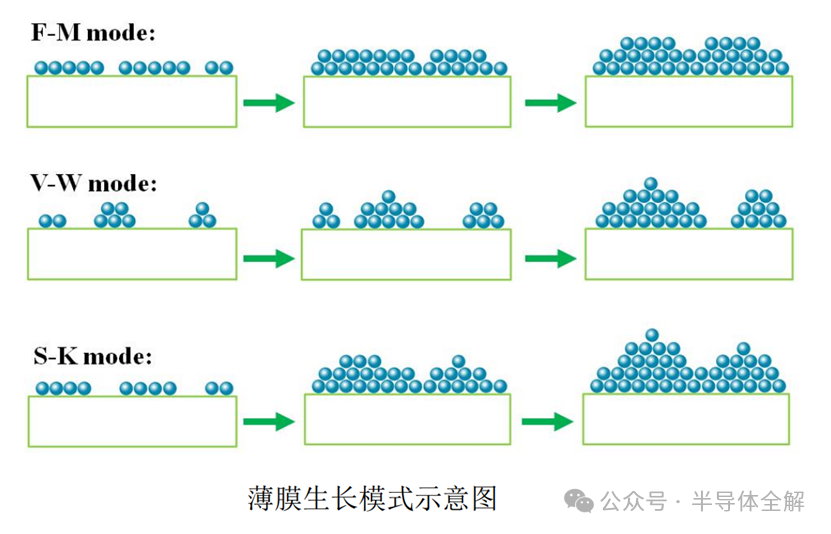

- 核心特征:在基底表面形成功能性薄膜,可以是多晶、非晶或无序结构,不严格要求与衬底的晶格匹配78;

- 目的:实现特定功能(如导电、绝缘、光学反射等),适用于更广泛的材料体系和应用场景。

工艺原理与方法

半导体外延

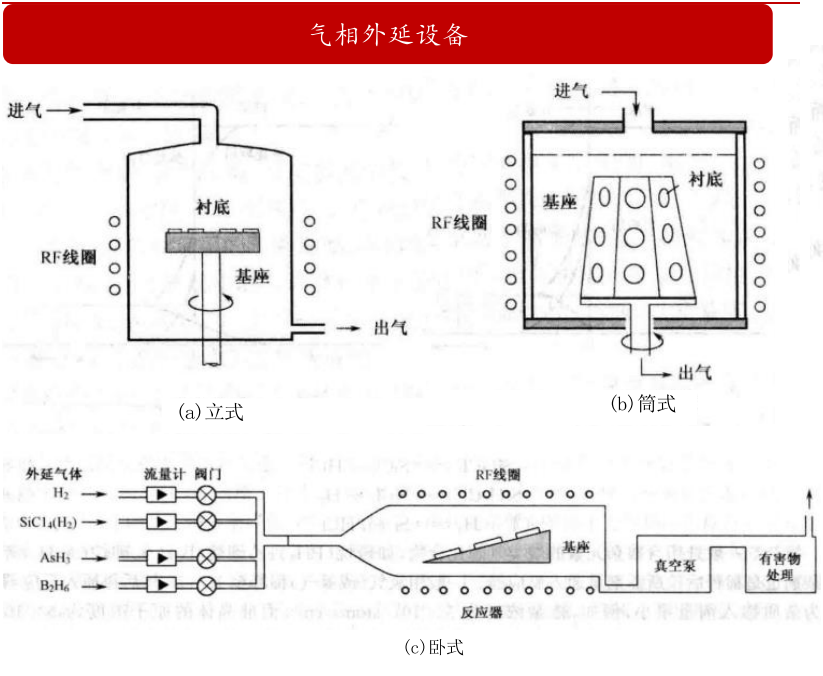

- 典型技术:分子束外延(MBE)、金属有机化学气相沉积(MOCVD)、气相外延(VPE)等6;

- 关键条件:高温环境(如SiC外延需1600~1660℃)、真空系统支持原位监测,以及严格的晶格匹配控制以确保单晶生长23;

- 特点:注重晶体质量,常用于制造晶体管、激光器等高精度器件。

薄膜沉积

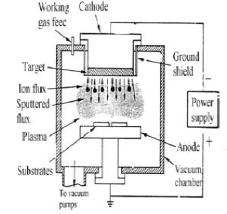

- 分类:包括物理气相沉积(PVD)、化学气相沉积(CVD)、原子层沉积(ALD)等79;

- PVD(如溅射、蒸发):依赖物理过程,适合金属或合金薄膜;

- CVD(如LPCVD、PECVD):通过化学反应生成薄膜,可调控成分和厚度;

- ALD:以单原子层逐次沉积,实现亚纳米级精度控制9;

- 灵活性:允许使用多类材料,且对衬底尺寸和形状的限制较小。

材料与结构特性

半导体外延

- 材料类型:以同质外延为主,也可进行异质外延;

- 结构特点:外延层与衬底保持严格的晶格连续性,缺陷密度低,适用于高可靠性器件3;

- 应用实例:CMOS源漏区的选择性Si/SiGe外延可降低电阻并引入应力优化性能4。

薄膜沉积

- 材料多样性:涵盖金属、氧化物、氮化物等多种体系;

- 结构多样性:薄膜可以是多晶、非晶或多层堆叠,设计自由度高;

- 典型用途:如栅极介电层、金属互连线、钝化层等。

设备与工艺参数

半导体外延

- 设备配置:高真空反应室、原位表征工具(如RHEED),背景真空度可达10??mbar2;

- 生长参数:侧重于衬底温度、气体流量比和反应动力学平衡,需避免气相成核导致的多晶化2。

薄膜沉积

- 设备适配性:根据需求选择批量式(管式)或空间型(板式)设备,支持大面积均匀镀膜;

- 工艺调控:通过调节沉积速率、压力和等离子体能量优化薄膜质量,例如ALD的自限性反应可实现超薄层厚控制9。

应用领域对比

| 技术方向 | 典型应用场景 |

|---|---|

| 半导体外延 | 先进逻辑芯片(FinFET)、功率器件(SiC/GaN)、量子通信器件 |

| 薄膜沉积 | 存储单元介电层、光学涂层、柔性电子器件、光伏电池电极 |

半导体外延专注于单晶材料的高质量生长,服务于高性能器件的核心结构;而薄膜沉积则侧重于功能层的多样化制备,适应复杂工艺需求。两者在材料科学和半导体制造中互补共存,共同推动技术进步。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

半导体

+关注

关注

335文章

29147浏览量

242166 -

薄膜

+关注

关注

0文章

317浏览量

36235 -

外延片

+关注

关注

0文章

37浏览量

9942

发布评论请先 登录

相关推荐

热点推荐

硅单晶(或多晶)薄膜的沉积

硅单晶(或多晶)薄膜的沉积

硅(Si)单晶薄膜是利用气相外延(VPE)技术,在一块单晶Si 衬底上沿其原来的结晶轴方向,生长一层导电类型

发表于 03-09 13:23

?9647次阅读

半导体设备行业跟踪报告:ALD技术进行薄膜沉积工艺优势

薄膜沉积是晶圆制造的三大核心步骤之- - ,薄膜的技术参数直接影响芯片性能。

半导体器件的不断缩小对薄膜

发表于 02-16 14:36

?1064次阅读

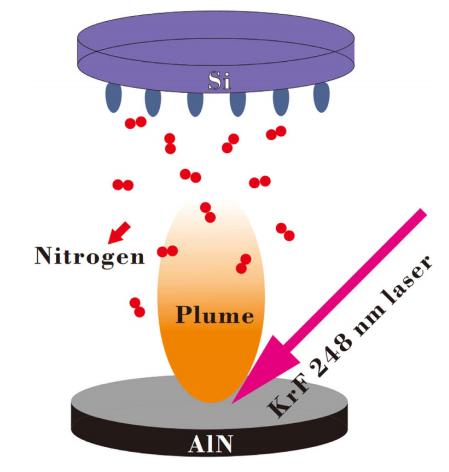

Si(111)衬底上脉冲激光沉积AlN外延薄膜的界面反应控制及其机理

通过有效控制AlN薄膜与Si衬底之间的界面反应,利用脉冲激光沉积(PLD)在Si衬底上生长高质量的AlN外延薄膜。英思特对PLD生长的AlN/Si异质界面的表面形貌、晶体质量和界面性能

中电化合物荣获“中国第三代半导体外延十强企业”

近日,华大半导体旗下中电化合物有限公司荣获“中国第三代半导体外延十强企业”称号,其生产的8英寸SiC外延片更是一举斩获“2023年度SiC衬底/外延最具影响力产品奖”。这一荣誉充分体现

半导体衬底和外延有什么区别?

衬底(substrate)是由半导体单晶材料制造而成的晶圆片,衬底可以直接进入晶圆制造环节生产半导体器件,也可以进行外延工艺加工生产外延片。

发表于 03-08 11:07

?2393次阅读

半导体薄膜沉积技术的优势和应用

在半导体制造业这一精密且日新月异的舞台上,每一项技术都是推动行业跃进的关键舞者。其中,原子层沉积(ALD)技术,作为薄膜沉积领域的一颗璀璨明星,正逐步成为

半导体外延工艺在哪个阶段进行的

半导体外延工艺主要在集成电路制造的前端工艺(FEOL)阶段进行。以下是具体说明:所属环节定位:作为核心步骤之一,外延属于前端制造流程中的关键环节,其目的是在单晶衬底上有序沉积单晶材料以形成外延

半导体外延和薄膜沉积有什么不同

半导体外延和薄膜沉积有什么不同

评论