上篇和中篇,我们介绍了FPGA的四大特点,以及这些特点所带来的市场和应用机会,概述如下:

高集成度:工业机器人,激光雷达等;

有那么多的机会,FPGA怎么不上天呢?其实FPGA真上天了,在每一台火星车上,几乎都有宇航级FPGA存在,但不卖国内。即使上天也解决不了根本问题,火星车就那么几台,而芯片的持续健康发展必须要有用量的支撑。做芯片无法持续盈利并投入,便没有生命力,这就是搞“两弹一星”和搞芯片的本质区别。在本篇内容中,让我们说说FPGA的五大硬伤,搞清楚是什么限制了FPGA的海量部署和做大做强。

>> FPGA五大硬伤及破局之道

硬伤一:单价高,HardCopy的悲歌

有时候客户想谈价格,会说他们那个产品是海量。而我喜欢跟客户开玩笑说,“我们喜欢量大的应用,但是量也不能太大,否则我们会被吓跑。” 这是一句玩笑,但的确是FPGA的无奈。为什么?成本,还是成本。FPGA的可编程是用资源冗余实现的,同样功能的FPGA裸片尺寸(die size)是等效ASIC的几倍,甚至十几倍。冗余会带来成本,成本最后需要用户买单。

最终,等产品规格趋于稳定,可编程不再是刚需,降本变成了对FPGA厂家的灵魂拷问。降价,降BOM,是客户的习惯动作。头部FPGA厂家的毛利通常在70%左右,对以高利润率而津津乐道的FPGA厂家来说,面对客户不停的压价是一个痛苦的过程。那有没有解决办法呢?

业界一直在探索这一问题的解决方案,在2001年Altera就首次推出了HardCopy解决方案。HardCopy是一种结构化的ASIC,简单说来,先用FPGA做前期设计和中小批量生产,等设计稳定不变了,就用一个硬化的芯片HardCopy来替代FPGA,可以实现管脚兼容,客户不需要做硬件的改动。这个硬化的芯片去掉了所有的冗余电路,把裸片(die)面积做小。看起来完美解决了客户前期设计需要频繁改动以及后期量产FPGA单价过高的问题。

这个方案其实对卖FPGA也是很有帮助的,一方面可以在设计前期稳住客户,吸引客户使用Altera的FPGA,在设计稳定之后,又可以防止客户自己投片ASIC留住量产设计,真是一箭双雕。当年Altera的CEO John也这么想的,他从LSI Logic过来,定制化ASIC是LSI的主业。他豪赌HardCopy,似乎不成功便成仁,可是HardCopy终归是一曲悲歌。当时Altera内部私下流传着一句笑话: “Hard Yes, Copy No!”。言下之意就是“这东西很难,也不是拷贝这么简单”。

那么HardCopy问题出在哪里呢?

第一,HardCopy结构限制,裸片尺寸不能大幅度降低,节省的成本有限;

第二,HardCopy流片成本也挺高,有NRE(工程费用),对客户是个负担;

第三,HardCopy一对多替换FPGA也有很大的验证风险;

第四,如果流片以后设计又发生更改,会非常麻烦,造成成本损失。

总的来说,ASIC的风险HardCopy一个都不少,但是收益却远没有ASIC那么诱人。HardCopy是个看起来很美,操作起来很要命的产品,失败是必然的。全国的HardCopy最多只做成了两三个,可以说失败的很彻底。赛灵思的EasyPath作为被动应对的方案,后来也跟着销声匿迹了。

Altera梦碎HardCopy,对HardCopy的过度投入,以至于在FPGA SOC和软件工具方面投入不足,无法让公司赶超对手更上一层楼,却慢慢被对手甩开,后来终于做出了出售Altera给Intel的决定。

硬伤二:资源少,性能低,功耗高

有人会说,FPGA的性能并不低,资源也有大规模的可选啊。资源和性能是个相对的概念,对很多高端的应用,单片FPGA的资源是不够的,需要很多颗拼起来一起验证,与ASIC相比其极限主频也不够,因为有很多冗余电路,漏电流明显,天生功耗就高。有时前期原型验证用FPGA,后期转ASIC可以做得更大,速度可以更快且功耗可以更低。

在很多手持设备应用场景,比如对讲机,手持测试仪,手持超声,玩具打印机等等设备,功耗非常关键,一个是散热效果,一个是电池续航,都很重要。即便不用电池供电,比如手持超声,功耗太大设备发烫,也会严重影响使用过程中的用户体验。

有些设计无论怎么做功耗优化,始终无法满足需求,于是被迫弃用FPGA,或者改用其他ARM SOC加个非常小的低功耗FPGA。虽然Lattice和Microchip都有低功耗的工艺,但却牺牲了性能。而后来的易灵思,通过XLR(可变换逻辑和走线)架构创新兼顾了低功耗和高性能,并保持较低成本。这些尝试都很有意义,但是FPGA的结构本身决定了只能在一定程度上优化功耗、性能和资源利用率。我们仍然期待FPGA厂家在这些领域持续创新。

硬伤三:FPGA白纸一张,生态弱

FPGA号称万金油,什么都可以做。但是如果没有算法和协议实现,白纸一张,没有实际功能,实际上也什么都做不了。实现任何功能都需要进行编程,需要客户自己设计或者找合作方深度定制,但这条路充满荆棘。

很多时候,特别是一些做消费类产品比如全景相机、VR/AR这些应用的客户,产品定义突然提出需求来,规格也时常变化,内部没人做,外部IDH(独立设计工作室)也很难配合。很多中小公司不愿意养人,因为不会一直有FPGA的活干,而单独做IDH的公司也时常处于打零工的状态,饱一顿饥一顿,无法实现长期发展,各有各的难处。

对我们来说,也对没有常备FPGA设计能力的客户来说,IDH显得非常珍贵,他们都是我们的座上宾。但很多IDH生活在温饱线边缘,无论是转产品设计或是坚守IDH都是一条艰苦的路。所以,请善待IDH,珍惜IDH。

我们在做客户的早期设计导入的时候,为什么只倾向于报价给设计方,而不是单纯的采购方。这是因为,任何FPGA的量产,都需要经过设计者的辛苦努力才会有结果。在任何客户询价的时候,我们都需要搞清楚设计的来源和去处才会报价。这对保护设计者,保护市场价格都非常重要。

硬伤四:设计层次低,难掌握

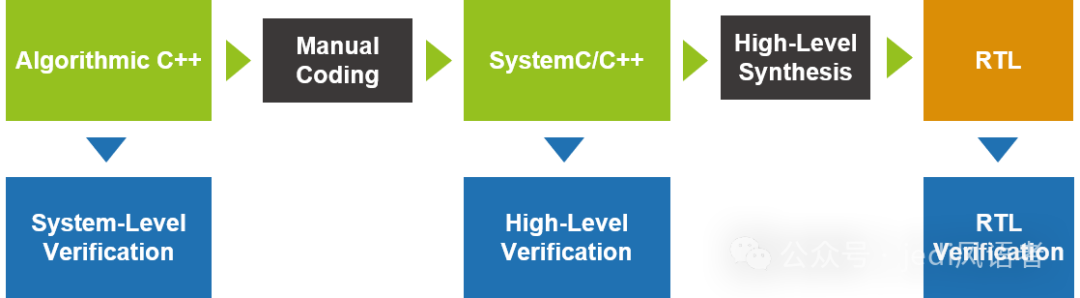

FPGA第一次市场规模的飞跃也是由设计方法学的飞跃引领的,也就是说,从原理图到HDL RTL层的设计革命极大提高了设计效率,第一次带飞了FPGA,把设计者从底层的原理图设计中解放出来,可以做更大更复杂的设计,然后由逻辑综合工具把HDL自动转成逻辑门网表,再布局布线。

「High-Level Synthesis/HLS并不普及」

然而,方法学就此几乎停滞不前,编程抽象层次仿佛被锁死在RTL层。RTL层犹如半自动化手工作坊,高级语言和高层次综合HLS始终无法大规模普及,无法带来设计生产力的革命性提升。不能大幅提升设计效率,极大限制了用户对资源或算力需求的拉动。

FPGA应用场景往往与底层硬件系统紧密结合,需要设计者对具体的硬件系统和应用需求有深入了解。同时,相比高级语言的软件设计,RTL设计方法比较难掌握,设计更改迭代慢,人难招。且对人的综合素质要求很高,包括软硬件,编程,算法,单板硬件都需要懂,难上加难。因此大家都会觉得FPGA圈子小,这并不是错觉。

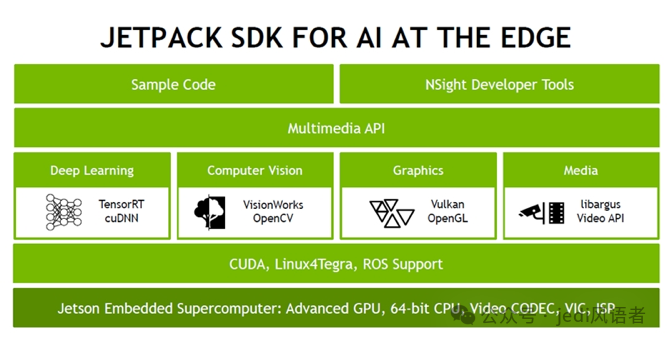

「Jetpack用于端侧AI开发」

再看看英伟达的GPU,不就是被CUDA带飞了吗。编程简单易学好用就是王道,高级语言直接上,资源效率和性能差不多就行,也没必要处处精益求精,通常能到标称算力的一半以上也不错了。如果需要对关键模块提高效率和性能,像DeepSeek那样,部分操作绕过CUDA的高层API,直接操作PTX指令集,也是可以的。现在的Jetson产品开发包Jetpack也是英伟达的护城河,它包含了完整的AI、计算机视觉、GPU加速、深度学习以及CUDA工具链,让开发者能够高效地在Jetson硬件上构建应用。

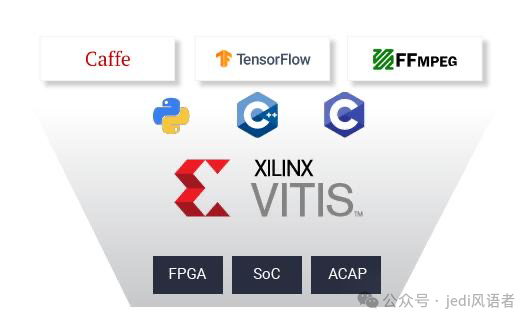

赛灵思“数据中心优先(DC First)战略”虎头蛇尾的一个重要原因,实际上就是FPGA设计方法学不具有普适性。公司高层也对这个问题洞若观火,做Vitis/Vitis AI工具的目的也是想让所有人都参与到FPGA平台的开发过程中来,不管是AI科学家,算法工程师,软件工程师都能轻松的对FPGA进行编程,使用C/C++,OpenCL库,亦或是TensorFlow,Pytorch等AI框架,希望能把FPGA编程彻底软件化。

但是,多数情况下,编程效果、硬件资源调用、资源使用效率和时序控制精度方面是个很大的问题。看起来高级编程语言和底层FPGA资源之间的鸿沟比想象的大很多,至今始终没有取得行业性的突破性进展。DC First出师未捷,原因与FaaS的逐渐衰落如出一辙。这一结果,导致了管理层考虑出售公司给AMD,使得盛极一时的XDF(赛灵思开发者大会)黯然落幕。

「Vitis有个美好的愿景」

硬伤五:芯片和工具迭代速度慢

在过去几年中,英伟达的边缘计算SOC从 Jetson TX2到Jetson Xavier再到Jetson Orin和Thor, 算力飞速提升,而FPGA的产品Portofolio基本没变,这样怎么竞争?!在主航道拼算力肯定是拼不过的,主流应用比较难竞争,那就只能偏安于小众应用了。

而且,最近几年整个FPGA行业的工艺领先性不再,产品更新迭代慢下来了,Altera和赛灵思芯片工艺也分别卡在10纳米(nm)和7纳米(nm)节点上多年。由于7nm产品推广不利,赛灵思目前在16nm产品上疯狂补课,甚至超过15年高龄也差点退休的45nm产品Spartan6,还在低端市场扮演重要角色。

前面也提过,一个重要原因就是FPGA这个行业的设计方法学停滞不前,被卡在RTL这个层级上了。有了先进的方法学,芯片资源就像韩信将兵多多益善,否则根本处理不了,芯片做得太大了只会是负担。逻辑综合与布局布线算法也多年没有革命性变化,最大的芯片每一次换代,相应的工具都需要努力做改进,否则做一次编译需要几天几夜,让人望而却步。

现在的英伟达,客户的算力需求一直迅速扩大,算力呈指数级增加,工具链并没有成为硬件的瓶颈,反而推动着技术一直向前。反观现在的FPGA,在大部分场合,感觉性能已然过剩。目前整个芯片行业资源向AI和GPU严重倾斜,必然在其他芯片品类投资减少,这也会影响FPGA的创新步伐。

四面楚歌,如何破局?

当年FPGA刚刚开始繁荣的时候,像极了一位朝气蓬勃的年轻人,到处挤占市场,把手伸向MCU, CPU, DSP, ASSP的传统领地。时过境迁,经过20多年的高速发展,FPGA年过不惑,动作也慢下来了。竞争对手却在不断迭代,GPU和集成NPU的SOC也开始蚕食FPGA的市场。逆水行舟,不进则退,FPGA会掉队吗,未来路在何方?

前赛灵思CEO Victor的大方向也许是对的,可能是着急了。或许资本也容不得他慢慢来吧,最后的最后就是卖公司能在短期内挣到更多的钱,财务目标肯定是达到了。功成身退,皆大欢喜。

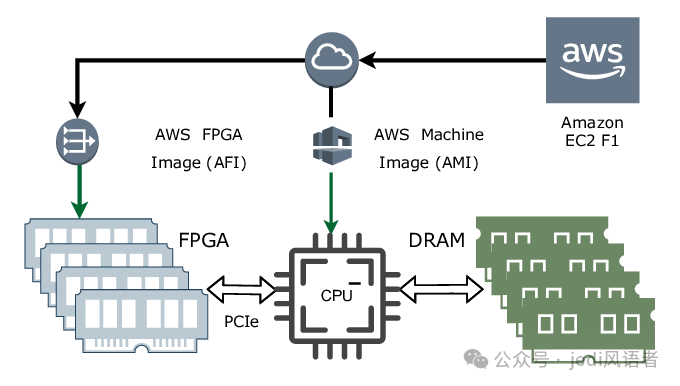

在AI浪潮下,数据中心云端AI推理、高性能计算、视频转码、数据分析等任务越来越多地使用通用GPU,而不是 FPGA。过去,云计算平台亚马逊AWS、微软Azure都使用FPGA加速,但现在通用GPU和客户定制的TPU/DPU已逐渐取代FPGA。

「AWS F1实例系统架构」

在边缘计算领域,GPU和带AI算力SOC也在计算机视觉,视频分析,信号处理(MIMO、波束成形、FFT计算等)领域开始侵蚀FPGA。比如,在超高端超声设备中,GPU正在取代传统的FPGA进行波束成形。AI 技术开始与超声成像结合,深度学习可以用于优化波束成形过程,进一步提高图像质量或减少噪声。而且,根本不需要什么专业的GPU,CUDA完全支持游戏GPU卡做计算加速,性价比非常好,也不要惊讶,很多客户都是这么做的。

国产带NPU的SOC芯片,逐渐侵蚀了L0/L1级辅助驾驶(ADAS),驾驶员监控系统(DMS),环视(Surround View)中FPGA SOC的份额。KVM市场中国产的SOC比如典型代表海思和RockChip,新产品不仅ARM处理器很强,AI算力足够,而且还内嵌了很强的Video Codec。在智能摄像头领域,几乎是海思, Rockchip, Amba等SOC的天下,FPGA毫无斩获。目前AI ISP也逐渐取得了更多关注,通常他们会跑在集成NPU的SOC中,而不是在FPGA上。当然这里说的都是AI推理方面,至于FPGA做接口转换等传统需求,倒是时常会有。

在自动驾驶领域,赛灵思Versal AI Edge的设计中标(Design Win)几乎可以忽略,公开消息就只有斯巴鲁的双目视觉EyeSight自驾系统。整个国内市场基本被英伟达Jetson Orin,地平线征程,华为MDC三家包了。尤其是Jetson系列,可以说是英伟达最具潜力的产品线,迅速引领市场,在自动驾驶,机器人,机器视觉等端侧AI领域变得越来越引人注目。

在端侧AI主赛道上,FPGA已然落后很多。

在工业控制,测试仪器仪表这样的应用中,TI, Rockchip, Allwinner等厂家的SOC产品迭代加快,体现更优性价比,对FPGA SOC虎视眈眈。一些前期FPGA的设计稳定量产以后,也面临着被ASIC替换的风险,比如无人机图传系统,光纤到屋FTTR中的mini-OLT部分,和车载激光雷达。

Altera在卖给Intel以后存在感逐渐降低,尽管风口将过,赛灵思也借机卖身成功,FPGA行业似乎陷入停滞,创新缓慢。反而由于数家国产FPGA厂家的卷入,在LED大屏和无线直放站等传统中低端市场厮杀惨烈。

然而天下大势,分分合合皆为常态。这时候Intel因为消化不良而让Altera单飞,也说明FPGA作为一个独立的品牌,具有相当的生命力,它不会是一个附属品,也不会淹没在星辰大海中最终销声匿迹。多听客户的意见,多做产品创新,把客户需求转化为实实在在的产品,做实客户基础,才是任何一家公司的未来。

FPGA行业应该从哪些方面突破呢?我觉得主要有如下几点:

第一,设计方法学革命

当有一天,C/C++和Python这样的高级语言能对FPGA自由有效的编程,不用再去学HDL,那么FPGA的潜力一定会被充分释放,市场规模和影响力会高几个数量级。这样,FPGA行业才会再次迎来革命性的时刻,真正实现当年Altera管理层的口号:Go to the Ocean。跳出小池塘,走向大海。

既然人类智慧这么多年没有解决这个问题,我想未来AI人工智能一定可以解决FPGA设计层次提升的问题,AI狂飙,我们有理由期待。

第二,集成度和工具链提升

毫无疑问,异构计算很有价值。作为一个异构计算平台,FPGA里面集成标量处理器(CPU),向量处理器(NPU,AIE,或Tensor Block),自适应引擎(FPGA逻辑)这些都是有用的。CPU可以是ARM, RISC-V或者x86也行。NPU种类就更多了,众多厂商各显神通。这些异构计算单元集成在一起,也不一定要在一个die上,也可以用小芯片(Chiplet)的方式做成多个die,把这些die封在一个封装里面。

但是,不管硬件多牛,集成多少CPU, NPU, 或别的计算单元,工具链易于使用绝对是重中之重,因为用户不想过多关心你的底层架构,只想使用编程语言对底层的计算资源方便的调用,并表现出良好的效率和性能。而且编译时间要短,综合布局布线工具也应该用AI加速来提高效率吧,应该有人研究这个方向。如今无论是赛灵思的Vitis/Vitis AI还是Intel的OpenVino/FPGA AI Suite都差强人意,更不用说其他FPGA厂家。

第三,架构和工艺的创新

用户对FPGA在资源、功能、性能、功耗、成本这些方面的要求是永无止境的,因此,需要在系统架构、工艺设计、工具实现有效性方面持续做巨大的创新,才能不停的满足用户的需求。记得当年90nm以下就被“砖家”认为是芯片的极限了,因为传统平面FET(场效应管)的漏电流已经大到无法忍受。

物理尺寸有极限,但创新无极限。过去业界的FinFET(鳍式场效应管), Chiplet(小芯片), NoC(片上网络), LUT6(6输入查找表), XLR Cell(可变换逻辑与走线单元), HyperFlex等这些创新,都可圈可点。作为创新载体的FPGA,唯有自身不断创新,才会生生不息。

第四,持续投资并优化生态

作为FPGA厂家,必须重视投资生态。该有的IP库必须有,可以自研开发,也可以出钱让合作伙伴开发。核心的IP和API是必须的,如果什么都是第三方收费版本,客户使用成本必然很高,支持不灵活,极大影响客户选用。外围一些难度很大但是使用场景较少的IP,可以联系第三方做porting,确保能支持本厂FPGA。

我们周围还有很多IDH方案商,尽量鼓励更多的IDH为FPGA做系统方案,做开发板,做SOM,做POC(概念验证),做客户定制。在合理的情况下多让利给IDH,让他们能够健康的运转下去。必须要团结一切可以团结的力量,把生态丰富起来,才可以让客户多起来。

全文结语

FPGA是个伟大的发明,让有想法的人可以快速且低起步成本做出原型,让硬件创新变得如同软件一样灵活方便,因此获得大学和研究机构的广泛采用,赋能了新技术的落地。

当一个新应用变为成熟且海量的应用时,FPGA又往往会悄然退出,好像一位“生而不有,为而不恃,功成则身退”的隐士。然而,过不了多久,他又会以另一种形态或另一种新应用突然出现在我们面前。

FPGA是一种很重要的技术,不要神化它,也不要把它黑化。无论在不在风口,它将一直在那儿自我新陈代谢,在可预见的将来,它不会消失,会一直发展。我觉得FPGA像水,水无常形却润物无声。老子说,水利万物而不争,故几于道。

全文结束,

2025年3月于深圳。

声明:本文内容全部来自业界资讯和个人理解,未涉及任何公司机密和客户信息,不代表任何公司立场,仅供大家交流参考。

-

FPGA

+关注

关注

1646文章

22096浏览量

620627 -

芯片

+关注

关注

460文章

52734浏览量

444019 -

AI

+关注

关注

88文章

35748浏览量

282376

发布评论请先 登录

AI狂飙, FPGA会掉队吗? (中)

AI狂飙, FPGA会掉队吗? (上)

让太阳能逆变器“狂飙”的秘诀-耐达讯CAN转EtherCAT网关

大家都在用什么AI软件?有没有好用的免费的AI软件推荐一下?

智多晶FPGA设计工具HqFpga接入DeepSeek大模型

马斯克回归“7×24硬核模式”,FSD与Optimus双线狂飙

大模型加持,利尔达全新星闪AI开发套件体验感继续“狂飙”

FPGA+AI王炸组合如何重塑未来世界:看看DeepSeek东方神秘力量如何预测......

当我问DeepSeek AI爆发时代的FPGA是否重要?答案是......

FPGA在AI方面有哪些应用

基于Achronix Speedster7t FPGA器件的AI基准测试

AI狂飙, FPGA会掉队吗? (下)

AI狂飙, FPGA会掉队吗? (下)

评论