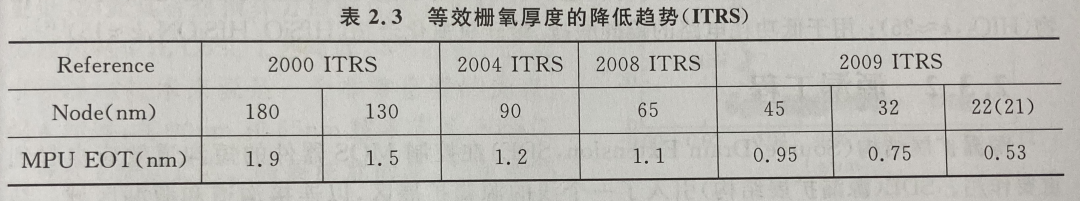

为了有效抑制短沟道效应,提高栅控能力,随着MOS结构的尺寸不断降低,就需要相对应的提高栅电极电容。提高电容的一个办法是通过降低栅氧化层的厚度来达到这一目的。栅氧厚度必须随着沟道长度的降低而近似地线性降低,从而获得足够的栅控能力以确保良好的短沟道行为。另外,随着栅氧厚度的降低,MOS 器件的驱动电流将获得提升。由表2.3可见不同技术节点下对栅氧厚度的要求。

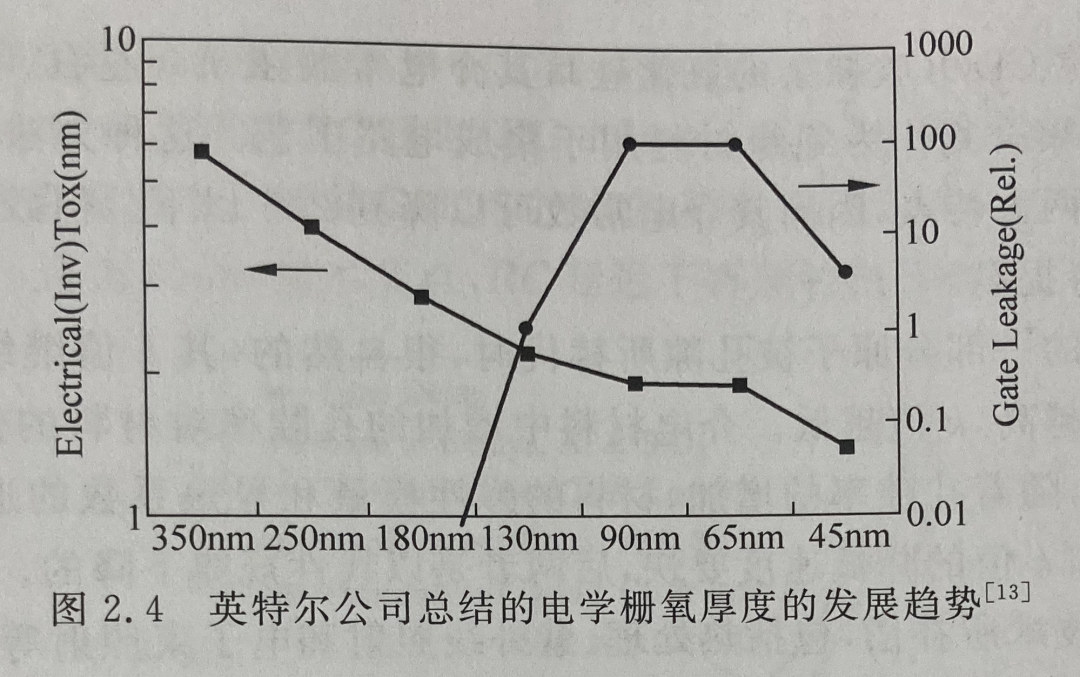

从20世纪70年代第一次被引入集成电路工业中,二氧化硅一直作为硅基MOS管的栅介电材料。然而,不断降低的二氧化硅的厚度会导致隧穿漏电流的指数提升,功耗增加,而且器件的可靠性问题更为突出;氧化层陷阱和界面陷阱会引起显著的界面散射和库伦散射等,降低载流子迁移率;硼穿通问题则影响 PMOSFET 阈值电压的稳定性;此外,薄栅氧带来的强场效应会导致明显的反型层量子化和迁移率退化以及隧穿电流后。图2.4为英特尔公司总结的栅氧厚度的降低趋势。

从图2.4可见,在0.13μm 工艺节点之前,栅氧厚度一般降低到上一工艺节点的0.7倍左右。到 90nm阶段,栅氧厚度的降低变得缓慢,这是为了避免栅极漏电流(gate leakage)的急剧增大。而从 90nm 技术节点到65nm 技术节点,栅氧的厚度基本没有改变,也是出于同样的原因。然后,在45nm 技术节点,奇异的是,其电学栅氧厚度继续降低,同时栅极漏电流也显著减小。这是为什么呢?

提高电容的另外一个办法是提高介电层的介电常数,这样就可以提高栅介质材料的物理厚度,以限制栅极漏电流,同时其有效栅氧厚度(EOT)能够做到很薄,以对 FET通道有足够的控制、维持或提高性能。在 45nm 之前,工业界通过将栅氧化层部分氮化,以提高栅极电容,并降低漏电流。氮化硅跟已有的工艺比较兼容,但是其k值提高的幅度有限。而当尺寸需要进一步降低时候,就需要引入高k栅介电材料。

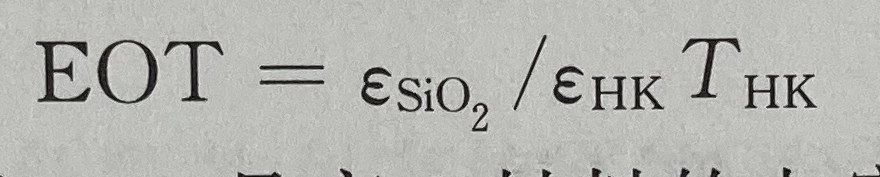

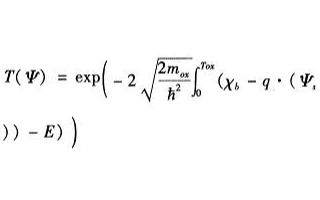

高k介电材料的物理厚度和其EOT 之间的关系如下

上式中,THK是高k材料的物理厚度,εHK 是高k材料的电容率,它与介电常数k呈正比关系。由于εHk 远远大于εSiO2,在降低 EOT 的同时,高k材料的物理厚度获得大幅度提升。英特尔公司的45nm 技术已经采用该技术,并已经进入量产阶段。

高k材料的选择,需要综合考虑介电常数和漏电的要求。高k介质在硅上必须具有热动力稳定性,它们必须具有最小的高k/Si界面态,并为NMOS和PMOS 器件提供专门的功函数。为实现批量生产,还必须满足动态要求和刻蚀选择性标准。综上所述,以元素铪为基础的介电层材料成为首选。给的系列材料包括:可以用于微处理器等高性能电路的铪氧化物(HfO2,k~25);用于低功耗电路的铪硅酸盐/铪硅氧氮化合物(HfSiO/HfSiON,k~15)。

-

集成电路

+关注

关注

5430文章

12160浏览量

369149 -

电容

+关注

关注

100文章

6280浏览量

154851 -

MOS

+关注

关注

32文章

1368浏览量

97459

原文标题:等效栅氧厚度的微缩

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

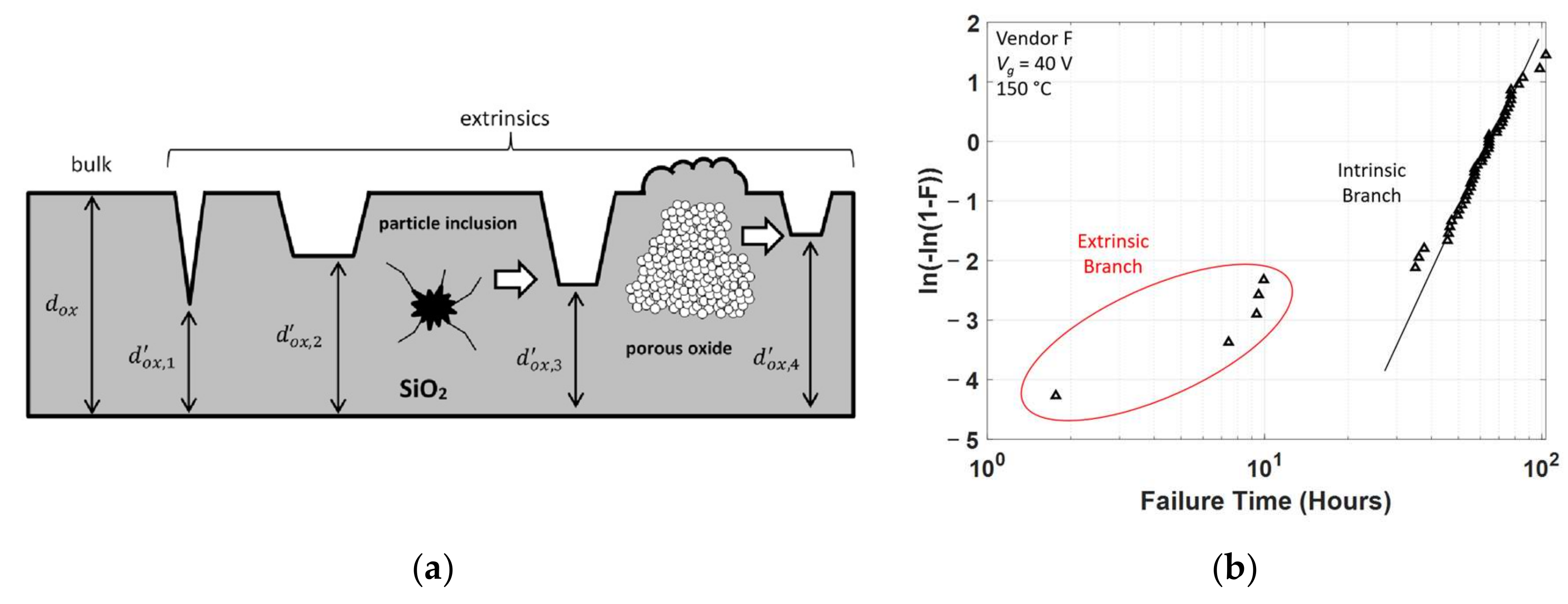

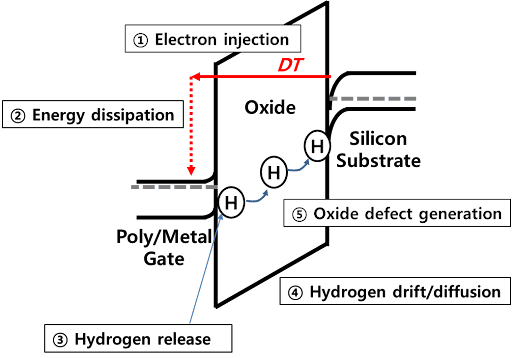

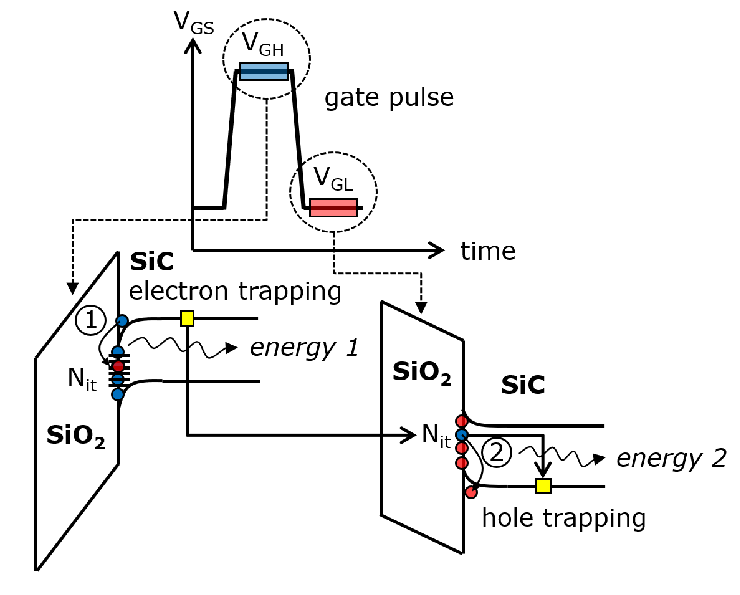

3300V SiC MOSFET栅氧可靠性研究

未来推动芯片尺寸微缩的五种技术

MOSFET栅漏电流噪声特性、模型的特性和局限性研究分析

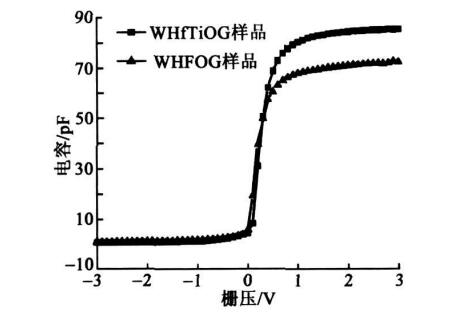

一文读懂HfTiO高栅介质GeMOS电容

AEC---SiC MOSFET 高温栅氧可靠性研究

vdmos器件厚度对电阻的影响

集成电路制造工艺中的伪栅去除技术介绍

碳化硅(SiC)MOSFET的栅氧可靠性成为电力电子客户应用中的核心关切点

做贼心虚:部分国产碳化硅MOSFET厂商“避谈栅氧可靠性”的本质

国产SiC碳化硅MOSFET厂商绝口不提栅氧可靠性的根本原因是什么

车载充电机(OBC)和热泵空调等车载领域成为栅氧可靠性问题的“爆雷重灾区”

等效栅氧厚度的微缩

等效栅氧厚度的微缩

评论