概述

具有隐含时钟的DS1251 4096k NV SRAM为全静态非易失RAM (按照8位、512k字排列),内置实时时钟。DS1251Y自带锂电池及控制电路,控制电路连续监视VCC是否超出容差范围,一旦超出容差,锂电池便自动切换至供电状态,写保护将无条件使能、以防存储器和实时时钟数据被破坏。

隐含时钟提供百分之一秒、秒、分、时、星期、日、月、年等时间信息。对少于31天的月份,月终日期可自动调节,包括对闰年的修正。隐含时钟格式可配置为24小时制或配合AM/PM指示的12小时制。

数据表:*附件:DS1251 4096k NV SRAM,带有隐含时钟技术手册.pdf

特性

- 实时时钟保持跟踪百分之一秒、秒、分、时、星期、日、月和年

- 512k x 8 NV SRAM可直接替代易失静态RAM或EEPROM

- 内置锂电池维持日历运行及保存RAM数据

- 时钟功能对RAM操作完全透明

- 月和年决定每个月的天数,有效期至2100年

- 无外部电源时可保存数据10年以上

- 10%工作范围

- 第一次上电前,锂电池与电路断开、维持保鲜状态

- 提供DIP模块

- 标准32引脚JEDEC引脚排列

- 与DS1248引脚兼容

- PowerCap模板

- 表面贴装可直接与带有电池和晶振的PowerCap连接

- 电池可更换(PowerCap)

- 与其它存储容量的DS124xP隐含时钟引脚兼容

- 提供无引线封装

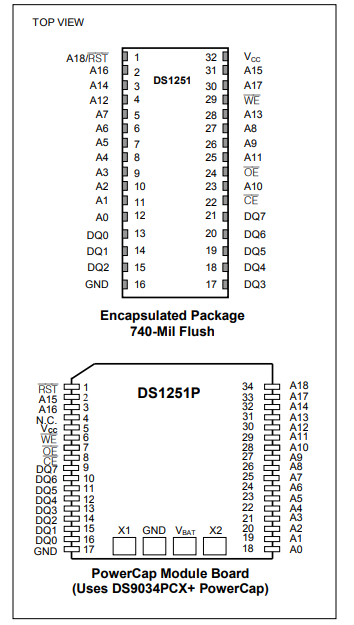

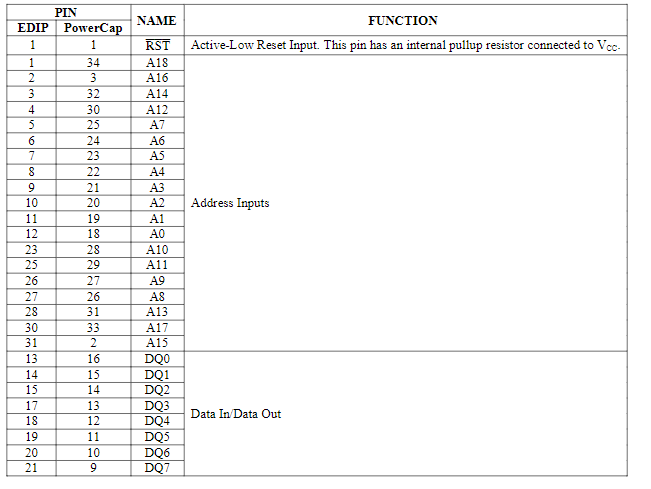

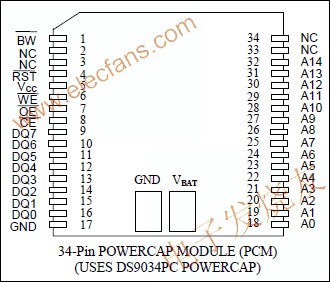

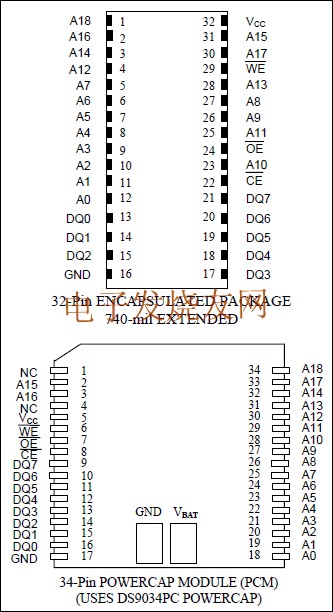

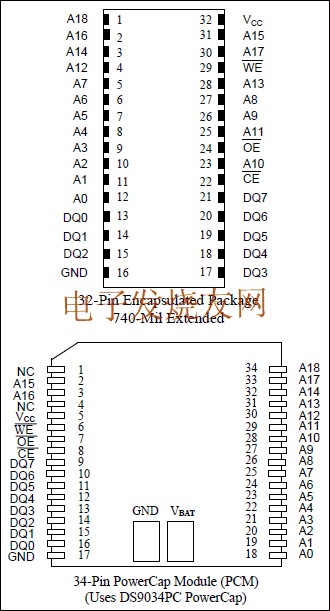

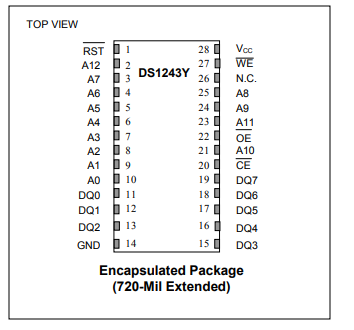

引脚配置

包装

DS1251有两种封装:32针DIP和34针PowerCap模块。32针DIP式模块将晶体、锂能源和硅集成在一个封装中。34针PowerCap模块板设计有触点,用于连接到包含晶体和电池的单独PowerCap(DS9034PCX)。这种设计允许在表面安装过程完成后将PowerCap安装在DS1251P的顶部。在表面安装过程后安装PowerCap可以防止因回流焊所需的高温而损坏晶体和电池。PowerCap采用键控设计,可防止反向插入。PowerCap模块板和PowerCap单独订购,并装在单独的容器中运输。

幻影时钟操作

与幻影时钟的通信是通过对64位串行比特流进行模式识别来建立的,必须通过执行包含DQ0上正确数据的64个连续写入周期来匹配。在识别64位模式之前发生的所有访间都指向内存。在识别建立后,接下来的64个读取或写入周期提取或更新幻影时钟中的数据,并禁止存储器访间。

在芯片启用、输出启用和写入启用的控制下,通过串行比特流实现与计时功能的数据传输。最初,使用幻影时钟的CE和OE控制对任何存储位置的读取循环通过将指针移动到64位比较寄存器的第一位来启动模式识别序列。接下来,使用SmartWatch的cE和wE控制执行64个连续的写入周期。这64个写入周期仅用于访间幻影时钟。因此,套接字中内存的任何地址都是可以接受的。然而,为访间幻影时钟而生成的写入周期也在将数据写入配套RAM中的一个位置。管理这一要求的首选方法是在RAM中只留出一个地址位置作为幻影时钟暂存区。当执行第一写入周期时,将其与64位比较寄存器的位0进行比较。如果找到匹配,指针将递增到比较寄存器的下一个位置,并等待下一个写入周期。如果未找到匹配项,指针将不会前进,所有后续写入周期都将被忽略。如果在模式识别过程中的任何时候发生读取循环,则当前序列将中止,比较寄存器指针将重置。如上所述,模式识别持续了总共64个写入周期,直到比较寄存器中的所有位都匹配为止(图1)。正确匹配64位后,幻影时钟启用,数据传输到或

-

RAM

+关注

关注

8文章

1393浏览量

118015 -

实时时钟

+关注

关注

4文章

316浏览量

67226 -

DS1251

+关注

关注

0文章

3浏览量

7117

发布评论请先 登录

DS1350W 3.3V、4096k非易失SRAM

DS1345W 3.3V、1024k NV SRAM

DS1330 256k非易失(NV) SRAM

DS1250 4096k、非易失SRAM

DS1250W 3.3V 4096k全静态非易失SRAM

DS1251,DS1251P 4096k NV SRAM

DS1251 4096k NV SRAM,带有隐含时钟技术手册

DS1251 4096k NV SRAM,带有隐含时钟技术手册

评论