电子供应链中的所有利益相关者都依赖于他们买卖的复杂组件的可靠性。但随着芯片技术的进步,测试所有可能的质量问题变得更具挑战性。例如,苹果的A17 Pro SoC拥有190亿个晶体管和一个6核CPU,其中两个高性能内核采用了新的台积电3纳米技术。当组件直接销售或通过授权渠道销售时,半导体制造商保证其芯片的性能。

10纳米以下晶圆厂生产的新处理器出现了更多的质量问题——有些在常规测试中很难检测出来。制造商和原始设备制造商在最终用户投诉后才发现,不得不更换整个设备并推迟生产。

一些小故障仍然是个谜。2015年,一群来自多伦多大学的计算机科学家IEEE频谱报告超过4%的谷歌云计算服务器被之前任何测试都没有检测到的错误击中,导致服务器意外停止。

然后,在2020年,AMD发表了一份报告有证据表明,当时最先进的芯片比上一代同类产品的可靠性低5.5倍。越来越多的人一致认为,随着每一代半导体的出现,这个问题正在成倍增长,尤其是在最先进的芯片中。

2021年,脸书和谷歌的研究人员发表了描述计算机硬件故障的研究,这些故障的原因不容易确定。他们认为,问题不在于软件,而在于不同公司生产的计算机硬件的某个地方。

“我们的冒险始于警惕的制作团队越来越多地抱怨累犯机器破坏数据,”谷歌工程师彼得·霍奇斯尔德在一次视频已呈现在操作系统热点话题(Hot Topics in Operating Systems)2021大会上。

Hochschild和他的团队推测,“性能和密度正在超过硅的可靠性,复杂性正在超过测试方法。”

摩尔定律与功耗

1974年,美国工程师和发明家罗伯特·h·丹纳德与人合著了一部纸认为随着晶体管变得越来越小,它们的功率密度保持不变,因此功耗与面积成比例。

根据摩尔定律,晶体管数量每两年翻一番,芯片尺寸保持不变,而Dennard scaling则表示,给定面积的总芯片功率在不同代的工艺中保持不变。

英特尔、AMD、台积电和其他公司一直在利用这两条定律制造更快、更小的处理器,从而实现了当前的移动计算生态系统。当前的笔记本电脑、平板电脑,尤其是智能手机,之所以成为可能,是因为它们在相同的面积上封装了更多的晶体管,而同样的性能需要更少的功率。

不幸的是,对于半导体行业和原始设备制造商来说,Dennard scaling不再有效。“1974年,丹纳德的标度法则被发现,并一直保持了30多年,直到2005年左右,”克里斯蒂安·马丁教授说奥格斯堡应用科学大学的教授说:“在2005年之前,器件结构大于65纳米时,漏电流可以忽略不计。”

根据内存制造商Rambus的说法,“业界普遍认为,Dennard缩放定律在2005-2007年间的某个时候失效了。正如马丁所证实的那样,由于阈值和工作电压无法再调整,因此不可能在保持各代产品功率包络不变的同时实现潜在的性能提升。”

事实上,正如马丁所展示的那样,在相同的芯片面积下,后Dennard缩放导致每代功耗增加2倍,芯片计算资源的使用减少。对于给定的芯片面积,每一代的能效只能提高40%。

收益率下降;耗电量增加了

摩尔第二定律,也叫洛克定律(以亚瑟·洛克命名)指出半导体制造厂也会随着时间呈指数增长。

随着密度和复杂性的增加,生产可用芯片的成本增加。一些半导体制造商正花费数十亿美元购买新工具,尤其是阿斯麦***。

此外,由于Dennard扩展已经死亡,芯片设计人员必须创建更多的专用内核来补偿更高的功耗。这对于云计算和人工智能应用尤其重要,在这些应用中,电源使用效率(PUE)是效率和可持续性的最终衡量标准。

最近,华为推出了新的旗舰智能手机Mate 60 Pro,据报道,它包括由中国半导体制造国际公司(SMIC)明确开发的新5G麒麟9000s处理器。最初,华为没有发布这款设备的全部规格,但是拆卸显示其采用7纳米技术。直到最近,人们还认为没有一家中国制造商拥有制造如此大规模芯片的工具。

“一些研究公司预测SMIC的7纳米工艺成品率低于50 %,与90%或更高的行业标准相比,低产量将限制出货量在200-400万片左右,不足以让华为恢复其以前在智能手机市场的主导地位,”路透社报道。

测试复杂的芯片需要新的工具

在对创新的不懈追求中,半导体行业已经达到了前所未有的里程碑,芯片使用5纳米和3纳米内核。然而,这种显著的进步也带来了令人担忧的副作用:芯片故障率不断上升。

在这种情况下,对前沿半导体进行全面、持续的可靠性测试的需求从未像现在这样明显。从过去的失败中吸取的教训,如谷歌、AMD、脸书和其他公司所强调的,强调了应对这些挑战的紧迫性。

审核编辑:黄飞

-

芯片

+关注

关注

460文章

52736浏览量

444119 -

摩尔定律

+关注

关注

4文章

640浏览量

80031 -

芯片设计

+关注

关注

15文章

1093浏览量

55770 -

晶体管

+关注

关注

77文章

10043浏览量

142591 -

半导体制造

+关注

关注

8文章

457浏览量

24981

发布评论请先 登录

可靠性设计的十个重点

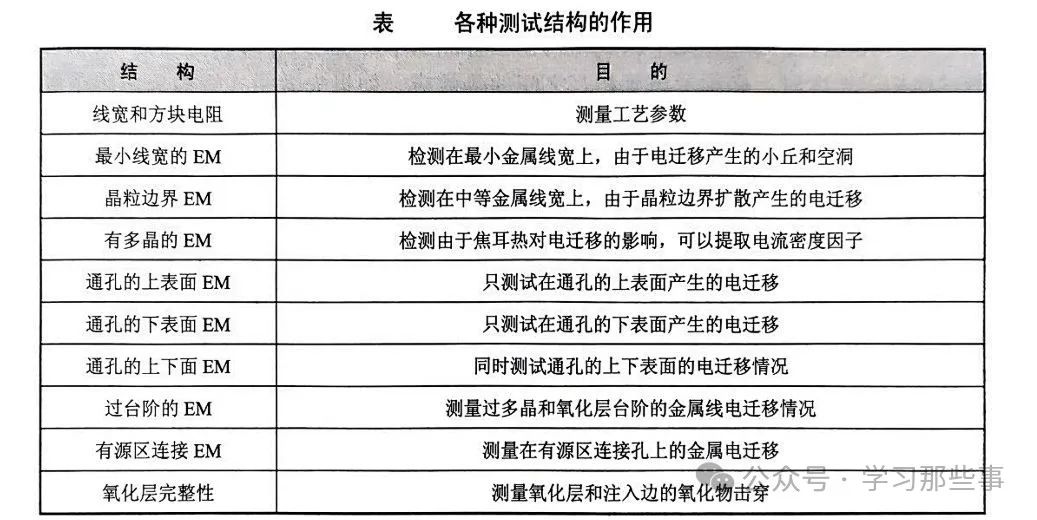

提供半导体工艺可靠性测试-WLR晶圆可靠性测试

电机微机控制系统可靠性分析

非易失性存储器芯片的可靠性测试要求

电路可靠性设计与工程计算技能概述

详解晶圆级可靠性评价技术

芯片可靠性测试:性能的关键

PCB高可靠性化要求与发展——PCB高可靠性的影响因素(上)

浅谈芯片技术的可靠性风险

浅谈芯片技术的可靠性风险

评论