什么是Setup和Hold时间?

Setup和Hold时间是数字电路中一种时序要求,用于确保稳定的数据传输和正确的电路操作。

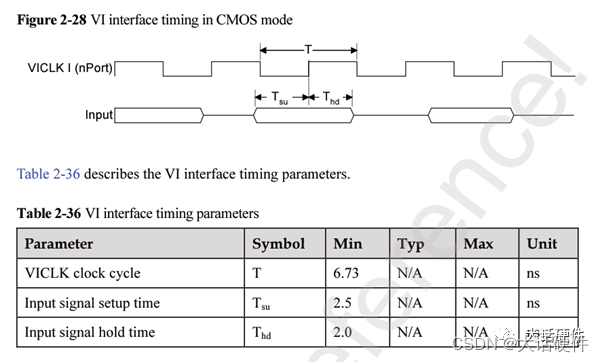

在数字电路中,数据的传输需要遵循一定的时间要求。Setup时间指的是在时钟的上升沿之前,输入信号需要稳定在有效的数据值上的最小时间间隔。Hold时间指的是在时钟的上升沿之后,输入信号需要保持在有效的数据值上的最小时间间隔。这两个时间要求是保证数据在电路中的正确传输和处理的关键。

首先,让我们更深入地了解一下Setup时间。在数字电路中,时钟信号被用于同步电路的操作。当时钟上升沿到来时,电路通常会在其上沿完成一系列操作,特别是将输入数据发送到输出端口或者进行逻辑运算。然而,由于电路的延迟,输入信号往往会在时钟上升沿之前发生变化。如果在时钟的上升沿到来之前,输入信号没有稳定在有效值上,那么电路将无法正确定义输出。因此,为了确保正确的数据传输,需要保证输入信号在设定时钟上升沿前稳定在有效值上的最小时间间隔,这个时间就是Setup时间。

接下来,让我们来研究一下Hold时间。类似于Setup时间,Hold时间也是为了确保正确的数据传输。当时钟上升沿到来时,电路会根据输入信号进行一系列操作,然后将结果发送到输出端口。然而,由于电路的延迟,输出结果可能不会立即稳定下来。如果在时钟的上升沿之后,输出信号没有保持在有效值上,那么后续的电路操作可能会受到影响,导致数据传输出错。因此,为了确保正确的数据传输,需要保证输出信号在设定时钟上升沿后保持在有效值上的最小时间间隔,这个时间就是Hold时间。

Setup和Hold时间的要求是由电路设计人员根据电路的特性和所使用的技术来确定的。这些时间要求需要满足芯片制造商的规范,以确保芯片的正常工作。在设计电路时,设计人员需要仔细地分析每个组件的延迟特性,以确定合适的Setup和Hold时间。通常情况下,芯片制造商会提供一些默认值和建议,但最终的确定仍然需要由设计人员来做出。

在实际应用中,如果不满足Setup和Hold时间的要求,可能会导致电路功能失效、数据错误或者芯片损坏。因此,确保电路满足这些时序要求对于数字系统的正确运行至关重要。

为了满足Setup和Hold时间的要求,设计人员可以采取一系列措施。首先,他们可以通过适当的选择时钟频率来放宽Setup和Hold时间的要求。降低时钟频率意味着更长的时间间隔,这样可以更容易满足时序要求。其次,他们可以使用更快的电路元件或者优化电路布局来减少电路的延迟。此外,他们还可以使用时序分析工具来模拟和验证电路的时序要求,以确保电路满足设定要求。

综上所述,Setup和Hold时间是数字电路中用于确保稳定数据传输和正确电路操作的关键时序要求。这些时间要求需要由电路设计人员根据电路特性和制造要求来确定。设计人员可以通过选择适当的时钟频率、优化电路元件和布局以及使用时序分析工具等措施来满足这些要求。对于数字系统的正确运行来说,满足Setup和Hold时间的要求至关重要。

-

芯片制造

+关注

关注

11文章

699浏览量

29890 -

数字电路

+关注

关注

193文章

1641浏览量

82152 -

Setup

+关注

关注

0文章

30浏览量

12267

发布评论请先 登录

什么是Setup和Hold时间?

什么是Setup和Hold时间?

评论