关键要点

为什么IC设计需要从两个不同的方向入手。

了解准备IC设计文件的过程。

成本和收益问题限制了IC的物理设计。

密集晶体管数硅晶片始于一系列IC设计步骤。

尽管晶体管的推出相对较晚,但它是人类历史上生产最多的产品。除非出现完全不可预见的技术突破,否则这种情况不太可能改变;自推出以来的几十年里,器件晶体管的数量呈指数级增长,而小型化制造奇迹是数字革命的核心。然而,晶体管数量增加的趋势正在突破设计和制造工艺的极限。IC设计构建了一个迭代过程,将对细节的关注与对设备特性和功能的高层次、系统的包含结合起来。

迭代和双向设计动机

IC设计步骤类似于PCB设计,但由于更多的约束和更严格的公差而产生差异。超大规模集成电路(VLSI)指导IC设计,将数十亿MOSFET组合到一个芯片中,实现密集的电子功能,如片上系统(SoC)。与PCB设计类似,VLSI设计流程是一个迭代过程,但需要注意的是,物理制造过程中的迭代比小批量原型要昂贵得多。而且,与PCB设计不同的是芯片在制造后缺乏用户可维护性——它是一种二进制的,不是成功就是失败。

IC设计的迭代性质源于自上而下和自下而上的设计风格的组合:

自上而下的设计是逆向工程意义上的分解。设计团队制定好的系统框架,然后在设计过程中为子系统添加细节。

自下而上的设计是先构建子系统,然后再将各个子系统合并到系统中。

虽然大部分IC设计侧重于自下而上的方法,因为它允许最精细的细节来塑造更高水平的设计复杂性,但自上而下的方法可以帮助利用自下而上的设计来改善性能结果。例如,尺寸是IC的两个主要设计约束之一,在没有准确估计芯片面积的情况下实施自上而下的架构设计可能会超出分配的空间。相反,IC设计应尽早集成物理约束,以构建具有互补特性的器件功能。最好的设计综合了自下而上的复杂性和对自上而下方法的约束:

概念设计-IC的规格。与所有工程一样,IC特性将有合理的权衡,以符合设计意图。然而,IC布局将允许在这些限制范围内有很大的自由度,允许设计者选择最合适的拓扑结构和布局

原理图设计和仿真 -IC的组件需要互连定义。网表必须完整描述与电源、接地和外部 I/O 引脚的连接。为了正确实现原理图,设计团队必须创建表示元件分组的符号,称为电路模块。除了布局之外,这些模块也是设计仿真阶段不可或缺的一部分。仿真阶段是有双重意义的:设计验证和优化性能。

布局和验证 -布局可以增强或抑制关键性能,主要是IC的功率、尺寸和运行速度。此外,精心的布局会抵消寄生电阻和电容的影响。然后,布局将使用可配置的DFM约束执行设计规则检查(DRC),以检测设计的IC与制造要求之间的冲突。

布局后仿真 -在确定布局和原理图之间不存在差异后,此阶段将是原理图级仿真的改进版本。它是一种更强大的仿真,可将寄生效应和信号延迟参数纳入评估中,从而准确模拟实际性能。仿真后的结果提供了有关布局的反馈,相关的设计规范可能需要进一步修订。

物理 IC 设计步骤的细节

完整的设计和制造的IC之间仍然存在着巨大的差距。制造工具和技术将要求遵守最小特征尺寸和间距规则。可制造性保证将取决于迭代和先前IC设计步骤的质量:

平面规划 -放置数十亿个单独的晶体管是不可行的;相反,晶体管被划分在功能模块中,然后递归地定义为更小的子块。平面图必须最好地将这些块分组,以最小化面积并方便布线。

布局-这个阶段涉及到块在芯片上的精确定位。第一个放置将是评估步骤之前的单元的粗略排列,旨在优化空间,同时遵守设计限制。对布线空间的估计可指导放置是否需要继续迭代。

第一次布局将是在评估步骤之前对单元进行粗略布置,评估步骤旨在优化空间,同时遵守设计要求限制。对布线空间的估计可指导布局是否需要继续迭代。

布线-块之间的空间为布线保留空间,布线过程跨越两个阶段。布线必须保留空间,并通过在引脚之间占用尽可能短的路径来最小化寄生效应的影响。首先,全局布线在金属层之间以交替的首选方向组织连接。详细布线如下,其中指定了这些连接的几何形状。

萃取-物理布局转化为网表,以实现包含精确细节的最精确仿真水平。必须对电气参数进行最终检查,以确定信号延迟和时序。

布线——块之间的空间为互连预留了空间,连接过程分为两个阶段。布线必须保留空间,并通过占据引脚之间尽可能短的距离来最小化寄生效应的影响。首先,全局布线以交替的优先方向在金属层之间组织连接。接下来是详细的布线,它指定了这些连接的几何形状。

导出-物理布局转化为网表,以进行最精确的仿真,其中包含精确的细节。为了建立信号延迟和时序,需要对电气参数进行最终检查。

使用Cadence解决方案逐步进行IC设计

IC设计步骤需要严格控制和精确度,以将密集的晶体管制造纳入现代封装中。然而,IC设计在概念上与PCB设计中的过程相差无几,这并不奇怪,因为IC实际上就是一块微型化的PCB。电路板或元器件需要复杂的工具集和最先进的建模,以不断实现设计突破的性能。

结论

Cadence Allegro PCB Designer是一个综合的PCB设计和分析工具,可涵盖设计流程的各个方面,包括原理图设计、布局、布线、分析等。这样可以大大提高工作效率,减少数据传递和转换过程中的错误和不一致性。

Cadence Allegro PCB Designer提供了一系列强大的分析工具,包括信号完整性分析、电源完整性分析、射频噪声分析等。这些工具可以帮助您识别和解决设计中可能存在的噪声问题,优化电路性能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

IC

+关注

关注

36文章

6154浏览量

180387 -

IC设计

+关注

关注

38文章

1362浏览量

106143 -

DFM

+关注

关注

8文章

477浏览量

29909

发布评论请先 登录

相关推荐

热点推荐

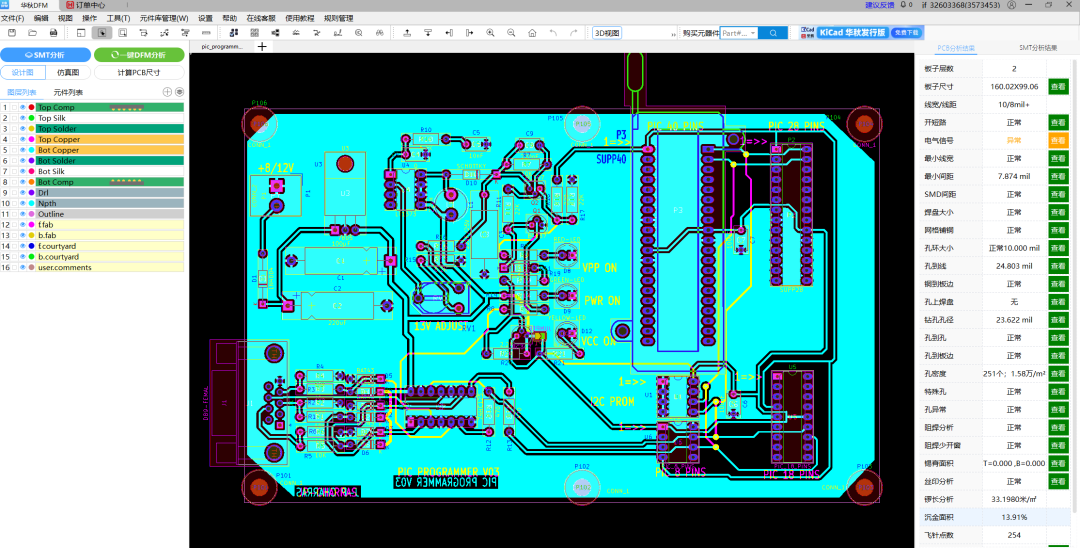

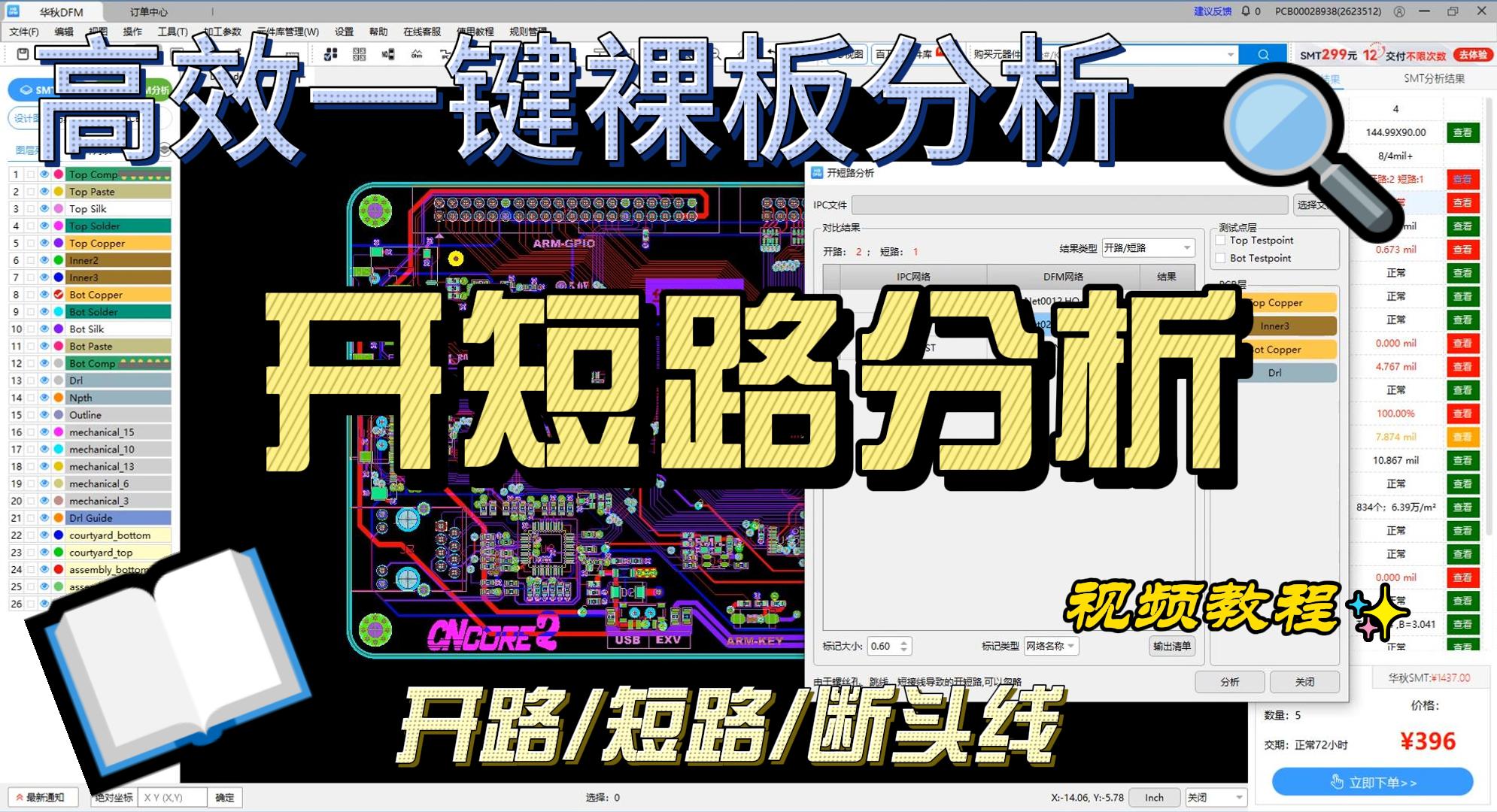

abg欧博DFM支持KiCad PCB了

“ ?新版的abg欧博 DFM 已支持打开源生的 KiCad PCB 文件。现在要进行裸板或 SMT 的 DFM 检查更方便了! ” ? 低调的看图神器 作为一个不怎么正经的电子工程师,我的电脑里常年安装

abg欧博DFM被杀毒软件报毒

卡巴斯基安全软件

用户类型: 活动用户

组件: 系统监控

结果说明: 已删除

类型: 木马

名称: PDM:Trojan.Win32.Generic

威胁级别: 高

对象类型: 进程

对象路径: d:\\\\program files\\\\hqdfm

对象名称: hqdfm

发表于 04-01 17:40

不懂DFM?设计隐患终成 “雷”!

问题轻则导致生产进度延迟,重则造成巨大的成本浪费。

二、工程师竞争力:DFM能力是职场 “护城河”

随着电子行业的发展,企业对PCB工程师的要求已经从单纯的 “能画板”提升到“懂制造” 。一名

发表于 02-25 15:53

MySQL还能跟上PostgreSQL的步伐吗

Can MySQL Catch Up with PostgreSQL’s Momentum?[2] 译者:冯若航[3],Vonng,Pigsty[4]?作者,PostgreSQL 大法师,数据库老司机,云计算泥石流。 MySQL还能跟上PostgreSQL的步伐吗

DFM在实际应用中的关键考虑和策略

一站式PCBA智造厂家今天为大家讲讲DFM对SMT贴片加工有什么影响?DFM对SMT贴片加工的重要性。在电子制造领域,SMT(Surface Mount Technology,表面贴装技术)贴片加工

abg欧博DFM软件再升级,热门功能抢先体验

在快速迭代的电子设计领域,每一处细节都可能成为决定产品成败的关键。

因此abg欧博DFM团队始终坚持不懈地 优化软件的服务、升级功能的应用 ,全面支持电子产品研发流程中的多元角色,尤其 聚焦于硬件

发表于 09-11 20:23

在 KiCad 中使用abg欧博 DFM 插件

“在 KiCad 中使用abg欧博DFM插件,高效完成工艺规则检查,且可以根据检测结果直接在 PCB 中进行修改。”

abg欧博 DFM 插件介绍

DFM 插件可以帮助您在 KiCad 的 PCB 中一

发表于 08-18 22:15

IC设计步骤:跟上现代DFM的步伐

IC设计步骤:跟上现代DFM的步伐

评论